Fターム[4M104GG08]の内容

Fターム[4M104GG08]の下位に属するFターム

Fターム[4M104GG08]に分類される特許

601 - 620 / 620

エッチング液及びエッチング方法

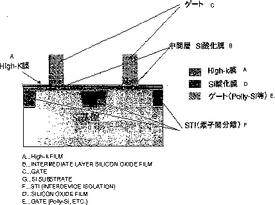

本発明は、比誘電率が8以上の膜(High−k膜)とシリコン酸化膜とが表面に形成されたものをエッチング処理するのに好適なエッチング液であって、High−k膜のエッチングレートが2Å/分以上であり、熱酸化膜(THOX)とHigh−k膜のエッチングレートの比が50以下であるものを提供する。前記エッチング液としては、フッ化水素(HF)と種々のエーテル系有機溶媒とを混合したものが好ましく使用される。  (もっと読む)

(もっと読む)

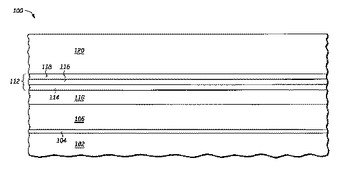

ドープ窒化膜、ドープ酸化膜、およびその他のドープ膜

【課題】一般に、半導体デバイスの製造に使用される被膜、特に窒化被膜および酸化被膜を提供すること。

【解決手段】窒化シリコン、酸化シリコン、酸窒化シリコン、または炭化シリコン被膜の形成中、少なくとも1つの非シリコン前駆体(ゲルマニウム前駆体や炭素前駆体など)を添加することによって、堆積速度が改善され、または被膜の応力を調整するなどこの被膜の特性を調整することが可能になり、あるいはその両方が可能になる。また、ドープ型酸化シリコンまたはドープ型窒化シリコンまたはその他のドープ型構造では、ドーパントが存在することを利用して、このドーパントに関連する信号(目印)をエッチング・ストップとして測定することができ、またはその他の場合にはエッチング中の制御を実現することができる。

(もっと読む)

集積回路およびその製造方法

【課題】 ポリマー系有機半導体材料を用いたp型FETを用いて実用的集積回路を構成できるようにすること。

【解決手段】 集積回路を構成するトランジスタとしてp型FETのみを用いたものである。基本回路の例として(a)インバーター回路、(b)AND回路、(c)OR回路を示す。同図において、1〜12はp型FETである。p型FETだけで構成し、出力部にもp型FETのみを用いたソースフォロワ回路を用いたアナログアンプも可能である。

(もっと読む)

High−k誘電材料をエッチングするための方法及びシステム

【課題】high−k(高誘電率)誘電材料をエッチングするための方法及びシステム

【解決手段】本発明のある実施形態では、エッチ反応剤が、high−k層と反応したときに揮発性エッチ製品を形成するために利用される。代わりに、high−k層はパターン化されたフォトレジストまたはハードマスクに従って異方エッチングすることができ、中性原子のハイパーサーマルビームがhigh−k層とのエッチ反応剤の反応を助けるために使用される。代わりに、中性原子のハイパーサーマルビームまたはプラズマ処理はhigh−k層を修正し、その後、該修正されたhigh−k層と反応するエッチ反応剤を活用して該修正されたhigh−k層をエッチングするために使用することができる。

(もっと読む)

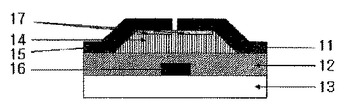

薄膜トランジスタ,その製造方法及び該薄膜トランジスタを備える平板ディスプレイ装置

【課題】 ソース/ドレイン電極間の電気的疎通を円滑にすることが可能な,薄膜トランジスタ,その製造方法及び該薄膜トランジスタを備える平板ディスプレイ装置を提供する。

【解決手段】 本発明に係る薄膜トランジスタは,基板110と,基板110上に形成されたゲート電極120と,ゲート電極120上に形成されるゲート絶縁層130と,ゲート電極120と絶縁されるようにゲート絶縁層130上に形成されるソース/ドレイン電極140a,140bと,ソース/ドレイン電極140a,140bと接するとともに,ゲート電極120と絶縁される有機半導体層150と,を含み,ソース/ドレイン電極140a,140bの少なくとも有機半導体層150と接する部分には酸化部140´a,140´bが設けられ,酸化部140´a,140´bを構成する物質は,有機半導体層150のHOMOエネルギー準位より大きい仕事関数を有する物質を含む。

(もっと読む)

半導体パターン形成方法

【課題】 半導体パターン形成方法を提供する。

【解決手段】 この方法は無機ハードマスク膜、有機マスク膜、反射防止膜及びシリコン含有フォトレジスト膜が積層された多層のマスク層を形成し、O2プラズマで前記反射防止膜及び有機マスク膜を乾式エッチングしてパターンを形成することによって無機ハードマスク膜の損傷を防止することができる。

(もっと読む)

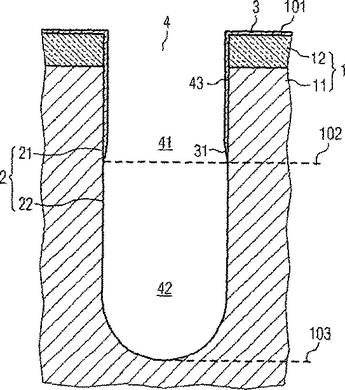

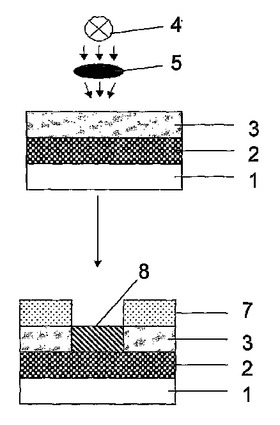

インコンフォーマルな堆積を用いて半導体プロセス技術において基板を垂直にパターニングする方法

典型的には半導体ウェーハである基板(1)の、レリーフ状にパターニングされた基板表面(101)上に、堆積方法(ADL;atomic layer deposition:原子層堆積)を用いて、基板表面(101)に対して傾斜し、および/または垂直である処理表面(2)に、被覆層(3)が提供される。被覆層(3)は、前駆材料の少なくとも1つの処理量の制限によって、および/または堆積方法の時間的制限によって、簡易な方法において、基板表面(101)に対して垂直な方向にパターニングされ、後続のプロセス工程のための機能層あるいはマスクとして形成される。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能や信頼性を向上させる。

【解決手段】 CMISFETを有する半導体装置において、nチャネル型MISFET30aのゲート電極31aは、P、AsまたはSbをドープしたシリコン膜をNi膜と反応させることで形成されたニッケルシリサイド膜からなり、pチャネル型MISFET30bのゲート電極31bは、ノンドープのシリコンゲルマニウム膜をNi膜と反応させることで形成されたニッケルシリコンゲルマニウム膜からなる。ゲート電極31aの仕事関数はP、AsまたはSbをドープすることによって制御され、ゲート電極31bの仕事関数はGe濃度を調節することによって制御される。

(もっと読む)

金属ゲート集積化のためのゲートスタック及びゲートスタックのエッチングシーケンス

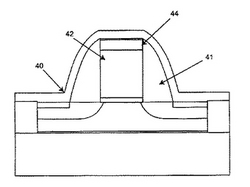

【課題】本発明は半導体デバイス(205)における金属ゲートスタック(200)を製作するためのプロセスを提供する。

【解決手段】本願の方法は、半導体基板(220)上に位置するゲート誘電体層(215)の上に金属層(210)を堆積させる段階を含む。本方法は、金属層(210)上にポリシリコン層(225)を形成する段階と、そのポリシリコン層(225)上に保護層(230)を生成する段階とを更に含む。本方法はは、また、保護層(230)上に無機反射防止被覆(235)を配置する段階を含む。他の実施形態では、金属ゲートスタックの前駆構造体及び集積回路の製造方法を含む。

(もっと読む)

分離相補型マスクパターン転写方法

パターニング方法は、相補的なレチクルの組を個別に転写することを可能にする。一実施形態においては、例えば本方法では、位相シフトマスク(PSM)(112)をエッチングし、次にcPSMマスク(110)に対応するカットマスクをエッチングする。更に、分離相補型マスクパターン転写方法は2つの個別の、かつ分離されたマスクパターニング工程を含み、これらの工程では、像を最終ウェハパターニングの前に、複合パターンを、中間ハードマスク(112)に部分的に転写することにより形成する。中間ハードマスク材料(112)及び最終ハードマスク材料(110)は、像が最終エッチングプロセスの前に下層の基板(102)またはウェハに像が転写されることがないように選択される。  (もっと読む)

(もっと読む)

カーボンナノチューブと金属炭酸塩とを具備する複合材料

本発明は、カーボンナノチューブ複合材料、それの生成の方法、そして、そのような複合材料の使用に関する。  (もっと読む)

(もっと読む)

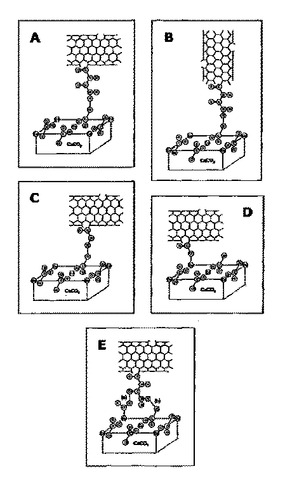

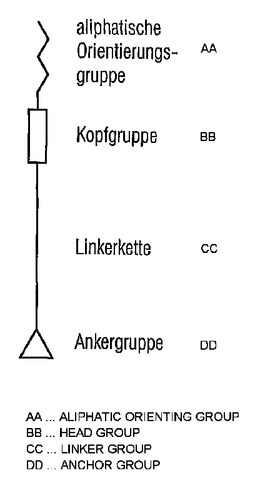

超薄膜誘電体、および、有機電界効果トランジスタでの超薄膜誘電体の使用

本発明は、基板、ソース電極、ドレイン電極、ゲート電極、および有機半導体材料を含む有機電界効果トランジスタに関するものである。このとき、誘電体層(ゲート誘電体)が、ゲート電極と半導体材料との間に配置されている。上記誘電体層は、アンカー基、リンカー基、頭部基、および脂肪族基を含んだ有機化合物の自己組織化単分子層からなる。アンカー基、リンカー基、頭部基、および脂肪族基は、この順にて互いに結合されている。  (もっと読む)

(もっと読む)

多機能ドープ導電性ポリマー系電界効果デバイス

電界駆動デバイス及び作動方法が提供される。各デバイスは、印加電界に対して多機能の応答を提供するために、一種以上のドープ導電性ポリマーを使用している。デバイスは、デバイス(10)用のゲートコンタクト(22)を提供するように作動できる導電層(30)と、デバイス(10)用のソース(24)及びドレイン(26)コンタクト並びに活性層を提供するように作動できる導電性ポリマー層(14)と、導電層(12)と導電性ポリマー層(14)との間に形成された絶縁性ポリマー層(16)とを有し、前記層の組合わせにより、複数の応答機能の内の少なくとも2機能を行うようにデバイス(10)が作動できる。 (もっと読む)

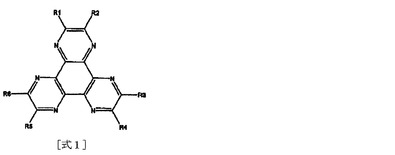

有機薄膜トランジスタ

本発明は、有機物層を有する有機トランジスタが提供される。本発明の前記有機物層は、下記式1で表される化合物のうち少なくともいずれか1種を含む。

(もっと読む)

(もっと読む)

金属被着

レーザによりパターン化された基板上に金属を無電解メッキする方法。基板上に熱画像形成層および触媒層がともに被着される。レーザ・ビームで露光すると、熱画像形成層において十分なレベルの放射が熱に変換され、それによって、隣接する触媒層の露光領域が不活性になる。次いで、レーザによりパターン化された基板を反応溶液に暴露し、それによって、触媒層の非露光領域上で金属被膜の成長が開始される。  (もっと読む)

(もっと読む)

III族窒化物素子の不動態化およびその方法

【課題】

【解決手段】III族窒化物半導体素子およびその製造方法の実施形態は、高温処理中にIII族窒化物材料に損傷を与えずに、素子のコンタクトを形成することを可能にする低抵抗の不動態化層を備えてよい。不動態化層は、素子全体を不動態化するために用いられてよい。不動態化層は、さらに、素子のコンタクトと活性層との間に設けられて、導電のための低抵抗の電流路を提供してもよい。この不動態化処理は、FET、整流器、ショットキダイオードなど、任意の種類の素子に用いて、破壊電圧を改善すると共に、コンタクトの接合部付近の電界集中効果を防止してよい。不動態化層は、外部拡散に関してIII族窒化物素子に影響を与えない低温アニールで活性化されてよい。

(もっと読む)

少なくとも一つの電気的コンポーネントを有するフィルム及びその生産プロセス

【課題】

本発明は、少なくとも一つの電気的コンポーネントを有するフィルムと、そのようなフィルムの生産プロセスと、に関するものである。

【解決手段】

放射架橋性接着剤を備えた接着剤層はベースフィルム(61)に塗布される。接着剤層はベースフィルムへパターン形状に塗布され、及び/または、接着剤層がパターン形状に構造化して硬化するようにパターン形状に放射線照射される。キャリアフィルムと電気的機能層とを備えたトランスファーフィルム(41)が接着剤層に塗布される。キャリアフィルム(41)は、ベースフィルム、接着剤層、及び電気的機能層を含むフィルム体から剥がされ、そこではパターン形状に構造化された第一領域では電気的機能層はベースフィルム(61)に残り、パターン形状に構造化された第二領域では電気的機能層は前記キャリアフィルム(45)に残り、ベースフィルム(61)からキャリアフィルムとともに取り除かれる。

(もっと読む)

(もっと読む)

半導体部品およびその製造方法

本発明は、有機半導体、特に有機電界効果トランジスタ、との静電的相互作用を制御するための層(10)を備える半導体部品に関するものである。上記半導体部品は、上記化合物が、a)基板と結合するために、少なくとも1つのアンカー基(1)を有する化合物を含み、b)当該化合物は、少なくとも1対の自由電子対および/または双極子モーメントを有する少なくとも1つの基(2)をすることを特徴とする。さらに、本発明は、そのような化合物を含む層を形成させるための方法に関するものであり、当該方法によれば、特に、論理関数を付加的に補正(レベルシフト)しなくてもよいOFETを製造することができる。  (もっと読む)

(もっと読む)

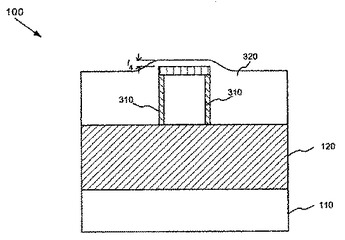

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

線パターン形成方法、デバイスとその製造方法及び電気光学装置並びに電子機器

【課題】複数の線パターンの形成領域から一時的に溢れ出した機能液同士が接触しないように機能液を吐出することによって短絡を防止すると共に、線パターンと線パターンとをより近接させる。

【解決手段】線パターンの形成方法であって、隣合うバンク間34から一時的に溢れ出した上記機能液X同士が接触しないように各上記バンク間34の幅方向の中央Aに対し当該幅方向に変位した位置を各々のバンク間34の吐出位置として上記機能液Xを吐出することによって複数の上記バンク間34に同時に機能液を配置する。

(もっと読む)

601 - 620 / 620

[ Back to top ]