Fターム[4M104GG08]の内容

Fターム[4M104GG08]の下位に属するFターム

Fターム[4M104GG08]に分類される特許

121 - 140 / 620

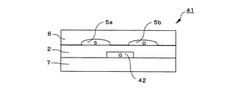

薄膜トランジスタの製造方法および薄膜トランジスタ

【課題】UV露光でも電気的絶縁性が損なわれず、表面濡れ性の変化を利用して印刷法でソース・ドレイン電極のパターニングが可能なゲート絶縁層を有する薄膜トランジスタの製造方法を提供する。

【解決手段】基板7上にゲート電極42およびゲート絶縁層2が順次形成され、該ゲート絶縁層が形成されたゲート電極上に適宜の間隔でソース電極5aおよびドレイン電極5bが対向配置され、該間隔を含む領域に半導体層6が形成された薄膜トランジスタを、活性水素基と反応可能なメラミン誘導体および活性水素基を有する樹脂を含有する溶液を塗布・焼成し、紫外線照射で表面濡れ性が可変のゲート絶縁層を形成し、紫外線照射で該ゲート絶縁層の露光部位を親水性域に変え、親水性域に電極材料含有溶液を印刷法で塗布・乾燥し、ソース電極及びドレイン電極を形成して薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】グラフェン層に対して良好なコンタクトを形成しうる配線構造体を有する半導体装置及びその製造方法を提供する。

【解決手段】グラフェン層と、グラフェン層の第1の領域に形成され、グラフェン層と、グラフェン層に積層された第1のネットワーク・ナノグラファイト層とを含む第1の配線部と、グラフェン層の第2の領域に形成され、グラフェン層と、グラフェン層に積層された第2のネットワーク・ナノグラファイト層とを含む第2の配線部と、グラフェン層の、第1の領域と第2の領域との間の第3の領域上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた半導体装置は、可視光や紫外光を照射することで電気的特性が変化する。このような問題に鑑み、酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】酸化物絶縁層上に膜厚が1nm以上10nm以下の第1の酸化物半導体層を形成し、加熱処理により結晶化させ、第1の結晶性酸化物半導体層を形成し、その上に第1の結晶性酸化物半導体層よりも厚い第2の結晶性酸化物半導体層を形成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

多重膜のエッチング液組成物及びそのエッチング方法

【課題】Cu/Mo積層金属膜、Cu/Mo合金積層金属膜、Cu合金/Mo合金積層金属膜のような、銅又は銅合金の1層以上の銅層と、モリブデン又はモリブデン合金の1層以上のモリブデン層とを含む多重膜を、効率的で優秀に同時に一括してエッチングすることができるエッチング液組成物及びこれを用いた多重膜のエッチング方法を提供する。

【解決手段】エッチング液組成物は、総重量に対して、リン酸50〜80wt%;硝酸0.5〜10wt%;酢酸5〜30wt%;イミダゾール0.01〜5wt%;及び残量の水を含む。添加剤イミダゾールは、銅/モリブデンガルバニック反応調節剤として機能する。

(もっと読む)

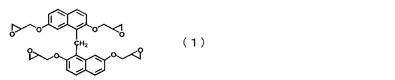

電子デバイス及びその製造方法、並びに、半導体装置及びその製造方法

【課題】従来よりも低い温度での形成が可能である絶縁層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、(A)制御電極12、(B)第1電極14及び第2電極14、並びに、(C)第1電極14と第2電極14との間であって、絶縁層13を介して制御電極12と対向して設けられた、有機半導体材料層15から成る能動層16を備えて成り、少なくとも能動層12と接触する絶縁層13の部分は、下記の式(1)にて示される材料を硬化して成る層から構成されている。 (もっと読む)

(もっと読む)

半導体装置

【課題】 パワートランジスタ及びSBD素子を有する半導体装置において、SBD素子の耐圧を高める。

【解決手段】 半導体装置は、半導体基板の主面に第1および第2領域を有し、前記第1および第2領域内にはそれぞれ複数の第1および第2導電体が形成され、前記第1領域内の隣接する第1導電体間には、第1半導体領域と、前記第1半導体領域内にあって第1半導体領域と逆の導電型を持つ第2半導体領域とが形成され、前記第2領域内の隣接する第2導電体間には、前記第2半導体領域と同導電型でかつ第2半導体領域より低濃度の第3半導体領域が形成され、前記第3半導体領域の下には第3半導体領域と同導電型で、かつ第3半導体領域より高濃度の第4半導体領域が形成され、前記第2領域の半導体基板上には金属が形成され、前記金属は前記第2半導体領域と電気的に接続され、前記第3半導体領域は、前記金属と接触しショットキー接合を形成している。

(もっと読む)

半導体装置とその作製方法

【課題】特性が良好なトランジスタを提供する。

【解決手段】例えば、ボトムゲート・ボトムコンタクト構造のトランジスタを作製するに際して、ソースとドレインを構成する導電層を3層の積層構造とし、2段階のエッチングを行う。すなわち、第1のエッチング工程には、少なくとも第2の膜及び第3の膜に対するエッチングレートが高いエッチング方法を採用し、第1のエッチング工程は少なくとも第1の膜を露出するまで行う。第2のエッチング工程には、第1の膜に対するエッチングレートが第1のエッチング工程よりも高く、「第1の膜の下に接して設けられている層」に対するエッチングレートが第1のエッチング工程よりも低いエッチング方法を採用する。第2のエッチング工程後にレジストマスクをレジスト剥離液により剥離するに際し、第2の膜の側壁が少し削られる。

(もっと読む)

半導体装置

【課題】トレンチゲート構成のパワートランジスタを有する半導体装置のオン抵抗を低減する。

【解決手段】トレンチゲート構成のパワーMIS・FETQにおいて、ソース用の半導体領域3の上面の層間絶縁層12の端部(位置P1)と上記ソース用の半導体領域3の上面の上記ゲート電極9Eから遠い端部(溝16の外周の位置P2)との間の長さをaとし、上記層間絶縁層12と上記ソース用の半導体領域3の上面との重なり部の長さ(位置P1から溝5aの外周の位置P3までの長さ)をbとすると、0≦b≦aとする。これにより、ソースパッドSPとソース用の半導体領域3の上面との接触面積が増大する上、ソースパッドSPとチャネル形成用の半導体領域4との距離を短くすることができるので、トレンチゲート構成のパワーMIS・FETQのオン抵抗を下げることができる。

(もっと読む)

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置、光学装置及びセンサ装置

【課題】ソース電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側及びソース電極34側に庇状に突き出したフィールドプレート40が形成され、基板32の表面層とフィールドプレート40との間に誘電体膜46が形成され、誘電体膜46は、フィールドプレート40のドレイン電極36側及びソース電極34側の終端面と面一状態となるように切れ込み、ドレイン電極36側の下端からドレイン電極36に接続するようにドレイン電極36に向かって延びており、且つ、ソース電極34側の下端からソース電極34に接続するようにソース電極34に向かって延びている。

(もっと読む)

有機誘電体を有する有機電界効果トランジスタ

【課題】有機トランジスタの大電流および高速スイッチングを達成するために、ゲート絶縁体材料とその製造方法を提供する。

【解決手段】基板1上に、溶液から有機半導体層3を堆積させる工程、および溶液から低誘電率絶縁材料の層を堆積させて、その低誘電率絶縁材料が有機半導体層3と接触するようにゲート絶縁体2の少なくとも一部を形成する工程を含む有機トランジスタを形成する。低誘電率絶縁材料の比誘電率が1.1から3.0未満までである。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

トランジスタ

【課題】ソース電極(ドレイン電極)と、ゲート電極との重畳部に生じる寄生容量値を低減させても、オン電流値をほぼ維持できる新たな電極構造のトランジスタを提供することを課題の一とする。

【解決手段】トランジスタのソース電極及びドレイン電極の電極形状を櫛歯形状にすることによって寄生容量値を低減させる。また、櫛歯状電極の先端部の幅や、電極歯部間の間隔を制御することによって、電極歯部の側面から流れる曲線電流を発生させることができる。この曲線電流が、電極形状を櫛歯形状にすることにより減少する直線電流を補うため、寄生容量値を低減させても、低減させる前とほぼ変わらないオン電流値を維持させることができる。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置

を提供することを課題の一とする。また、同一基板上に複数種類の薄膜トランジスタの構

造を作製して複数種類の回路を構成し、増加する工程数が少ない半導体装置の作製方法を

提供することを課題の一とする。

【解決手段】絶縁表面上に金属薄膜を成膜した後、酸化物半導体層を積層し、その後、加

熱処理などの酸化処理を行うことで金属薄膜の一部または全部を酸化させる。また、論理

回路などの高速動作を優先する回路と、マトリクス回路とで異なる構造の薄膜トランジス

タを配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタや縦型FET等の縦型デバイスを、絶縁膜マスクを用いた選択成長による、ボトムアップ構造にするすることで、精密な制御を要求される工程を削減できる製造方法を提供する。

【解決手段】導電性基板20の第1主表面上に、第1絶縁膜32、金属膜42及び第2絶縁膜52を順次に形成する。次に、第1絶縁膜、金属膜及び第2絶縁膜の、中央領域の部分を除去することにより、導電性基板を露出する成長用開口部70を形成する。次に、成長用開口部内に、半導体成長部82,84を形成する。次に、第2絶縁膜の、中央領域の周囲の周辺領域内に設けられた引出電極領域の部分72を除去することにより、金属膜を露出する引出電極用開口部を形成する。次に、引出電極用開口部内72に、引出電極90を形成する。次に、半導体成長部上及び導電性基板の第2主表面上にオーミック電極92を形成する。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

121 - 140 / 620

[ Back to top ]