Fターム[4M104GG19]の内容

Fターム[4M104GG19]に分類される特許

1 - 20 / 202

層選択レーザーアブレーションパターニング

半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

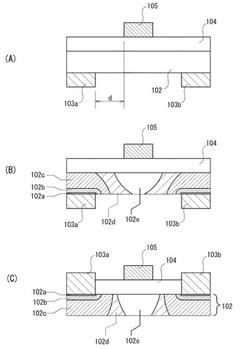

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

保護素子およびそれを備えた半導体装置

【課題】被保護素子に接続されることにより、被保護素子の破壊を未然に防止できる保護素子を提供すること。

【解決手段】アノード電極15とカソード電極16との間に主たる電流を流す被保護素子に対して、電気的に並列に接続される保護素子1であって、GaN層13よりもバンドギャップの大きなAlGaN層14が形成され、AlGaN層14の表面に離間してアノード電極15とカソード電極16とが形成され、アノード電極15とカソード電極と16の間の2次元電子ガス層13Aを流れる電流のオンオフを制御する制御電極19を備えたオンオフ可能領域21を備え、制御電極19が所定の抵抗体20を介してアノード電極15に接続されてなり、アノード電極15が被保護素子のアノード電極15と接続され、カソード電極16が被保護素子のカソード電極16と接続され、被保護素子より耐圧が低く設定されている。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

マルチゲート半導体デバイス

【課題】バランス抵抗器の接続されたゲート間伝導領域を有するマルチゲート半導体デバイスにおいて、スイッチ素子として使用した際の低挿入損失と素子サイズを抑えつつ、オフ時の非線形性を改善する。

【解決手段】バランス抵抗器405のゲート間伝導領域への接続点をゲートの2つの両端より内側に設ける。好ましくはメアンダ状ゲートの屈曲領域4061に設ける。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコン抵抗体の上に急速熱酸化処理により形成され、シリサイド化ブロック用酸化膜の一部として用いる熱酸化膜の膜厚が多種のポリシリコン抵抗体間でばらつくことにより、ポリシリコン抵抗体が部分的にシリサイド化されることを回避する。

【解決手段】多種のポリシリコン抵抗体全てにおいて、急速熱酸化処理によりポリシリコン抵抗体上に生成される熱酸化膜の膜厚と、ポリシリコン抵抗体を含む非シリサイド化領域に形成された保護酸化膜の膜厚との和が、シリサイド化ブロック用酸化膜としてのブロック性能を確保するために必要な膜厚以上となるように、保護酸化膜の膜厚を決定する。多種のポリシリコン抵抗体間で急速熱酸化処理により生成される熱酸化膜の膜厚に差が生じる場合でも、熱酸化膜と保護酸化膜とをシリサイド化ブロック用酸化膜として用いることにより、充分なブロック性能を確保することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

薄膜抵抗を備えた半導体装置の製造方法

【課題】薄膜抵抗と配線部との接触抵抗が高抵抗化することを抑制できる薄膜抵抗を備えた半導体装置の製造方法を提供する。

【解決手段】スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成する。これにより、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

(もっと読む)

スパッタリングターゲットとそれを用いたTi−Al−N膜および電子部品の製造方法

【課題】FeRAMやDRAMなどに使用されるTi−Al−N膜などの成膜用のTi−Al合金ターゲットにおいて、不純物量の低減を図った上で、ターゲットの製造歩留りを高めると共に、膜品質の向上などを図る。

【解決手段】スパッタリングターゲットは、Alを5〜50原子%の範囲で含有するTi−Al合金からなる。このようなTi−Al合金ターゲットにおいて、ターゲットのCu含有量を10ppm以下およびAg含有量を1ppm以下とする。

(もっと読む)

電子素子基板及びその製造方法

【課題】酸化物の一部領域又は全領域の比抵抗を低下させることにより、簡易な工程で多様な電子素子を作製できる電子素子基板の製造方法を提供する。

【解決手段】少なくとも最表層の一部が比抵抗1×109Ω・cm以下の酸化物からなる基板における前記酸化物の一部領域又は全領域に対し、前記基板の電位よりも高い電位を印加することにより、前記一部領域又は前記全領域の比抵抗を低下させる低抵抗化処理工程を有する電子素子基板の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】 フィン型MISトランジスタ、プレーナ型MISトランジスタ及び抵抗素子を集積化した半導体装置において、的確な製造方法を提供する。

【解決手段】 フィン部10aを形成する工程と、フィン部の側面に第1のゲート絶縁膜14及び第1のゲート電極膜15を形成する工程と、フィン部並びにフィン部の側面に形成された第1のゲート絶縁膜及び第1のゲート電極膜を囲み、第1のゲート電極膜に接する半導体導電部16aを形成する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、第2のゲート絶縁膜20及び第2のゲート電極膜21を形成する工程と、半導体導電部上及び抵抗素子形成領域に形成された第2のゲート絶縁膜及び第2のゲート電極膜を除去する工程と、半導体導電部上並びにプレーナ型MISトランジスタ形成領域及び抵抗素子形成領域に、抵抗素子用の半導体膜を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】半絶縁性基板に形成されたゲートパッドにマイナスの電圧が印加され、半絶縁性基板の裏面に形成された裏面電極にプラスの電圧が印加されても、リーク電流を抑制できる半導体装置を提供する。

【解決手段】裏面電極10が形成された半絶縁性基板11の表面上に並列に形成された、複数のゲート電極15がゲート電極接続部21に接続されるとともに、このゲート電極接続部21が複数に分割された半導体装置であって、ゲート電極接続部21間の半絶縁性基板11の表面に形成されたn型の抵抗層22と、このn型の抵抗層22の周囲を覆うように、p型不純物層23と、このp型不純物層23の周囲を覆うように、所望の濃度で形成されたn型不純物層24と、を具備し、ゲートパッド29は、ゲート電極接続部21と、このゲート電極接続部21に隣接するn型の抵抗層22上の引き出し電極25とを接続するように形成される。

(もっと読む)

薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法

【課題】接着層の厚さを増加させることなく、銅の下部層との接着性が向上し、銅が下部層に拡散することを防止することができる薄膜形成方法、表示板用金属配線、及びこれを含む薄膜トランジスタ表示板とその製造方法を提供する。

【解決手段】本発明の薄膜形成方法は、基板上にスパッタリング方法により薄膜を形成する方法であって、薄膜は、電力密度が1.5〜3W/cm2、非活性気体の圧力が0.2〜0.3Paで形成する。薄膜は、非晶質構造を有することができ、チタニウム、タンタル、又はモリブデンのうちのいずれか一つで形成することができる。

(もっと読む)

1 - 20 / 202

[ Back to top ]