Fターム[4M104HH03]の内容

Fターム[4M104HH03]に分類される特許

1 - 20 / 133

表示装置用配線構造

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、配線構造全体の電気抵抗(配線抵抗)も低く抑えられており、更にフッ酸耐性にも優れた表示装置用配線構造を提供する。

【解決手段】本発明の表示装置用配線構造は、基板側から順に、Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含むAl合金の第1層と;Ti、Mo、Al、Ta、Nb、Re、Zr、W、V、Hf、およびCrよりなる群(Y群)から選択される少なくとも一種の元素の窒化物、またはAl合金の窒化物の第2層と、が積層された表層構造を有する。

(もっと読む)

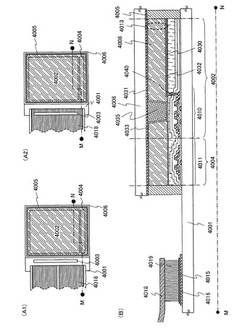

表示装置

【課題】信頼性の高い表示装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを有し、酸化物半導体の下に設けられた絶縁膜と、酸化物半導体の上に設けられた絶縁膜とを有する。平坦性を持たせるため、有機材料を含む絶縁膜をさらに設ける。シール材は、有機材料を含む絶縁膜と重なることはなく、絶縁膜と接している。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、480℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が1〜5μmであることを特徴とする半導体電極構造。

(a)Alマトリックスの最大粒径が1μm以下

(b)ヒロック密度が1×109個/m2未満

(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属の窒化物薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が300nm〜5μmであることを特徴とする半導体電極構造。(a)Alマトリックスの最大粒径が1μm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置用Al合金膜

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられた半導体装置用Al合金膜を提供する。

【解決手段】500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が500nm〜5μmであることを特徴とする半導体装置用Al合金膜。(a)Alマトリックスの最大粒径が800nm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間にバッファ層が設けられた逆スタガ型(ボト

ムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン

電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設

けることによってオーミック性のコンタクトを形成する。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

化合物半導体デバイス

【課題】高温にさらされても、Au配線表面に析出物が発生することを抑制できる半導体デバイスの製造方法を提供する。

【解決手段】化合物半導体基板1上の、Auからなる下部配線層3aと上部配線層3bの上部を覆って、Auより薄膜応力が小さく高融点を有する金属であるタンタルあるいはチタンからなる配線被覆層5と5’をスパッタにより形成する。

(もっと読む)

薄膜トランジスタ基板、および薄膜トランジスタ基板を備えた表示デバイス

【課題】金属配線膜のドライエッチングレートの低下やエッチング残渣を発生させることがなく、また該金属配線膜のヒロック耐性や電気抵抗率が抑制され、更に該金属配線膜と直接接続する透明導電膜や酸化物半導体層とのコンタクト抵抗率が抑制された薄膜トランジスタ基板、及び該薄膜トランジスタ基板を備えた表示デバイスを提供する。

【解決手段】薄膜トランジスタ基板であって、金属配線膜は、ドライエッチング法によるパターニングで形成された、Ni:0.05〜1.0原子%、Ge:0.3〜1.2原子%、Laおよび/またはNd:0.1〜0.6原子%を含有するAl合金膜とTi膜とからなる積層膜あって、該Ti膜が、該酸化物半導体層と直接接続していると共に、該Al合金膜が、該透明導電膜と直接接続している。

(もっと読む)

金属配線

【課題】従来の、真空装置を用いた形成方法に比べて簡便かつ安価に形成され、しかもインクジェット印刷方法によって形成されるもの比べて、断線等を生じることなしに、より細線化された金属配線を提供する。

【解決手段】Ag粒子、またはAgを50原子%以上含む合金粒子を含む分散液を塗布して塗膜を形成し、乾燥後にパターン形成したのち焼成して形成され、その縁部2における、基材の表面方向の、想定される外形線4からの凹入量の最大値と突出量の最大値との和が50nm以下、前記縁部2における、基材3の表面方向の、想定される外形線4と直交し、かつ金属配線1の厚み方向の断面のうち、前記厚み方向の外形線の、前記基材3の表面と接する部分の、前記基材3の表面との交差角度が70°以下で、かつ抵抗率が14μΩ・cm以下である。

(もっと読む)

表示装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置用Al合金膜である。

(1)Alと、X群から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含む第1の析出物について、円相当直径20nm以上の析出物が500,000個/mm2以上の密度で存在する。

(もっと読む)

表示装置

【課題】TFTと接続するソース電極あるいはドレイン電極のスルーホールにおけるコンタクト抵抗を減少させ、表示装置の動作効率を向上させる。

【解決手段】スルーホールにおいて、TFTのソース部とソース電極8が接続している。ソース電極8は、バリヤメタル、Al合金82、キャップメタル83の3層から形成されている。バリヤメタルは半導体層と接触する下層81aとAl合金と接触する上層81bとに分かれている。バリヤメタルの下層81aをスパッタリングして形成した後、熱処理し、その後、ベースメタルの上層81b、Al合金82、キャップメタル83を連続してスパッタリングによって形成する。Al合金82と接触するバリヤメタルの上層81bは酸化されていないので、スルーホールにおけるコンタクト抵抗の上昇を防止することが出来る。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

スパッタリングターゲット及びその製造方法、並びにトランジスタ

【課題】酸化物半導体膜を成膜する成膜技術を提供することを課題の一とする。

【解決手段】金属酸化物の焼結体を含み、その金属酸化物の焼結体の含有水素濃度が、たとえば、1×1016atoms/cm3未満と低いスパッタリングターゲットを用いて酸化物半導体膜を形成することで、H2Oに代表される水素原子を含む化合物、もしくは水素原子等の不純物の含有量が少ない酸化物半導体膜を成膜する。また、この酸化物半導体膜をトランジスタの活性層として適用する。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トランジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

Al基合金スパッタリングターゲット

【課題】低配線抵抗と耐ヒロック性に優れた金属薄膜の形成に有用であり、好ましくはスパッタリング時のスプラッシュの発生を抑制することができるAl基合金スパッタリングターゲットを提供する。

【解決手段】本発明のAl基合金スパッタリングターゲットは、Feを0.0010〜0.4質量%と、Siを0.0010〜0.50質量%含有することを特徴とする。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】オフ電流および漏れ電流が抑制された薄膜トランジスタ、および前記薄膜トランジスタを歩留り良く製造することのできる薄膜トランジスタの製造方法を提供する。

【解決手段】ゲート電極12上にゲート絶縁膜12を介して順次形成されるSi(i)膜13およびSi(n)膜14上に金属膜を形成し、フォトレジストパターン22をマスクとしてエッチングし、ソース電極15およびドレイン電極16を形成する。酸素を含むプラズマで処理して、フォトレジストパターン22の側面を後退させるとともに、ソース電極15およびドレイン電極16の側面および露出した上面にAl酸化皮膜17を形成する。残存するフォトレジストパターン22およびAl酸化皮膜17をマスクとして、チャネル部18のSi(n)膜14およびSi(i)膜13の表面の一部をエッチングする。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ヒロックに対して400℃程度の耐熱性を有するNd添加量2at%のAlNd層を塩素系ガスでプラズマエッチングする場合、フェンスと呼ばれる反応生成物が堆積した領域が生じる。フェンスの存在により、AlNd層をゲート電極としてTFTを形成した場合、ゲート電極脇に電気的に不安定な領域ができることから、TFTの電気的特性が不安定になる場合があるという課題がある。

【解決手段】AlNd層203を層厚0.45μm以上0.8μm以下、Ndの含有量を0.5at%以上1.0at%以下に形成した。この条件範囲であれば、塩素ガスを主としたプラズマエッチングを行ってもフェンスの発生が抑えられる。また、基板温度を500℃まで上げられることから、層間絶縁層211として信頼性が高い酸化シリコン層をAlNd層203にヒロックを発生させることなく形成することができ、信頼性が高いTFT220を提供することが可能となる。

(もっと読む)

1 - 20 / 133

[ Back to top ]