Fターム[4M106AB17]の内容

半導体等の試験・測定 (39,904) | チェック素子の細部 (1,099) | 形成方法 (210)

Fターム[4M106AB17]に分類される特許

1 - 20 / 210

半導体装置および半導体装置の製造方法

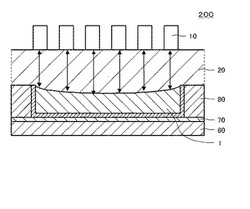

【課題】溝配線に生じるディッシングやエロージョンが配線構造に及ぼす影響を簡便に評価できるような半導体装置を提供する。

【解決手段】TEG200は、多層配線層中に設けられている。また、多層配線層中の第1絶縁膜に埋め込まれた下層溝配線1を備えている。TEG200は、第1絶縁膜80(図示せず)の表層に埋め込まれた下層導体パターン1と、第1絶縁膜80上及び下層導体パターン1上に形成された第2絶縁膜20と、それぞれが同一の下層導体パターン1に対向する複数の上層導体パターン10と、を有している。なお、上層導体パターン10は、第2絶縁膜20の表層に埋め込まれていても良いし、第2絶縁膜20上に形成されていても良い。

(もっと読む)

半導体装置の評価用TEG、オーバーエッチング率の演算方法および半導体装置の評価方法

【課題】評価用TEGにおいて、ビアエッチングによる層間膜換算におけるオーバーエッチング量を数値化する。

【解決手段】第1の層間絶縁膜12上の、VIA実寸測定用パターン2の形成領域には下部配線を設けずに、VIA抵抗測定用パターン4の形成領域には下部配線14を設け、この上に第2の層間絶縁膜16を生成する。この第2の層間絶縁膜16に、エッチングによりビアホール20aを形成した後、導電性部材を堆積させてビアTEG20を形成する。下層に下部配線14が配置されたビアTEG20(204)のビアホール深さbと下層に下部配線14が配置されないビアTEG20(202)のビアホール深さaとの比からオーバーエッチング率(量)を演算する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】TEGによる検査結果を容易に確認できるようにしつつ、TEGの占有面積を小さくする。

【解決手段】TEG群300は、第1テスト用パッド310、第2テスト用パッド312、及び複数のTEG(例えば第1TEG320、第2TEG340、及び第3TEG360)を有している。複数のTEGは、電気回路上、第1テスト用パッド310と第2テスト用パッド312の間に位置し、互いに直列又は並列に配置されており、かつ平面視で互いに重なっていない。本実施形態において、TEG群300を構成するTEGは、OBRICH(Optical Beam Induced Resistance Change)用のTEGである。

(もっと読む)

半導体素子における配線不良検出方法、半導体ウェーハ及び半導体素子

【課題】製品用半導体ウェーハについて配線不良を検出することが可能で、かつ、製品となる各半導体素子について配線不良を検出することが可能な、半導体素子における配線不良検出方法を提供する。

【解決手段】半導体ウェーハ10に複数の半導体素子100を製造する際に、素子形成領域R1の外周部に形成する接地配線112よりもさらに外周側に当該接地配線112よりも細い不良検出用配線122を各半導体素子100に形成するとともに、不良検出用配線122に接続された測定用端子124を素子形成領域R1の周囲のスクライブ領域R2に形成しておき、当該測定用端子124を用いて配線不良を検出することを特徴とする半導体素子における配線不良検出方法。

(もっと読む)

試料汚染方法

【課題】基板上の半導体デバイスを均一に汚染した試料を作成できる試料汚染方法を提供することを目的とする。

【解決手段】本発明の実施形態に係る試料汚染方法は、汚染物を含有する薬液を筺体内へ噴霧する工程と、噴霧により薬液が充満した筺体内へ半導体基板を搬入する工程と、薬液が充満した筺体内へ半導体基板を所定時間放置する工程と、所定時間経過後に、半導体基板を筺体内から搬出する工程と、を有する。

(もっと読む)

評価素子、半導体装置および半導体装置の製造方法

【課題】活性領域と素子分離絶縁膜との段差を精度よく評価する技術を提供する。

【解決手段】半導体基板10に形成されたトレンチに埋め込まれた素子分離絶縁膜18と、前記半導体基板10に形成され不純物を含む活性領域36と、前記活性領域36と前記素子分離絶縁膜18との間の段差を測定するための前記活性領域36の幅W1〜W7が異なる複数の段差測定部52a〜52gと、を具備する評価素子によって前記段差を測定し、この測定結果に基づき、ゲート寸法を調整する。

(もっと読む)

環境雰囲気の不純物汚染評価方法

【課題】シリコンウェーハが直接曝露される環境雰囲気のボロンおよびリンからなる群から選ばれる不純物による汚染を、高精度に評価する手段を提供すること。

【解決手段】環境雰囲気の不純物汚染評価方法。上記評価対象不純物は、ボロンおよびリンからなる群から選ばれる少なくとも一種である。評価対象雰囲気中でホットプレート上にシリコンウェーハを配置し加熱することにより該シリコンウェーハ表面に酸化膜を形成すること、上記酸化膜形成後のシリコンウェーハを、引き続き評価対象環境雰囲気中に所定時間放置すること、次いで上記酸化膜表面を回収液と接触させること、上記酸化膜表面と接触させた回収中の評価対象不純物量を測定すること、および、測定された評価対象不純物量に基づき、前記環境雰囲気中の不純物汚染レベルを判定すること、を含む。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の設計方法

【課題】TEGパターンより上の層を除去しなくてもTEGパターンを用いた検査を行うことができるようにする。

【解決手段】複数の配線層200,300,400は第1TEGパターン30の上に形成されている。複数の配線層200,300,400には、それぞれ配線242,342,442及び複数のダミーパターン224,324,424が形成されている。電極パッド444は、最上層の配線層400に形成されている。そして平面視において、第1TEGパターン30は、いずれの配線242,342,442及びダミーパターン224,324,424にも重なっていない。

(もっと読む)

半導体装置及びその製造方法

【課題】パッシベーション膜にクラックを生じさせるか否かを容易に判定できる構造を有する半導体装置を提供する。

【解決手段】半導体装置1は、下部電極23の上面に達する接続孔30hを持つパッシベーション膜30を備える。パッシベーション膜30は、接続孔30hを除いて下部電極23の周縁部を含む領域を被覆する。下部バリアメタル膜31は、下部電極23とパッシベーション膜30の凸状部分30bとを被覆するように形成されている。バンプ電極35から離れた領域でパッシベーション膜30に形成されている段差部分を被覆するように金属膜パターン31Tが形成されている。

(もっと読む)

半導体装置

【課題】プローブカードの汎用性を維持しつつ、スクライブTEGの評価素子を大規模化する。

【解決手段】半導体装置は、半導体基板の上に行列状に形成された複数の半導体集積回路101と、複数の半導体集積回路に沿ってそれぞれ行方向又は列方向に延びるように形成された複数の第1のスクライブライン領域及び第2のスクライブライン領域と、第1のスクライブライン領域に形成され、第1の評価素子120〜125及び評価用電極パッド110〜116を含むスクライブTEG128と、第2のスクライブライン領域に形成された第2の評価素子160、161と、複数の半導体集積回路のうちの少なくとも1つの半導体集積回路、第1のスクライブライン領域又は第2のスクライブライン領域に形成された少なくとも1つのスクライブ間配線170〜173とを備えている。第2の評価素子とスクライブTEGとは、スクライブ間配線を介して電気的に接続されている。

(もっと読む)

パターン形成方法及び半導体装置の製造方法

【課題】半導体リソグラフィ技術を用いて感光性樹脂膜をパターニングする工程の良否を正確且つ簡易に検査することができるパターン形成方法を提供する。

【解決手段】パターン形成方法は、基板1の主面上の被検査領域に感光性樹脂膜を形成する工程と、投影光学系を用いて、マスクに形成された原版パターンを透過した露光光を感光性樹脂膜の表面に照射する露光工程と、感光性樹脂膜に現像処理を施して原版パターンに対応する被検査パターン2を形成する現像工程とを備える。被検査パターン2は、一端側から他端側に向かうにつれて厚みが変化する傾斜構造2sa,2sbを有する。原版パターンは、被検査パターン2の厚み分布に応じた光透過率分布を有する。

(もっと読む)

テストエレメントグループおよび半導体装置

【課題】小さな面積でより多くの素子を搭載することができ、さらに、素子特性を精度良く測定することの可能なテストエレメントグループおよびそれを備えた半導体装置を提供する。

【解決手段】各グループGNにおいて、全ての入力端子INが共通のドレインソース線DSLに接続されている。各グループGNにおいて、全ての出力端子OUTが入力端子INに非接続のドレインソース線DSLに、他の出力端子OUTと非共有で接続されている。さらに、一のグループGNにおける共通のドレインソース線DSLと、他のグループGNにおける共通のドレインソース線DSLとが互いに異なっている。

(もっと読む)

評価素子

【課題】チャージアップした電荷を検出する感度を向上させること。

【解決手段】半導体基板10上に形成された絶縁膜14と、前記絶縁膜内に形成され、延伸方向に延伸した延伸部22を含む第1配線20と、前記絶縁膜内に設けられ、前記半導体基板と前記延伸部とを電気的に接続するコンタクト26と、前記絶縁膜内に形成され、前記延伸部と前記半導体基板の面方向に対向し前記延伸部より長さの短い対向部32と、前記対向部から前記第1配線の反対方向に引き出される引き出し部34と、を含む第2配線30と、前記引き出し部に電気的に接続されたアンテナ電極40と、含む評価素子。

(もっと読む)

半導体集積装置の評価システム及び評価用半導体チップ

【目的】プラズマプロセスによる半導体集積装置の各製造段階において、所望のエッチング工程で生じたチャージアップの度合いのみを測定することが可能な半導体集積装置の評価システム及び評価用半導体チップを提供することを目的とするものである。

【構成】評価用半導体チップにプラズマエッチング処理を施している間にこの評価用半導体チップ内に生じたチャージアップに伴って流れる電流を、評価用半導体チップから外部に導出されている第1リード線及び第2リード線を介して計測する。評価用半導体チップは、シリコン基板上にゲート酸化膜、ゲート電極、プラズマによる電子電流の流入を部分的に遮断するパターンを有するレジストが積層された構造を有する。この際、レジスト上面側からシリコン基板の表面までを貫通する第1のコンタクトホールを介して上記第1リード線がシリコン基板の表面と電気的に接続されていると共に、上記レジストを貫通する第2のコンタクトホールを介して第2リード線がゲート電極の表面と電気的に接続されている。

(もっと読む)

半導体集積回路及び半導体集積回路の試験方法

【課題】実際の動作条件下においてエレクトロマイグレーションの劣化現象を検知すると共に、故障の兆候を検知することが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路10は、カウンタ回路6と、遅延クロック信号56を生成する遅延素子5と、クロック信号52のクロックサイクル毎にトグルするデータを入力する第1のフリップフロップ1と、第1のフリップフロップ1からの出力信号を入力する配線4と、遅延クロック信号56に基づき駆動し、配線4からの出力信号を入力する第2のフリップフロップ2と、クロック信号52に基づき駆動し、第1のフリップフロップ1からの出力信号を入力する第3のフリップフロップ3と、第2及び第3のフリップフロップ2、3からの出力信号の排他的論理和を出力する排他的論理和回路7と、を有する。

(もっと読む)

半導体ウェーハ、及びその製造方法

【課題】シリコン基板にダメージを与えずに、ゲート下の不純物分布の正確な評価を安定して行うことのできる半導体ウェーハとその製造方法を提供する。

【解決手段】 半導体ウェーハは、半導体基板上の所定の箇所に設定されたモニター領域に、他と電気的接続を有しない断面形状がW字型のダミー充填部を有する。

(もっと読む)

半導体装置及び半導体チップ

【課題】半導体チップを製造する際のダイシング精度の悪化を防止するとともに、流通後のTEGを用いた測定の実行を完全に防止する。

【解決方法】半導体装置は、複数の製品領域と、それら製品領域間に設けられたスクライブ領域とを備える。複数の製品領域のそれぞれは、プロービング用電極34、40とセンス電極36、38を少なくとも有するTEG30を有している。TEG30には、TEG内の他の部分と比較して電流許容量が低く設定されているセンス配線36a、38aが設けられている。半導体装置では、センス配線36a、38aに所定電流以下の電流が印加された状態でTEG30の特性を測定することができる。その一方、センス配線36a、38aに所定電流を越える電流を印加するとセンス配線36a、38aが破壊される。

(もっと読む)

SOIウェーハの検査方法

【課題】SOIウェーハに半導体素子を形成する前に当該SOIウェーハの転位欠陥に関する良否の判定を行うことが可能な検査方法を提供する。

【解決手段】SOIウェーハ1にSOIウェーハ1のスクライブ領域6aにおける表面から埋め込み酸化膜3まで到達する検査用トレンチ7・7・・・を形成し、検査用トレンチ7・7・・・にシリコンと異なる熱膨張係数を有する埋め込み材8・8・・・を埋め込み、SOIウェーハ1を所定の処理温度に到達するまで加熱し、SOIウェーハ1の表面のうち検査用トレンチ7・7・・・の周囲となる部分に現れた転位9・9・・・を検出し、検出された転位9・9・・・に基づいてSOIウェーハ1の良否を判定する。

(もっと読む)

半導体装置の試験方法

【課題】長期信頼性を保障することができる半導体装置の試験方法を提供すること。

【解決手段】ゲート絶縁膜を介してゲート電極が埋め込まれてなる第1トレンチと、第1絶縁膜を介して、ゲート電極に非接続の埋設電極が埋め込まれてなる第2トレンチと、を有する半導体装置において、埋設電極を、両側を第1トレンチと第2トレンチとに挟まれるチャネル領域の表面のみに導電接続する。半導体装置のターンオフゲート抵抗およびターンオフ電流の一方または両方を、ターンオフ時に埋設電極とチャネル領域との間に所望の電位差が発生するように設定して、ターンオフスイッチング試験を行う。それによって、半導体装置をターンオフさせたときに埋設電極とチャネル領域との間に所望の電位差が発生し、埋設電極とチャネル領域との間の第1絶縁膜に電圧ストレスがかかるので、第1絶縁膜の絶縁特性を評価することができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】液晶ドライバ等の半導体集積回路装置においては、その形状が極端に細長いため、長手方向にプロセス特性がばらつくと、所望のデバイス特性が得られない。そこで、実製品ウエハにプロセスモニタ用の検査用素子を各種配置して、それらを測定することによって、プロセス特性のばらつきを監視している。しかし、ウエハ内におけるグローバルなプロセスばらつきは、比較的抽出しやすいものの、チップ内の局所的なプロセスばらつきの高精度の抽出は、大幅に検査用素子密度を上げない限り、困難であることが、本願発明者等により明らかにされた。

【解決手段】本願の一つの発明は、半導体集積回路装置の製造方法において、ウエハ上のチップ領域の近傍に複数のテスト素子領域を異なるピッチで配列し、プローブテストにおいて、それらを電気的に計測することにより、プロセスの局所的ばらつきをモニタするものである。

(もっと読む)

1 - 20 / 210

[ Back to top ]