Fターム[4M106DB05]の内容

半導体等の試験・測定 (39,904) | 外観・パターン検査装置 (3,574) | 検出部 (1,484) | 2次電子検出器 (538)

Fターム[4M106DB05]に分類される特許

1 - 20 / 538

基板の凹部の検査方法および基板のレジスト膜の検査方法

【課題】有底の凹部の状態を非破壊で検査し、製造コストを低減させる。

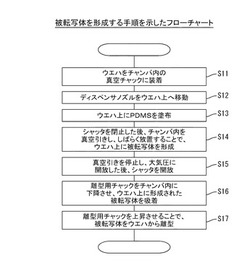

【解決手段】本発明のウエハ50のビア孔51の検査方法は、有底のビア孔51が表面に形成されたウエハ50に被転写材料を塗布し、この被転写材料をビア孔51内に充填させ、被転写材料を硬化させた後、ウエハ50から離型させることでビア孔51がビア像71として転写されてなる被転写体70を形成する転写工程と、ビア像71の表面を観察することでその表面形状の画像データを作成する表面観察工程と、ビア像71の画像データに基づいてビア像71の形状を評価し、ビア孔51内の状態を検査する検査工程とを備えたところに特徴を有する。

(もっと読む)

半導体パターン検査装置

【課題】虚報を多発させることなく,システマティック欠陥を検出する半導体パターン検査装置を提供する。

【解決手段】検査に先立ち,前準備として,少数の実画像101と対応する設計データ102から,特徴量算出部でそれぞれのパターンの特徴を表す特徴量を算出し(106a,106b),これと,欠陥座標が指定された教示データ103とから,正常と欠陥を識別するルールである識別境界を識別境界算出部で算出する(107)。検査時には,検査対象の実画像104と,設計データ105から106a,106bと同様にして特徴量を算出し(108a,108b),これらに対し,検査前準備にて算出した識別境界107を適用することにより,欠陥判定部で欠陥判定109を行う。

(もっと読む)

荷電粒子線装置

【課題】本発明は、ビーム走査によって得られる検出信号を積算して画像を形成する装置において、取得画像のS/Nの向上と、シュリンクの低減の両立の実現を目的とするものである。

【解決手段】上記目的を達成するために本発明によれば、画像データを積算して、画像を形成する荷電粒子線装置において、設定される走査線方向の大きさごとに、走査線方向とは垂直な方向に、異なる大きさであって、異なる走査線数を持つ複数の走査パターンによる走査が可能な偏向器と、1フレーム内にて、前記走査線方向とは垂直な方向の大きさに比例する数の走査線位置への走査によって得られる検出信号を1の走査位置の検出信号として、積算する演算装置を備えたことを特徴とする荷電粒子線装置を提案する。

(もっと読む)

欠陥観察方法及び欠陥観察装置

【課題】欠陥画像取得時間を短縮することが可能な欠陥観察方法および欠陥観察装置を提供する。

【解決手段】複数の画像取得条件から選択した任意の画像取得条件を用いて検査対象である試料の表面を撮像して欠陥画像を取得する画像取得工程と、前記画像取得工程にて取得した欠陥画像を処理して、該試料の表面上の欠陥位置を算出する欠陥位置算出工程と、前記欠陥位置算出工程にて算出した欠陥位置の確からしさである欠陥検出確度を求める欠陥検出確度算出工程と、前記欠陥検出確度算出工程にて求めた欠陥検出確度が予め定めた条件を満たすかどうかを判定する終了判定工程と、を備え、前記終了判定工程にて該条件を満たすと判断するまで、前記複数の画像取得条件から画像取得条件を選択し直し、前記画像取得工程と前記欠陥位置算出工程と前記欠陥検出確度算出工程と前記終了判定工程とを繰り返す。

(もっと読む)

領域決定装置、観察装置または検査装置、領域決定方法および領域決定方法を用いた観察方法または検査方法

【課題】高感度検査や高精度計測を行うことが必要な部分領域を、効率的に決定する。

【解決手段】領域決定装置は、試料を検査して得た試料上の欠陥位置あるいは試料上において欠陥が発生する可能性があると予測された欠陥位置を撮像した画像を含む欠陥データの、少なくとも複数種の欠陥属性情報に基づき欠陥の発生度合いを算出する算出部と、発生度合いが所定以上となる欠陥データを抽出し、該抽出された欠陥データから観察または検査を行う試料上の領域を決定する領域決定部と、を有する。

(もっと読む)

半導体装置、半導体装置の検査方法及び製造方法

【課題】コンタクト周りのキラー欠陥検査を容易にするパターンを有する半導体装置、半導体装置の検査方法及び製造方法を提供する。

【解決手段】半導体基板の第1導電型領域の表面に設けられ、それぞれ第1の方向に延在する複数の第2導電型領域と、複数の第2導電型領域とそれぞれ複数の個所で交差することにより各第2導電型領域にソースとドレインが直列に接続された複数のMOSトランジスタを形成するゲート配線と、複数のMOSトランジスタとゲート配線との表面を覆う絶縁膜と、絶縁膜の表面から複数のMOSトランジスタのソースドレイン領域にそれぞれ設けられた複数の第1のコンタクトと、絶縁膜の表面からゲート配線の各領域に共通に接続された第2のコンタクトと、を有する。

(もっと読む)

レシピ生成装置、検査支援装置、検査システムならびに記録媒体。

【課題】設計レイアウトに記録された情報を、直接、解析して、所望の領域を抽出し、この抽出方法を用いて検査レシピを生成し、効率的な検査を実現する。

【解決手段】設計レイアウトデータの階層情報を解析して、その内部データであるセル一つ一つが設計レイアウトデータ内での参照回数を計算して、参照回数の多い順に並び替えて、対象を探索し、その上位セルを追跡することによって、メモリマットなどの所望の回路モジュールの領域抽出を容易にする。

(もっと読む)

電子顕微鏡システム及びその制御方法

【課題】試料の鮮明な画像を撮影することができる電子顕微鏡システム及びその制御方法を提供すること。

【解決手段】電子顕微鏡システムは、電子線を発生させる電子銃と、電子線を試料に照射するための光学系と、当該試料をセットするステージと、当該試料を観察するために、当該試料への電子線の照射を基に試料を撮影する撮影機構と、撮影機構が撮影した当該試料の画像を解析する解析機構と、当該試料と撮影機構との相対的位置を調節する位置調節機構と、を備える。位置調節機構は、解析機構の解析結果を基に、ステージ又は撮影機構の視野のうちの少なくとも一方を移動させる。

(もっと読む)

光学式検査装置、検査システムおよび座標管理用ウエハ

【課題】欠陥座標に含まれている誤差を低減可能な光学式検査装置を提供する。

【解決手段】チャンネルが配列されたラインセンサと、ウエハをステージに載せてラインセンサに対して移動させる移動手段と、行列の行毎に1つ且つ列毎に1つ擬似欠陥ダイが形成され擬似欠陥ダイには複数の擬似欠陥が列方向に一列に形成されている座標管理用ウエハを検査したのを受けてチャンネル上に結像した擬似欠陥のステージ上の位置を擬似欠陥ステージ座標Xs0として検出するステージ位置検出手段と、擬似欠陥ステージ座標Xs0を擬似欠陥ダイ座標に変換する座標変換手段と、設計座標に対する擬似欠陥ダイ座標の差分ΔXを算出する差分算出手段と、擬似欠陥ステージ座標Xs0に対して差分ΔXが一定の振幅A1で振動し直線L1に沿って増加又は減少する座標誤差特性パターンCP1を取得する特性パターン取得手段とを有する。

(もっと読む)

検査装置

【課題】検査精度を向上させ、5〜30nmのデザインルールにも適用できる検査方法及び検査装置を提供すること。

【解決手段】本発明の検査装置は、荷電粒子又は電磁波の何れか一つをビームとして発生させるビーム発生手段と、ワーキングチャンバ内に保持した検査対象に前記ビームを導き照射する1次光学系と、可動式のニューメリカルアパーチャ、および前記検査対象から発生して当該ニューメリカルアパーチャを通過した二次荷電粒子を検出する第1検出器を有する2次光学系と、前記第1検出器によって検出された二次荷電粒子に基づいて画像を形成する画像処理系と、前記可動式のニューメリカルアパーチャと前記第1検出器の間に設けられ、前記検査対象から発生する二次荷電粒子のクロスオーバ位置における位置及び形状を検出する第2検出器とを備える。

(もっと読む)

パターン検査方法、フォトマスク、半導体装置の製造方法

【課題】光学的検査で検出された欠陥を、高精度で電子顕微鏡の観察視野に収めることができるパターン検査方法、フォトマスク、半導体装置の製造方法を提供する。

【解決手段】実施形態のパターン検査方法によれば、チップ領域に形成されたデバイスパターンと、チップ外領域に形成された第1のパターンと、チップ外領域に形成され第1のパターンとは異なる第2のパターンとをそれぞれ含む複数の領域が形成されたウェーハの光学的検査により、デバイスパターンの欠陥をウェーハ上での位置座標と対応づけて検出すると共に、第1のパターンとの比較から第2のパターンをウェーハ上での位置座標と対応づけて検出する。また、検出した第2のパターンの位置座標に電子顕微鏡の観察視野を合わせたときの観察結果に基づいて、デバイスパターンの欠陥の位置座標を補正する。

(もっと読む)

パターン検査装置および検査方法

【課題】ウエハとマスクのように同等の回路パターンが形成されているが形状が異なる試料を一つの装置で検査することができる検査装置または検査方法を提供する。

【解決手段】検査装置が、形状が異なる複数の試料に対応した複数の搬送ホルダを備えることにより、同一試料室で異なる試料の検査を可能とする。更に、双方の試料に対する検査結果を照合する機能を備えることにより、欠陥と欠陥が生じる原因との関係を容易に解析できるようにする。

(もっと読む)

パターン寸法測定方法及びパターン寸法測定装置

【課題】 測定対象のパターンを、その外形によって特定することが困難である場合に、外形及び明るさ以外の情報によって測定対象パターンを特定する技術を提供する。

【解決手段】 走査型電子顕微鏡を用いて、測定対象物の二次元画像を取得する。取得された二次元画像から、測定対象候補として、相互に隣接している2つのパターンを抽出する。測定対象候補の2つのパターンの内部の領域の各々の表面粗さを算出する。算出された表面粗さに基づいて、測定対象候補の2つのパターンのうち一方を、測定対象パターンとして採用する。採用された測定対象パターンの寸法を測定する。

(もっと読む)

半導体デバイスの欠陥検査方法およびそのシステム

【課題】

ステップ・アンド・リピート式の高解像度SEMを用いて予め定められた危険点を検査し、危険点での欠陥発生頻度を統計的かつ信頼性を持って推定する半導体デバイスの欠陥検査方法及びそのシステムを提供する。

【解決手段】

デザインデータ上で欠陥タイプ別に検査点を指定し、この指定された検査点の中から予め指定された数の検査点を欠陥タイプ別に選択し、この選択した欠陥タイプ別に予め指定された数の検査点を撮像してこの検査点における欠陥を検出し、欠陥タイプ別に撮像した検査点の数に対する検出した欠陥の数の比である欠陥比率とこの欠陥比率の信頼区間を算出し、この算出した欠陥タイプ別の欠陥比率の信頼区間と予め設定した基準値とを比較し、この基準値を超える欠陥発生比率をもつ欠陥タイプを求める半導体デバイスの欠陥検査方法及びそのシステムとした。

(もっと読む)

走査電子顕微鏡及び試料作成方法

【課題】検査データから解析対象箇所を選択する場合、全体の中で重要性の高い欠陥が解析対象にならなかった。また、欠陥に対してマーキングを一定の位置で行うと、欠陥の形状や大きさにより、欠陥自体に影響を与え、後段の解析装置での解析に支障をきたすという問題があった。更に、ノンパターンウェーハの場合には、SEMで欠陥が見えない場合、マーキングができなかった。

【解決手段】重要性の高い欠陥が解析対象を選択するため、レビューSEMの自動分類結果を用いて、解析対象欠陥を選択する。また、欠陥自体に影響を与えないため、欠陥毎に距離を変えてマーキングを行う。このため、ADRまたはADCで欠陥の形状,サイズを認識して、影響範囲を考慮した距離を追加した距離にマーキングする。更に、SEMで観察できない欠陥の場合、光学顕微鏡での観察結果を用いてマーキングする。

(もっと読む)

欠陥検査方法、半導体装置の製造方法及び欠陥検査装置

【課題】欠陥検出の精度を向上させることのできる欠陥検査方法を提供する。

【解決手段】ウェハ上に欠陥があるか否かを検査する第1の欠陥検査処理(ステップS11)を実行した後、その第1の欠陥検査処理にて検出された欠陥により、不良チップを判定する(ステップS12,S13)。続いて、不良チップを除いて、その不良チップに隣接するチップに欠陥があるか否かを、第1の欠陥検査処理よりも検査感度を上げて検査する(ステップS16)。

(もっと読む)

欠陥観察方法及びその装置

【課題】検査装置の検査情報とレビュー装置で取得した観察情報とを用い、欠陥の高さ、屈折率、材質の情報を取得して欠陥材質・屈折率分析や、微細なパターン形状の三次元解析を行う方法、並びにこれを搭載した欠陥観察装置を提供する。

【解決手段】試料上の欠陥を観察する方法において、光が照射された試料からの反射・散乱光を受光した検出器からの検出信号を処理して検出した検査結果の情報を用いて観察対象の欠陥が存在する位置を走査電子顕微鏡で撮像して画像を取得し、この取得した観察対象の欠陥の像を用いて欠陥のモデルを作成し、作成された欠陥のモデルに対して光を照射したときに欠陥モデルから発生する反射・散乱光を検出器で受光した場合のこの検出器の検出値を算出し、この算出した検出値と実際に試料からの反射・散乱光を受光した検出器の検出値とを比較して観察対象の欠陥の高さ又は材質又は屈折率に関する情報を求めるようにした。

(もっと読む)

欠陥分類方法及び欠陥分類システム

【課題】自動欠陥分類機能では、装置毎に適切な処理パラメータが異なるが同一の工程において複数の装置が運用される場合でも、それぞれの分類レシピにおける分類クラスに差が発生しないようにする。

【解決手段】同一の工程で異なる画像撮像装置から得られた画像から同種の欠陥画像を特定する対応欠陥特定部209、同一の工程で異なる画像撮像装置から得られた画像を変換し、比較可能な類似した画像に変換する画像変換部212、同一の工程の分類レシピについて、同一の分類クラスを定義し、特定された同種の欠陥画像をそれぞれの対応する分類レシピ内の分類クラスに登録するレシピ更新部211を備えた。

(もっと読む)

半導体装置の製造方法及び洗浄装置

【課題】パターニング前工程にて半導体製造基板の歩留りへの影響を受けず、SEMレビューを可能とする半導体装置の製造方法及び洗浄装置を提供する。

【解決手段】製造装置30aにて所定の製造処理が施されたウェハWは、検査装置10にて欠陥が検査された後、評価装置20に搬送される。評価装置20では、検査装置10にて検出された欠陥がSEMレビューされる。そのSEMレビューされたウェハWは、洗浄装置40に搬送され、その表面に有機溶剤が塗布されて洗浄される。その洗浄後のウェハWは、製造装置30bに搬送され、次工程の製造処理が施される。

(もっと読む)

チップ位置特定システム、チップ位置特定装置、チップ位置特定プログラム及びチップ位置特定方法

【課題】個片化された半導体集積回路チップの個片化前の半導体ウェハー上における位置を特定するのに好適なチップ位置特定システムを提供する。

【解決手段】チップ位置特定システム1を、半導体ウェハー上に形成された複数の第1の半導体チップのパターン面における外観上の特徴的な部位の画像データ及び第1の半導体チップ内における座標情報とを含む第1の外観情報及び半導体ウェハー内における第1の半導体チップの位置情報とを含むチップ位置特定用情報と、第1の半導体チップを個片化後の第2の半導体チップのパターン面における外観上の特徴的な部位の画像データ及び第2の半導体チップ内における座標情報とを含む第2の外観情報とを測定する外観検査装置10と、第1の外観情報と第2の外観情報とを照合し、該照合結果に基づき、第2の半導体チップの個片化前の半導体ウェハー上での位置を特定するチップ位置特定装置20とを含む構成とした。

(もっと読む)

1 - 20 / 538

[ Back to top ]