Fターム[4M112EA18]の内容

Fターム[4M112EA18]に分類される特許

1 - 20 / 571

振動式トランスデューサの製造方法

異なる厚さの領域を有する少なくとも1つの活性部を備える構造を製造する方法

【課題】異なる厚さを有する少なくとも2つの領域を備える活性部を備え、これらの領域の少なくとも一つが単結晶半導体材料からなる構造を製造する、コストを減少させ欠点を有しない方法を提案すること。

【解決手段】第1の基板と異なる厚さの第1及び第2の懸架領域を備える活性部を備える構造を製造する方法であって、前記方法は、以下の、a)第1の基板の前面を加工して第1の基板よりも薄い第1の厚さの少なくとも1つの第1の懸架領域の水平方向の輪郭を画定し、b)懸架領域下部の第1の懸架領域のエッチング停止層を形成し、これが第1の懸架領域下部に配置された半導体材料を除去する段階に先立って行われ、c)第1の基板の前面上に犠牲層を形成し、d)第1の基板の背面から加工して犠牲層をリリースし、少なくとも1つの第2の懸架領域を形成し、第1の懸架領域の停止層に到達させ、e)第1及び第2の懸架領域をリリースする段階を備える。

(もっと読む)

物理量センサー素子及び電子機器

【課題】ベース基板と可動部との貼り付きを防止するとともに、落下等の衝撃時におけるベース基板の可動部に対する緩衝効果を向上させることが可能な物理量センサー素子、及び物理量センサー素子を備えた電子機器の提供。

【解決手段】センサー素子1は、ベース基板2と、ベース基板2上に設けられ、加えられた物理量に応じて可動する可動部33と、を備え、ベース基板2の空洞部21の底面には、平面視で可動部33と重複する位置に突起(25a,25b,25c等)が設けられ、突起(25a,25b,25c等)は、ベース基板2と一体で設けられていることを特徴とする。

(もっと読む)

半導体圧力センサおよび半導体圧力センサの製造方法

【課題】製造コストを抑制することができ、かつ圧力測定精度を向上することができる半導体圧力センサおよびその製造方法を提供する。

【解決手段】半導体圧力センサは、主表面1aに凹部3およびアライメントマーク4を有する第1の基板1と、第1の基板1の主表面1a上に形成されており、第1の基板1の凹部3内の空間IS上を覆うように設けられたダイヤフラム5およびダイヤフラム5上に設けられたゲージ抵抗6を有する第2の基板2とを備えている。アライメントマーク4は第2の基板2から露出するように設けられている。

(もっと読む)

静電容量式センサ

【課題】接続部分の導通が不十分となってしまうのを抑制することのできる静電容量式センサを得る。

【解決手段】静電容量式センサ1は、固定板2と半導体基板4とを接合した際に、固定電極21a、21b、22a、22bに形成された固定電極側金属接触部25と、半導体基板4に形成された半導体基板側金属接触部13とが接触するようになっている。そして、半導体基板側金属接触部13を金属材料を用いて形成し、当該半導体基板側金属接触部13の半導体基板4に接合される基部13a内に、より硬度の高い材料からなるバッファ層14を挿入した。

(もっと読む)

静電容量トランスデューサの製造方法

【課題】感度の高い静電容量トランスデューサの製造方法を提供する。

【解決手段】一連の可動フィンガおよび一連の固定フィンガのうちの一方の位置を画定するために、基体上の層に第1エッチングマスクを適用する。一連の可動フィンガ、一連の固定フィンガ、本体及びばねを画定するために、第2エッチングマスクを適用する。本体は一連の可動フィンガ及びばねに接続され、一連の可動フィンガは一連の固定フィンガと相互に入り込む。第2エッチングマスクを使用して、層および第1エッチングマスクをエッチングする。第1エッチングマスクを使用して、一連の可動フィンガと一連の固定フィンガとのうちの一方が、一連の可動フィンガと一連の固定フィンガのもう一方より短くなるように、エッチングされた層をエッチングする。力が本体に加わったときに、本体が基体に対して平行に動くように、本体、ばね及び一連の可動フィンガをエッチングを用いて分離する。

(もっと読む)

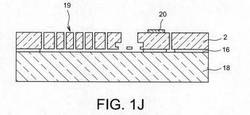

電気機械変換装置の製造方法

【課題】間隙底面の絶縁層の平坦性のバラツキにより生じるセル間及びセルを含むエレメント間の絶縁破壊強度のバラツキを低減した電気機械変換装置の製造方法を提供する。

【解決手段】電気機械変換装置の製造方法において、第一の基板1の上に第一の絶縁層2を形成し、第一の絶縁層2の一部を第一の基板1まで除去して隔壁3を形成し、第一の絶縁層2の一部が除去された第一の基板1の領域上に第二の絶縁層10を形成する。次に、第二の基板18を隔壁3の上に接合して間隙24を形成し、第二の基板18から、間隙24を介して第二の絶縁層10と対向する振動膜23を形成する。隔壁3を形成する工程では、第一の基板1に垂直な方向において間隙24側の高さが中央部の高さよりも低くなるように隔壁3を形成する。

(もっと読む)

半導体装置

【課題】 厚い半導体層に幅の狭いトレンチを形成する際に、半導体の残渣を生じることなくトレンチを形成することが可能な技術を提供する。

【解決手段】 本明細書では、半導体層にトレンチが形成された半導体装置を開示する。その半導体装置では、前記半導体層において、前記トレンチの幅が急変する箇所に、前記トレンチの幅の急変を補償する補償パターンが形成されている。上記の半導体装置では、半導体層において、トレンチの幅が急変する箇所に補償パターンが形成されているので、ディープRIE法によってトレンチ加工を行う際に、半導体の残渣の原因となる急峻な傾斜部の発生を抑制することができる。これによって、厚い半導体層に幅の狭いトレンチを形成する際に、半導体の残渣が発生することを防止することができる。

(もっと読む)

音響センサ及びその製造方法

【課題】基板の裏面側からエッチングすることにより、基板裏面における開口面積が基板表面における開口面積よりも小さな空洞を基板に形成することができる音響センサを提供する。

【解決手段】基板42には、その表面から裏面へ貫通するように空洞44を設ける。空洞44の上方において、基板42の上方には音響振動を感知する薄膜のダイアフラム43を設ける。空洞44の少なくとも1つの壁面は、基板42の表面とその厚み方向中間部との間において、基板42の表面から前記中間部へ向かうにつれて次第に基板42の外側へ向かって広がった第1の斜面47aと、前記中間部と基板42の裏面との間において、前記中間部から基板42の裏面へ向かうにつれて次第に基板42の内側へ向かって狭まった第2の斜面47bとで構成される。また、空洞44の裏面開口幅が表面開口幅よりも小さくなっている。

(もっと読む)

振動式差圧センサとその製造方法

【課題】測定精度が高く、製作が容易で、安価に出来る振動式差圧センサを実現する。

【解決手段】ダイアフラムに設けられた振動子形歪ゲージを具備する振動式差圧センサにおいて、一方の面に振動子形歪ゲージ素子が設けられ他方の面がダイアフラムに相当する厚さに研磨されて形成されシリコンよりなるセンサ基板と、センサ基板の他方の面に一方の面が直接に接合されたシリコンよりなるベース基板と、ベース基板のセンサ基板との接合部に設けられセンサ基板に実質的にダイアフラムを形成し、異物の混入によりダイアフラムの可動範囲が制限されることなく且つ振動子形歪ゲージ素子の振動によって励起されるダイアフラムの振動に対して制動作用をなすための所定の隙間を有する凹部と、凹部に測定圧を導入する導入孔と、凹部に導入孔を介して圧力を伝搬しダイアフラムを制動するための流体とを具備したことを特徴とする振動式差圧センサである。

(もっと読む)

容量性トランスデューサとその製造及び動作方法

【課題】容量性トランスデューサとその製造及び動作方法を提供する。

【解決手段】第1ドーピング領域20と、該第1ドーピング領域20と反対の型のドーピング領域であり、第1振動部分32を含む第2ドーピング領域30と、該第1ドーピング領域と該第1振動部分32との間に備えられた、空間60と、を備えるトランスデューサ。第1及び第2ドーピング領域20,30は、一体である。第1振動部分は複数の貫通ホール40を含み、振動部分上に貫通ホール40を密封する物質膜50が備えられる。

(もっと読む)

サポート部材を用いてマイクロフォンを形成するためのプロセス

【課題】サポート部材を用いてマイクロフォンを形成するためのプロセスを提供すること。

【解決手段】マイクロフォンを形成するための方法は、バックプレート、およびウェットエッチングの犠牲層の少なくとも一部分の上の可撓性の振動板を形成する。この方法は、ウェットエッチングのレジスト材料を追加し、ウェットエッチングのレジスト材料は、振動板を支持するように、振動板とバックプレートとの間に配置される。ウェットエッチングのレジスト材料の一部は、振動板とバックプレートとの間には配置されない。方法はその後、上述の追加の間に追加されたウェットエッチングのレジスト材料の一部を除去する前に、犠牲材料を除去する。その後、ウェットエッチングのレジスト材料は、犠牲材料の少なくとも一部が除去された後に、実質的にその全体が除去される。

(もっと読む)

MEMSセンサ

【課題】シリコン基板と絶縁基板とを接合した時に形成される密閉空間部の圧力を調整することの可能なMEMSセンサを得る。

【解決手段】シリコン基板4と、シリコン基板4の上下両面4a、4bに接合される一対の絶縁基板2、3と、シリコン基板4と絶縁基板2、3とを接合した時に形成される密閉空間部6とを備えたMEMSセンサ1において、絶縁基板2、3またはシリコン基板4の露出した外表面3bに、密閉空間部6と連通する貫通孔7を設ける。

(もっと読む)

物理量センサ及びその製造方法

【課題】本発明に係る静電容量型の物理量センサは、センサ特性の低下を招くことなく、小型化あるいはセンサの感度を向上させる物理量センサ及びその製造方法を提供する。

【解決手段】物理量センサは、フレーム部と、フレーム部の内側に配置された錘部と、錘部とフレーム部とを接続する可撓部と、を備えた半導体基板と、フレーム部の一方の側に接合された第1支持基板と、フレーム部の他方の側に接合された第2支持基板と、第1支持基板と第2支持基板の少なくとも一方に設けられ、第1支持基板又は第2支持基板の一方の側と他方の側を導通する配線用端子と、第1支持基板の面上に設けられ、錘部と対向する第1電極と、第2支持基板の面上に設けられ、錘部と対向する第2電極と、を備え、フレーム部には前記フレーム部の一方の側と他方の側を導通する貫通配線部が配設され、貫通配線部と前記配線用端子とは電気的に接続されている。

(もっと読む)

力学量センサ装置およびその製造方法

【課題】圧力センサと高精度の力学量センサとが最適にモジュール化されて、各力学量センサの性能がモジュール化に伴い低下することのない安価な力学量センサ装置およびその製造方法を提供する。

【解決手段】圧力を検出する第1力学量センサR1の第1力学量検出部M1と第2力学量センサR2の第2力学量検出部M2とが、第1の基板10に変位可能な状態に形成され、第2の基板20が貼り合わされて第1空間K1と第2空間K2が互いに連通せずに形成されてなり、第1の基板10がSOI基板からなり、SOI層3からなる一部の半導体領域Sで第1力学量検出部M1と第2力学量検出部M2がそれぞれ構成されてなり、第2力学量検出部M2が、第2可動半導体領域S2aと第2固定半導体領域S2bの対向する面の静電容量の変化を測定して、第2力学量を検出する力学量センサ装置100とする。

(もっと読む)

振動素子及び振動素子の製造方法

【課題】絶縁性の基板の一面に設けられた基板側電極と、該基板側電極に対向配置された対向電極を有する対向板とを備える振動素子であって、インピーダンスの低減及びキャパシタンス変換、信号増幅などの機能を行うと共に、素子自体のコンパクト化を図ることが出来る振動素子、及び該振動素子を製造する製造方法を提供する。

【解決手段】基板側電極2に対向するように、シリコン単結晶からなる上部板1を配置し、上部板1に、例えば、熱拡散法又はイオン注入法によって形成される、IC回路の不純物領域である集積回路部5を設け、振動素子10にて変換効率の向上及び生産性向上、実装システムのコンパクト化を実現する。

(もっと読む)

振動素子及び振動素子の製造方法

【課題】絶縁性の基板の一面に設けられた基板側電極と、該基板側電極に対向配置された対向電極を有する対向板とを備える振動素子であって、インピーダンスの低減及びキャパシタンス変換、信号増幅などの機能を行うと共に、素子自体のコンパクト化を図ることが出来る振動素子、及び該振動素子を製造する製造方法を提供する。

【解決手段】基板側電極2に対向するように、シリコン単結晶からなる上部板1を配置し、基板3と上部板1との間に、上部板1を保持する保持部31を介在させる。保持部31に、例えば、熱拡散法又はイオン注入法によって形成される、IC回路の不純物領域である集積回路部5を設け、振動素子10にて変換効率の向上及び生産性向上、実装システムのコンパクト化を実現する。

(もっと読む)

センサーデバイス、およびその製造方法

【課題】小型で信頼性の高いセンサーデバイス、及び、その製造方法を提供する。

【解決手段】センサーデバイス1は、第1の面10aに第1の電極11を有する半導体装置としてのICチップ10と、基部21、前記基部21から延伸された振動部を有し、第1の面10aと対向する第2の面20aに第2の電極としての引き出し電極29を有する振動片としての振動ジャイロ素子20と、を備えている。第1の面10aには、絶縁樹脂からなり第1の電極11と配線36を介して電気的に接続された第3の電極37の少なくとも一部を露出させる開口部32aを有する筒状支持部32が設けられ、第1の面10aおよび開口部32aにより形成された凹部に導電性接着剤98が埋設され、引き出し電極29に設けられたバンプ12が凹部内に配置されている。

(もっと読む)

半導体基板とその製造方法および半導体装置

【課題】圧力センサなどのデバイスの製造工程中に空洞内の上下のシリコン面の固着がない半導体基板およびその製造方法を提供する。また、精度良い小型のダイアグラムを有する半導体装置を提供する。

【解決手段】SON構造101のダイアフラム100を有するシリコン基板1およびその製造方法において、SON構造101を構成する空洞2内の下側のシリコン面3に凸状の島4を形成する。半導体基板の表面に深さの異なるホール群を形成し、高温アニール処理することにより一つの大きな空洞を形成する。

(もっと読む)

圧力センサ及びその製造方法

【課題】半導体基板の一方の面から形成することができる圧力センサ及びその製造方法を提供する。

【解決手段】本発明の圧力センサ1の製造方法においては、図4A〜Cに示すように、p型半導体柱7A、7Cを4方向に等分且つ外側又は内側にずらして配置し、そのp型半導体柱7A、7Cの上部に重なるように環状のn型半導体拡散層5を形成し、その環状のn型半導体拡散層5及びp型半導体柱7A、7Cのn型半導体拡散層5との重複部分をエッチングして、環状溝4で囲まれたメサ部3及び4個のブロック状のp型半導体部6A、6B、6C、6Dを半導体基板2の表面側に形成した。

(もっと読む)

1 - 20 / 571

[ Back to top ]