Fターム[4M113AD32]の内容

超電導デバイスとその製造方法 (1,906) | 超電導回路 (453) | 回路構造 (353) | 基板 (266)

Fターム[4M113AD32]の下位に属するFターム

Fターム[4M113AD32]に分類される特許

1 - 4 / 4

酸化物超電導薄膜

【課題】原料の種類が増えるのを抑制しつつ臨界電流特性を良好にする。

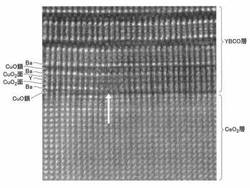

【解決手段】基材と、前記基材上に形成され、希土類元素とCuO鎖とCuO2面とを含んで構成されたRE系超電導体ユニットを複数含有する超電導層と、複数ある前記CuO鎖のうち、前記超電導層と前記超電導層の前記基材側に隣接する層との界面周囲の前記RE系超電導体ユニット中に存在し、前記RE系超電導体ユニットの格子定数により定まるCuO鎖の長さよりも1.2倍以上2倍以下積層方向に長いCuO鎖と、前記長いCuO鎖に対して積層方向に隣接して存在する刃状転位と、を備える酸化物超電導薄膜。

(もっと読む)

SIS素子、SISミクサ、超伝導集積回路用素子、及び、SIS素子の製造方法

【課題】

高性能なSIS素子などを提供する。

【解決手段】

本発明のひとつの側面は、基板と、前記基板上に形成され、下部電極と、上部電極と、前記上部電極と前記下部電極とに挟まれて形成されたバリア層とを有するSIS三層膜と、前記基板上に形成され、前記下部電極と電気的に接続され、前記下部電極と異なる材料のグランドプレーンとを備え、前記SIS三層膜は、前記基板上に形成されたバッファ層又は前記基板の上に接して形成されていることを特徴とするSIS素子にある。本構成によれば、SIS三層膜は、基板上に形成されたバッファ層又は基板の上に接して形成されているため、高品質なSIS接合が実現でき、高性能なSIS素子が得られる。

(もっと読む)

量子素子及びその製造方法

【課題】CF4を用いて、基板をエッチングして懸架型素子を形成した場合、トンネル接合及び島電極が悪影響を受け、十分な電荷分解能等が得られないと言う欠点があった。

【解決手段】基板上に、アッシングより除去できるレジストによって形成されたレジスト台部を設け、レジスト台部上に、トンネル接合及び島電極等の素子部を形成する。素子部をレジスト台部上に形成した後、レジスト台部をアッシングにより除去し、基板をCF4等によりエッチングすることなく、懸架型素子を構成することができる。

(もっと読む)

メモリ装置

【課題】安定した状態でより高密度に記憶保持が行える超伝導デジタル回路用のメモリ装置を実現する。

【解決手段】ジョセフソン接合JJ1,JJ2,JJ3,JJ4,JJ5、コイルL12,L23,L34,L45、抵抗R1,R2,R3(=RM),R4,R5、電圧端子T1,T2,T3,T4,T5を備え、所定の電圧が印可される電圧端子T3とコイルL23及びコイルL34の間の接続ノード(第2接続ノード)との間に抵抗RM(第2抵抗)が接続し、この接続ノードにジョセフソン接合JJ3(第3ジョセフソン接合)が接続している。ジョセフソン接合JJ3は、接続ノードと接地との間に接続されている。

(もっと読む)

1 - 4 / 4

[ Back to top ]