Fターム[4M118BA04]の内容

固体撮像素子 (108,909) | 基本構造 (11,702) | 受光部(光電変換部)を複数持つもの (11,448) | ICマルチチップ型 (85)

Fターム[4M118BA04]に分類される特許

1 - 20 / 85

リニアセンサ及び画像読み取り装置

撮像素子

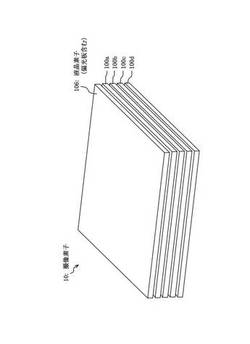

【課題】高解像度化した画素を有する撮像素子を提供する。

【解決手段】本発明の撮像素子10は、X,Y軸平面上に正方又は六方配置された各感光部101から蓄積電荷に相当する信号をZ軸方向に並列に抽出して出力する積層素子100a,100b,100c,100dと、この積層素子における感光部101を有する素子100aに対して設けられ、それぞれの感光部101に対して一部の領域を遮光するための当該感光部101の面積よりも小さい面積を有する1つの遮光部110を、当該感光部101の領域の範囲内で走査することにより各感光部101を所定の分割数で分割し、当該分割した各領域における遮光による蓄積電荷の変化量によって画素を形成する液晶素子106とを備える。

(もっと読む)

イメージセンサユニット、及び、イメージセンサユニットを用いた画像読取装置

【課題】分割出力されたセンサ信号の合成を行う際の処理を容易とするイメージセンサユニットを提供する。

【解決手段】光電変換部PDからのセンサ信号をシフトレジスタSRにより2以上に分割して転送する光電変換素子13を複数個備え、それらの光電変換素子13kからのセンサ信号を2以上のチャンネルで出力すると共に、光電変換素子13kより出力される転送終了の制御信号Sを分割された2回目以降のセンサ信号の転送開始の制御信号とするイメージセンサユニット4であって、光電変換素子13kを最大数備えたチャンネルにおける終端に位置する光電変換素子13kより出力される転送終了の制御信号Sを、光電変換素子13kの全てに入力する。

(もっと読む)

エネルギー線検出装置の製造方法

【課題】 信号電荷の収集効率を向上する。

【解決手段】 半導体基板の表面1000の第1区域1001の下に設けられた第1半導体領域131と、表面1000の第2区域1002の下に設けられ、接続部300に接続された第2半導体領域132と、表面1000の第1区域1001と第2区域1002との間の第3区域1003の下に設けられた第3半導体領域133とを有するエネルギー線変換装置の製造方法において、

第1半導体領域131及び第3半導体領域131を、第1区域1001及び第3区域1003を覆い、且つ、第3区域1003を覆う部分203の厚さが第1区域1001を覆う部分201の厚さよりも薄い緩衝膜200を介して、半導体基板100にイオン注入を行うことによって形成する。

(もっと読む)

放射線撮像装置、方法、および放射線撮像システム

【課題】 所望の回数の非破壊読み出しを行うことが出来ないフレームレート要求による動画像撮影を防止する放射線撮像装置を提供することを目的とする。

【解決手段】 入射した放射線を電気信号に変換して放射線画像を取得する放射線検出手段と、前記放射線検出手段で放射線動画像を取得する際のフレームレートの設定要求を取得する取得手段と、前記放射線検出手段による単位フレームごとの非破壊読み出し回数を設定する設定手段と、前記設定要求されたフレームレートにおいて、前記非破壊読み出し回数の読み出しが可能か否かを判定する判定手段と、前記判定手段による判定結果を出力する出力手段と、を有することを特徴とする。

(もっと読む)

フォトダイオードアレイモジュール及びその製造方法

【課題】 精密な計測が可能なフォトダイオードアレイモジュールを提供する。

【解決手段】 このフォトダイオードアレイモジュールは、第1波長帯域の光に感応する第1フォトダイオードアレイを有する第1半導体基板2と、第2波長帯域の光に感応する第2フォトダイオードアレイを有する第2半導体基板2’と、複数のアンプAMPが形成されると共に第1及び第2半導体基板2,2’が重なることなく横に並べ、各フォトダイオードをバンプを介してアンプAMPに接続した第3半導体基板3とを備えている。第1半導体基板2及び第2半導体基板2’の隣接する端部には、段差部が形成されており、これにより各画素を双方の基板に渡って連続して整列させた場合においても、低ノイズで計測ができるようになる。

(もっと読む)

固体イメージセンサおよびその製造方法

【課題】チップサイズ・パッケージを持ち、容易に製造することができる固体イメージセンサである。

【解決手段】受光素子層(20)の半導体基板(21)に複数の画素領域に対応して素子形成領域を形成し、それら素子形成領域内に半導体受光素子(PD)を形成して、透光性絶縁膜(25a)、(25b)、(26)で覆う。絶縁膜(26)上に、複数のマイクロレンズ(43)を内蔵した光導入用キャビティ(42)と、それを閉鎖する石英キャップ(51)を持つ光導入層(40)を形成する。半導体受光素子(PD)の出力電気信号は、半導体基板(21)の埋込配線を介してその底面に取り出し、出力層(10)またはインターポーザ(10A)を介して固体イメージセンサの外部に取り出す。

(もっと読む)

高ダイナミックレンジイメージセンサ

【課題】高ダイナミックレンジイメージセンサを提供する。

【解決手段】第1の基板12上に、複数の画素18であって、各画素が光検出器を有する画素と、前記複数の光検出器に接続する複数の読み出し回路であって、各読み出し回路が、この読み出し回路に接続する少なくとも1つの光検出器の充放電装置を有し、各充放電装置は、充放電の作動信号によって制御して前記読み取り回路に接続する各画素の前記光検出器の積分時間を課す回路とを有する。第1の基板12とは異なる第2の基板14を有し、この第2の基盤上には充放電装置の制御電子回路30、32、34を配置し、この回路は、第1の基板12と第2の基板14との間の電気接続16を介して充放電装置に転送するための充放電の作動信号を生成するように設計し、各画素または画素群は作動信号に接続して固有かつ適切な積分時間をこの画素または画素群に課す。

(もっと読む)

タイリング可能なセンサアレイ

【課題】大面積センサアレイを集積回路に接続しセンサ積層体を形成する方法を提供する。

【解決手段】第1の面16と第2の面18とを有しセンサアレイ14の第2の面上に配置された第1の複数の接触パッド20を含むセンサアレイを設け、第1の面と第2の面とを有し再配線層24の第1の面上に配置された第2の複数の接触パッド32を含む再配線層24と集積回路26の第1の面が再配線層の第2の面に作用的に結合されていて複数の貫通ビア30が貫設されている集積回路26とを含む相互接続層上にセンサアレイ14を配置し、センサアレイ14の第2の面上の第1の複数の接触パッドが再配線層の第1の面上の第2の複数の接触パッドと位置合わせされるようにセンサアレイ14を相互接続層上に配置し、センサアレイ14の第2の面上の第1の複数の接触パッドを再配線層24の第1の面上の第2の複数の接触パッドに作用的に結合してセンサ積層体を形成する。

(もっと読む)

イメージセンサモジュール及びイメージセンサ

【課題】共通信号ラインの電圧レベルの減衰を抑制する。

【解決手段】1つの実施形態によれば、イメージセンサモジュールは、光電変換部をそれぞれ有する複数のイメージセンサを有する。前記複数のイメージセンサに共通に接続され、前記複数のイメージセンサから順次に画像信号及びオフセット信号が出力される共通信号ラインを有する。前記複数のイメージセンサのうち最後に画像信号を出力すべきイメージセンサから、前記共通信号ラインへの画像信号及びオフセット信号の出力が完了したことをしめすタイミング信号を、前記複数のイメージセンサのうち前記共通信号ラインへオフセット信号を出力すべきイメージセンサへフィードバックするフィードバック部を有する。そして、前記オフセット信号を出力すべきイメージセンサは、前記フィードバック部によりフィードバックされた前記タイミング信号に応じて、前記共通信号ラインへ前記オフセット信号を出力する。

(もっと読む)

光学センサ、レンズモジュール、およびカメラモジュール

【課題】両面センサとして使用することが可能で、コスト増加を抑止しつつ、両面にウェハーレンズを貼り合わせた場合であっても取り出し電極を形成することが可能な光学センサ、レンズモジュール、およびカメラモジュールを提供する。

【解決手段】光学センサ10は、表面側に第1受光面111が形成され、裏面側に第2受光面112が形成され、第1受光面および第2受光面に被写体象を結像可能なセンサ基板11と、第1受光面側に配置された第1カラーフィルタ12と、第2受光面側に配置された第2カラーフィルタ13と、第1カラーフィルタを介して第1受光面側を支持する光学的に透明な透明支持板14と、を有し、第1カラーフィルタ12と第2カラーフィルタ13のレイアウトおよびサイズの少なくとも一方が異なる。

(もっと読む)

固体撮像装置および撮像システム

【課題】高画質化に有利な技術を提供する。

【解決手段】複数の行および複数の列を構成するように複数の画素が配列されるとともに複数の列信号線が配置された画素アレイを有する固体撮像装置において、前記複数の画素の各々は、半導体基板に形成された第1導電型の第1ウェルと前記第1ウェルの中に配置された前記第1導電型とは異なる第2導電型の不純物領域とを含む光電変換素子と、前記光電変換素子で発生した電荷に応じた信号を前記列信号線に出力する画素内読出回路とを含み、前記画素内読出回路は、前記第1導電型の第2ウェルに配置された回路素子を含み、前記第1ウェルと前記第2ウェルとが前記第2導電型の半導体領域によって分離されている。

(もっと読む)

固体撮像装置及び撮像システム

【課題】光電変換素子の面積が異なる画素を含む固体撮像装置において、画素間の感度のばらつきを低減する技術を提供することを目的とする。

【解決手段】光電変換素子をそれぞれ有する複数の画素と、光電変換素子を覆う遮光層とを備える固体撮像装置が提供される。遮光層は、複数の画素のそれぞれの光電変換素子に対して、当該光電変換素子への入射光の一部分を遮るための遮光部と、入射光の残り部分を通すための開口部とを有し、複数の画素は、光電変換素子の平面視における面積が異なる少なくとも2種類の画素を含み、光電変換素子の平面視における面積の大きい画素ほど遮光部の面積が大きい。

(もっと読む)

イメージセンサ用基板

【課題】 半導体基板に設ける位置合わせ用のアライメントマークの配置位置による制約を解消し、半導体基板同士の実装精度を向上させるイメージセンサ用基板を提供する。

【解決手段】 端子部4及び回路配線パターン1dを有して回路を形成した半導体基板1と、半導体基板1の長手方向に直線的に設けられ、光を光電変換する多数の光電変換部2と、光電変換部2から出力された電気信号を端子部4から出力する、光電変換部2と端子部4との間に設けられた駆動回路部3と、光電変換部2に選択的に配置され、光を透過させる光学波長の異なる複数の光学フィルタ5と、半導体基板1を載置するセンサ基板7と、センサ基板7に設けた基準マーク7aと、駆動回路部3の領域にある半導体基板1の回路配線パターン1dで形成された光反射パターン部6と、光反射パターン部6を除いて駆動回路部3を覆い、複数の光学フィルタ5が積層された光遮光膜とを備えるようにした。

(もっと読む)

画像撮影装置

【課題】複数の検出器ブロックを並べて光学的にしかも機械的に正確に配置することができ、ノイズの影響を受けにくい画像撮影装置を提供する。

【解決手段】X線100を発生するX線発生源を備える画像撮影装置10は、X線100を受けて光に変換するシンチレータ53と、光を電気信号に変換する光検出器54と、電気信号をデジタル信号に変換するデータ収集部55とを有する検出器ブロック52と、複数の検出器ブロック52を配列して固定する固定部材70と、基板63と、複数の検出器ブロック52の背面に略平行に挿通され、複数の検出器ブロック52におけるデータ収集部55の電気端子73と基板63とを電気的に接続する電気接続手段61と、を備える。

(もっと読む)

電気回路

【課題】物理長の異なる複数の伝送線路において、電気長を等しくする。

【解決手段】半導体基板1上の薄膜絶縁体上に形成された物理長の異なる複数の伝送線路A、Bのうち、物理長の長いほうの伝送線路において、伝送線路を構成する信号線メタルと半導体基板1との間に低誘電率絶縁膜3を挟むことによって信号伝搬速度を速くした領域を設け、この低誘電率絶縁膜3を挟んだ領域の長さを伝送線路Aの物理長に応じて調整することによって、すべての伝送線路の電気長を等しくする。

(もっと読む)

固定撮像素子

【課題】信号処理回路から熱によって、画素回路の性能が劣化することを抑制することができると共に、画素回路および信号処理回路とをそれぞれ最適な製造プロセスで製作することができる固定撮像素子を提供する。

【解決手段】固定撮像素子100は、第1主表面101および第2主表面102を含むガラス基板103と、集光部110および画素回路112を含む画素回路チップ113と、画素回路112からの信号を処理する信号処理回路が形成された信号処理回路チップ121とを備え、画素回路チップ113は、第1主表面101から間隔をあけて配置されると共に、集光部110が第1主表面101と対向するように配置され、信号処理回路チップ121は、第1主表面101に設けられると共に、集光部110とガラス基板103との間に位置する領域Rから離れた位置に配置される。

(もっと読む)

画像読取装置およびイメージセンサチップ

【課題】イメージセンサチップを長手方向に複数配列してなる1ラインのラインセンサにおいて、イメージセンサチップ間の光電変換素子の存在しない隙間部分に相当する欠損画素を補間する。

【解決手段】イメージセンサチップ1121の回路基板30の主走査方向における一方の端部に突出部31が形成され、回路基板30の主走査方向におけるもう一方の端部の、上記突出部31に対応する位置には後退部32が形成されており、イメージセンサチップ1121が主走査方向に複数直線状に並べられたときに、隣り合うイメージセンサチップ1121の突出部31と後退部32とは互いに嵌まり合う。当該突出部31上において、光電変換素子列40から副走査方向に所定距離離れた位置には、イメージセンサチップの繋ぎ目部分における画素欠陥領域の画素を補間するための補間用光電変換素子50が設けられている。

(もっと読む)

撮像素子モジュール

【課題】モジュール内のデッドスペースを活かしてその小型化に資することが可能な撮像素子モジュールを提供すること。

【解決手段】第1の面と第2の面とを有し、第1のランドを有する第1の配線パターンを第1の面側に備えた第1の配線板と、受光部と端子パッドを含む非受光部とを有する機能面を有し、該機能面が第1の配線板の側とは反対の側に向けられて第1の配線板の第1の面上に設けられた固体撮像素子チップと、第1の面と第2の面とを有し、第2のランドを有する第2の配線パターンを第1の面側に備え、第2の面から第1の面に至る端面上に被覆層を備え、第2の面の側が固体撮像素子チップの非受光部上に設けられた第2の配線板と、固体撮像素子チップの端子パッドと第1の配線板の第1のランドおよび/または第2の配線板の第2のランドとを電気的に接続するボンディングワイヤとを具備する。

(もっと読む)

放射線検出器及び放射線撮像装置

【課題】 モジュール間のギャップに因る信号歪が少なく、ギャップ分のデータ補間が容易で、且つ、製造も容易な放射線検出器を提供する。

【解決手段】X線検出器30は、シンチレータ31と、夫々が2次元に配列された画素を画成し、かつ夫々がシンチレータからの光信号を規定サイズの画素毎に電気信号に処理する処理回路を実装した回路基板32〜35と、を備える。シンチレータでは、所定サイズのシンチレータ要素を行方向及び列方向の少なくとも一方に2つ以上、平面状に配置される。シンチレータ及び回路基板の対を一つのモジュールとして、行方向及び列方向の少なくとも一方に2つ以上、平面状にかつ隙間を持たせて配置される。各モジュールは、互いに隣接する2つのモジュールの間に存在する隙間に因る画素不存在の領域が、規定サイズの隣接方向における値の整数倍になるように、前記規定サイズの前記隣接方向の値よりも小さい値に設定したサイズの画素の並びを当該隣接方向における最外側の端部に有する。

(もっと読む)

1 - 20 / 85

[ Back to top ]