Fターム[4M118DD12]の内容

Fターム[4M118DD12]に分類される特許

1 - 20 / 2,088

固体撮像素子およびその駆動方法、カメラシステム

固体撮像装置、カメラおよび固体撮像装置の設計方法

固体撮像装置

増幅回路および製造方法、撮像素子、並びに電子機器

半導体装置、半導体装置の製造方法、および電子機器

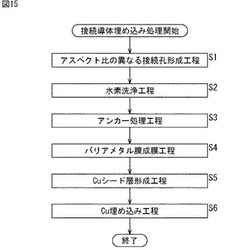

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

撮像素子

【課題】高解像度化した画素を有する撮像素子を提供する。

【解決手段】本発明の撮像素子10は、X,Y軸平面上に正方又は六方配置された各感光部101から蓄積電荷に相当する信号をZ軸方向に並列に抽出して出力する積層素子100a,100b,100c,100dと、この積層素子における感光部101を有する素子100aに対して設けられ、それぞれの感光部101に対して一部の領域を遮光するための当該感光部101の面積よりも小さい面積を有する1つの遮光部110を、当該感光部101の領域の範囲内で走査することにより各感光部101を所定の分割数で分割し、当該分割した各領域における遮光による蓄積電荷の変化量によって画素を形成する液晶素子106とを備える。

(もっと読む)

ハニカム構造の能動ピクセルセンサ

【課題】能動ピクセルセンサの色フィルタアレイを提供する。

【解決手段】それぞれが六角形の形状を有する複数個のフォトダイオードを備えたイメージセンサであって、前記イメージセンサは、さらに、前記複数個のフォトダイオードのうちの1つである第1フォトダイオードと、前記複数個のフォトダイオードのうちの2つである、前記第1フォトダイオードの側面に配置される第2及び第3フォトダイオードと、前記第1、第2及び第3フォトダイオード上に配置されるそれぞれの色フィルタと、を備え、前記第1、第2及び第3フォトダイオードの色フィルタは、相異なる色であることを特徴とする。

(もっと読む)

撮像装置及び電子機器

【課題】 静止画モード時にA/D変換時のセトリング期間を確保でき、画像信号の劣化を抑制できる撮像装置及び電子機器を提供する。

【解決手段】 撮像装置は、入射光を信号電荷に変換する光電変換部を有する複数の画素部と、前記信号電荷を蓄積し、信号電圧に変換するフローティングディフュージョン部と、前記信号電圧をデジタル信号に変換するアナログ・デジタル変換部と、リセットパルスが入力されることで、前記フローティングディフュージョン部に蓄積された信号電荷を破棄するリセット部と、前記画素部の信号電荷をそれぞれ信号電圧に変換する第1モードの場合、第1のLowレベルを有する第1のリセットパルスを生成し、前記複数の画素の信号電荷を加算して前記信号電圧に変換する第2モードの場合、前記第1のLowレベルより低い第2のLowレベルを有する第2のリセットパルスを生成して、前記リセット部に供給するリセットパルス生成部とを備える。

(もっと読む)

固体撮像装置および撮像装置

【課題】複数枚のチップを接続することによって構成される固体撮像装置において、回路規模の増大や、チップ間の接続部の数が増加することなく、それぞれのチップに形成された画素に制御信号を送ることができる固体撮像装置および撮像装置を提供する。

【解決手段】第1の基板と第2の基板とが接続部によって電気的に接続された固体撮像装置であって、第1の基板に配置された光電変換素子と第2の基板に配置された読み出し回路とを有する画素が2次元に複数配置された画素部と、画素からの信号の読み出しを制御する読み出し制御回路とを備え、読み出し制御回路は、パルス生成部と選択部とロジック部とを具備し、読み出し制御回路の構成要素の内、一部の構成要素を第1の基板内に配置し、残りの構成要素を第2の基板内に配置し、接続部を介して、第1の基板と第2の基板とに配置された読み出し制御回路の構成要素を電気的に接続する。

(もっと読む)

撮像装置

【課題】CMOS型イメージセンサを用いた撮像装置において、高輝度光が入射したときの横筋状又は横帯状のノイズの発生を抑制する。

【解決手段】複数の画素が二次元に配列され、光を受光する開口画素領域と、基準となる遮光されたオプティカルブラック領域とを含むCMOS型の撮像素子と、撮像素子の開口画素領域の特定の領域が高輝度被写体からの光を受光している場合の撮像素子の出力から得られる情報を予め記憶する記憶部と、開口画素領域の特定の領域が高輝度被写体からの光を受光しているか否かを判定する判定部と、判定部により特定の領域が高輝度被写体からの光を受光していると判定された場合に、記憶部に記憶された情報に基づいて、撮像素子からの出力を補正する補正部とを備える。

(もっと読む)

撮像装置

【課題】表示させる動画像に残像効果を持たせて、急激な構図変化をしたときであっても、主被写体を見失ってしまうことを防止する。

【解決手段】光電荷を生成し蓄積するフォトダイオード101と、前記フォトダイオードに接続され前記光電荷を転送する転送トランジスタ102と、前記転送トランジスタに接続された前記光電荷を蓄積する蓄積容量とを備え、前記フォトダイオードが光電荷を蓄積中に前記蓄積容量に蓄積された電荷のリセットを実行する第1の駆動モードと、電荷のリセットを非実行する第2の駆動モードとを有する。

(もっと読む)

リニアセンサ及び画像読み取り装置

【課題】ダーク成分やシェーディングの影響の抑制し、読み取り速度の高速化を図る。

【解決手段】リニアセンサ10は、1次元方向に配列された複数の第1光電変換部11aを有する第1センサ列12aと、1次元方向に配列された複数の第2光電変換部11bを有する第2センサ列12bと、各第1光電変換部から信号電荷を読み出して列方向に転送する第1水平転送部14aと、各第2光電変換部から信号電荷を読み出して列方向に転送する第2水平転送部14bと、第1水平転送部により転送された信号電荷を検出して出力し、第2水平転送部により転送された信号電荷を検出して出力する出力部18とを備える。第1光電変換部11aは光が入射する開口を有する受光センサであり、第2光電変換部は光が入射する開口が塞がれた遮光センサであり、各遮光センサは各々対応する受光センサに隣接して設けられ、第1センサ列と第2センサ列とが並列に設けられて構成される。

(もっと読む)

走査回路、固体撮像装置およびカメラ

【課題】構成の単純化およびモードの多様化に有利な技術を提供する。

【解決手段】走査回路は複数の単位回路を直列に接続して構成されたシフトレジスタと、シフトレジスタを制御する制御部とを備える。各単位回路はパルス信号入力端子と、パルス信号出力端子と、制御端子とを含む。単位回路は複数にグループ分けされている。制御部は、第1モードでは複数のグループの単位回路の制御端子にクロック信号を供給することによりパルス信号をシフトするように動作させ、第2モードでは少なくとも1つのグループの単位回路の制御端子にはバッファとして動作させる論理レベルを供給し、他のグループの単位回路の制御端子にはクロック信号を供給することにより前段の単位回路から出力されるパルス信号をクロック信号に応じて後段の単位回路に転送するように動作させ、1つの期間内に少なくとも1つのグループの単位回路とその前段の単位回路からパルス信号を出力させる。

(もっと読む)

焦電型光検出器、焦電型光検出装置および電子機器

【課題】焦電型光検出器の検出出力を高めること。

【解決手段】焦電型光検出器は、基板10と、基板上に支持される支持部材215と、支持部材に接して形成されている焦電型光検出素子251と、を有する。焦電型光検出素子251は、支持部材側に設けられる第1電極234と、第1電極と対向して設けられ、平面視における面積が、第1電極より小さい第2電極236と、第1電極234と第2電極236との間に設けられる焦電体232と、を含むキャパシター230を有する。焦電型光検出素子251はさらに、キャパシター上に形成されている光吸収層270を含む。平面視における光吸収層の面積を受光部面積Aaとし、平面視における第2電極の面積をキャパシター面積Acとし、Aa/Acは、2.0<Aa/Ac<49.0を満足する。

(もっと読む)

固体撮像装置、撮像装置、および信号読み出し方法

【課題】複数の基板の面積を有効に活用する。

【解決手段】本発明の一態様に係る固体撮像装置は、第1〜第n(nは2以上の整数)の基板どうしが接続部を介して電気的に接続された固体撮像装置であって、光電変換素子を含む画素が行列状に配置された画素部と、前記画素部内の画素の列に対応して配置され、対応する列の画素に含まれる前記光電変換素子で発生した信号を信号処理する複数の列処理回路を含む列回路部と、前記列処理回路によって信号処理された信号を当該装置の外部に出力する出力部と、を備え、前記第1の基板に前記画素部が配置され、前記第1〜第nの基板のうち少なくとも2以上の異なる基板のそれぞれに前記列回路部が配置され、前記画素部内の各列の画素に対応する信号処理を、前記少なくとも2以上の異なる基板のそれぞれに配置された前記列回路部で分散して行うことを特徴とする。

(もっと読む)

固体撮像装置

【課題】TDI動作によって撮像を行う際に、撮像に要する時間を短くすることができる固体撮像装置を提供する。

【解決手段】固体撮像装置1Aは、M×N個(M,Nは2以上の整数)の画素がM行N列に2次元配列されて成る撮像面12、撮像面12に対して列方向の一端側に各列毎に配置されたN個の信号読出回路20、及び、撮像面に対して列方向の他端側に各列毎に配置されたN個の信号読出回路30を有するCCD型の固体撮像素子10と、信号読出回路20から各列毎に出力される電気信号をディジタル変換したのちシリアル信号として順次出力する半導体素子50と、信号読出回路30から各列毎に出力される電気信号をディジタル変換したのちシリアル信号として順次出力する半導体素子60とを備える。

(もっと読む)

固体撮像素子およびカメラシステム

【課題】チップ内の熱勾配を緩和することが可能で、ひいてはダークシェーディングを緩和することが可能な固体撮像素子およびカメラシステムを提供する。

【解決手段】第1チップは画素アレイ部が配置され、第2チップはロジック部およびレギュレータが配置され、レギュレータは、基準電圧を生成する基準電圧生成部と、複数の出力段トランジスタと、基準電圧と複数の出力段トランジスタの共通化された出力電圧を比較する演算増幅器とを含み、演算増幅器の出力は複数の出力段トランジスタのゲートに接続され、出力段トランジスタの出力経路は一つのノードに接続され、演算増幅器にフィードバックされ、複数の出力トランジスタの電源側端子は外部電源電圧が供給される供給電源端子に接続され、演算増幅器は、基準電圧と複数の出力段トランジスタのノードで共通化された出力電圧を比較して複数の出力段トランジスタのゲート電圧を制御する。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

固体撮像装置およびカメラ

【課題】感度差の低減に有利な技術を提供する。

【解決手段】複数の画素ユニットを有する固体撮像装置において、各画素ユニットは、複数の画素と、前記複数の画素によって共用される電荷電圧変換部とを含み、各画素は、半導体基板に形成された光電変換素子を含む。前記固体撮像装置は、複数の配線層と、層間絶縁膜と、前記層間絶縁膜の屈折率よりも高い屈折率を有する材料を前記層間絶縁膜における各光電変換素子の上方に埋め込んで構成された光導波路とを含む構造部を前記半導体基板の上に有し、各画素ユニットの前記複数の画素は、第1画素と第2画素とを含み、前記第1画素の前記光電変換素子の上方に配置された前記光導波路の周辺の構造と前記第2画素の前記光電変換素子の上方に配置された前記光導波路の周辺の構造との相違による前記第1画素の感度と前記第2画素の感度との差を低減するようにダミーパターンが前記構造部に設けられている。

(もっと読む)

撮像素子およびカメラシステム

【課題】センス回路の高速化や消費電力の増加を伴うことなく、低照度時と高照度時においてノイズの少ない高精度な撮像が可能な撮像素子およびカメラシステムを提供する。

【解決手段】光電変換素子と蓄積部と、蓄積電荷を電気信号として出力するアンプ素子とを有し、光子入射に応じて電気信号を出力信号線に出力する画素が、複数アレイ状に配置された画素アレイ部と、画素からの電気信号を受けて、所定期間における画素への光子入射の有無を判定するセンス回路を含むセンス回路部と、を有し、センス回路は、出力信号線に接続されたAD変換装置を含み、AD変換装置は、少なくともバイナリ判定である1ビット出力と多ビット解像度による階調出力の2モードで動作可能であり、少なくとも1ビット出力モードの選択時は、画素ごとに複数回の露光における出力結果が集積されて、各画素に入射した光の強度が算出される。

(もっと読む)

1 - 20 / 2,088

[ Back to top ]