Fターム[4M118FA28]の内容

固体撮像素子 (108,909) | CCD、MOS型固体撮像素子の細部 (13,257) | 分離構造 (2,603) | 絶縁物による分離 (743)

Fターム[4M118FA28]に分類される特許

1 - 20 / 743

固体撮像素子

半導体装置、半導体装置の製造方法、および電子機器

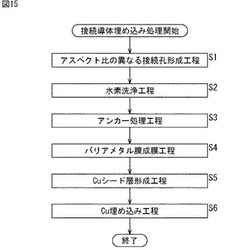

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

固体撮像装置及びその製造方法

【課題】フォトダイオードに蓄積された電荷をより正確に読み出す。

【解決手段】固体撮像装置は、半導体基板11と、半導体基板11内に設けられ、第1導電型の半導体層を有するフォトダイオード16と、フォトダイオード16上に設けられ、上部又は全体が第2導電型の半導体層からなるシールド層27と、半導体基板11に設けられ、フォトダイオード16に蓄積された電荷を浮遊拡散層に転送する転送トランジスタ20とを含む。シールド層27の上面は、半導体基板11の上面より高い。

(もっと読む)

固体撮像素子および製造方法、並びに、電子機器

【課題】良好な感度特性およびスミア特性を両立する撮像機能を備えた電子機器を提供する。

【解決手段】画素21は、全ての画素21において同時に光電変換部31で発生した電荷をメモリ部33に転送し、メタルゲート61、62を有する転送部32、34と、転送部32、34の周囲の層間絶縁膜67を掘り込むことにより形成された溝部にメタル66を埋め込むことにより形成される遮光部とを有する。また、遮光部は、その先端部が、転送部の周囲において、層間絶縁膜67と半導体基板51との間に形成されるライナー膜65の膜厚よりも半導体基板側に突出するように形成される。

(もっと読む)

固体撮像素子

【課題】画素部の金属汚染や受光部の光電変換素子表面へのRIEによるダメージの発生を抑制することができる固体撮像素子を提供する。

【解決手段】実施形態によれば、固体撮像素子は、所定の波長の光を透過させるカラーフィルタ51L,51M,51Sと、カラーフィルタ51L,51M,51Sを透過する光を検出するフォトダイオードPDと、を含む画素PL,PM,PSを、異なる波長の光を検出するように複数有する絵素が、所定の周期で2次元的に基板11上に配置される。絵素中の最も長い波長の光を検出する画素PLは、基板11の光の入射面と対向する面側のフォトダイオードPD上に設けられる保護膜12と、保護膜12上に設けられ、厚さ方向に貫通する円柱状の孔が2次元的に配置される回折格子部20Lと、を備える。回折格子部20Lは、画素PLに設けられるカラーフィルタ51Lを透過する光を反射させるように孔の径と配置される周期が選択される。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

固体撮像素子ウエハ、固体撮像素子の製造方法、および固体撮像素子

【課題】裏面照射型の固体撮像素子を備えたチップ領域が複数配列された固体撮像素子ウエハにおいて、個片化されるチップ領域のサイズを縮小し、これにより固体撮像素子の小型化を図る。

【解決手段】複数のチップ領域200と、チップ領域200を囲んで配置された分割領域300と、各チップ領域200に設けられた光電変換部20と、各チップ領域200において光電変換部20に対する受光面Aとは逆の表面側に設けられた駆動回路と、駆動回路に接続され各チップ領域200において表面側に引き出されたデバイス用端子33と、駆動回路に接続され分割領域300において受光面A側に露出された検査用端子400とを備えた固体撮像素子ウエハ100−1である。

(もっと読む)

固体撮像装置およびその製造方法

【課題】ランダムノイズを低減する。

【解決手段】固体撮像装置は、基板上に形成され、光電変換部(PD)と複数の画素内トランジスタとからなる画素が2次元配列された画素アレイを備え、複数の画素内トランジスタのうちの所定の画素内トランジスタの電極、具体的には、増幅トランジスタのゲート電極のみに接続されるコンタクトの基板に平行な面の形状は、略長方形または略楕円形に形成される。本技術は、CMOSイメージセンサに適用することができる。

(もっと読む)

光電変換装置および撮像システム

【課題】 良好な性能を有する光電変換装置を提供する

【解決手段】 光電変換部110を覆うとともに、転送ゲート120の転送ゲート電極121の光電変換部110側の側面に沿って延在して転送ゲート電極121の上面1210を覆う第1保護膜220を備え、第1保護膜220と光電変換部110との間に、第1保護膜220の屈折率及び光電変換部110の屈折率よりも低い屈折率を有し、第1保護膜220と界面を成す第1領域11が設けられ、第1保護膜220と転送ゲート電極121の上面1210との間に、転送ゲート電極121の屈折率及び第1保護膜220の屈折率よりも低い屈折率を有し、第1保護膜220と界面を成す第2領域22が設けられており、第1領域11の光学膜厚をT1、第2領域22の光学膜厚をT2、光電変換部110へ入射する光の波長をλとして、T1<T2<λ/2−T1を満たす。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】裏面照射型の固体撮像装置において、受光面と遮光膜との距離を小さくすることにより、光電変換部での受光特性の向上を図る。

【解決手段】光電変換部が配列形成された画素領域を有するセンサ基板と、センサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、画素領域における受光面上に設けられた遮光膜と、遮光膜を覆って設けられた保護絶縁膜と、画素領域の外側の周辺領域において、保護絶縁膜からセンサ基板にかけて埋め込まれ駆動回路に接続された複数の貫通ビアを備えた固体撮像装置。

(もっと読む)

固体撮像素子およびその製造方法、電子情報機器

【課題】受光部への光入射効率を悪化させることなく、金属コンタミネーション起因による白傷を低減する。

【解決手段】複数の受光部3の上方で、パターニングされた3層の導電層(ここでは金属層の第3配線7c)上の第4絶縁膜6d上に、装置側で設定するプラズマ発生エネルギーを示すRFパワーを、金属コンタミネーション起因による白傷を抑制するように700W〜1500Wに設定するプラズマCVD法によりパッシベーション膜8を成膜するパッシベーション膜成膜工程と、熱処理によりパッシベーション膜8から水素を脱離させるシンター処理を行うシンター処理工程とを有している。このパッシベーション膜8は、その膜厚が50〜100nmである。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の不純物濃度を好適に制御する半導体装置の製造方法を提供する。

【解決手段】第2トランジスタ170のゲート電極171を半導体基板1に対するマスクとして半導体基板1へイオン注入を行うことにより、第2トランジスタのドレイン175を形成するとともに、第2トランジスタ170のゲート電極171へイオン注入を行う。

(もっと読む)

半導体装置の製造方法

【課題】高いスループットで製造するために有利な製造方法を提供する。

【解決手段】第1領域101および第2領域102を有する半導体基板において、第1絶縁膜112、第2絶縁膜113および第3絶縁膜122を貫通する第1コンタクトホール形成工程と、第4絶縁膜120、第5絶縁膜121および第6絶縁膜122を貫通する第2コンタクトホール形成工程とを含み、前記第1,3,4,6絶縁膜は第1組成を有し、前記第2,4絶縁膜は前記第1組成とは異なる第2組成を有し、開口工程では、前記第2絶縁膜をエッチングストッパとして前記第3絶縁膜をエッチング後に、前記第2絶縁膜および前記第1絶縁膜を互いに異なるエッチング条件で第1コンタクトホールを形成し、前記第5絶縁膜をエッチングストッパとして前記第6絶縁膜をエッチング後に、前記第5,4絶縁膜を同一のエッチング条件で連続的にエッチングして、前記第2コンタクトホールを形成する。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】受光面側にパッド配線を設けた裏面照射型の固体撮像装置において、絶縁膜の薄膜化を図ることにより光電変換部での受光特性の向上を図ることが可能な裏面照射型の固体撮像装置を提供する。

【解決手段】このような目的を達成するための本技術の固体撮像装置は、光電変換部が配列形成された画素領域を有するセンサ基板を備え、このセンサ基板において光電変換部に対する受光面とは逆の表面側には駆動回路が設けられている。また画素領域の外側の周辺領域には、センサ基板における受光面側から駆動回路に達しする貫通ビアが設けられている。さらに、周辺領域の受光面側には、貫通ビア上に直接積層されたパッド配線が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】歩留まりの向上、およびコスト削減を図る。

【解決手段】半導体装置は、デバイス基板600と、前記デバイス基板上に接合された支持基板200と、を具備する。前記デバイス基板は、前記支持基板との接合面側の外周部に溝50を有する。

(もっと読む)

光電変換装置及び撮像システム

【課題】既存のCMOS形成製造方法を用いながら、撮像性能向上に寄与するPD形成用ウエル構造を実現する。

【解決手段】光を信号電荷に変換する光電変換領域を含む画素と、該画素が形成された画素領域外に、前記信号電荷を処理するための回路を含む周辺回路が同一基板上に配置された光電変換装置において、前記基板に形成された第一導電型の第1の半導体領域と前記信号電荷と同導電型である第二導電型の第2の半導体領域を含んで前記光電変換領域が形成され、第一導電型の第3の半導体領域を含んで前記周辺回路が形成されており、前記第1の半導体領域の不純物濃度は前記第3の半導体領域の不純物濃度よりも高い。

(もっと読む)

画素をバーストリセット動作と統合することにより改善された性能を有するCMOSイメージセンサ

【課題】小型画素及び高性能CMOSイメージセンサアレイで使用することができる実質

的な画素設計を提供すること。

【解決手段】本発明のリセットトランジスタは、電荷を検出するフローティング拡散領域

と、電荷を排出する接合領域と、リセット信号の制御を受けて、前記フローティング拡散

領域から前記接合領域への電荷転送を制御するゲートと、該ゲートの下部に統合された電

位井戸とを備えることを特徴とする。

(もっと読む)

固体撮像装置

【課題】記憶部で発生するリーク電流の量を抑制した固体撮像装置を提供する。

【解決手段】前記固体撮像装置は、半導体基板70に配置される複数の画素部と、複数の記憶部と、垂直走査回路6とを備える。前記半導体基板70内には、第一導電型のウエル61が形成される。前記複数の記憶部の各々は、ウエル61に形成される書き込みトランジスタ31を有する。ウエル61と、書き込みトランジスタ31のソース又はドレインである第二導電型の前記拡散領域72とは接合される。垂直走査回路6は、前記記憶部に画素信号を記憶させるための記憶期間中に、ウエル61と前記拡散領域72との接合部の電界強度を低減させる所定電圧を、ウエル61に印加する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能向上を図ることができる技術を提供する。

【解決手段】層間絶縁膜を形成した後、マイクロ波アニールを実施する。このマイクロ波アニールによれば、シリコン結晶に共鳴吸収される周波数(5.8GHz)のマイクロ波を使用することにより、シリコン結晶の格子振動を直接誘起するため、例えば、400℃以下という低温においても、半導体基板の内部に形成されている結晶欠陥を回復させることができる。

(もっと読む)

イメージセンサのピクセル縮小のためのコンタクト構造及びその製造方法

【課題】フィルファクターの低下なしで、ピクセル縮小が可能なイメージセンサ及びその製造方法を提供する。

【解決手段】イメージセンサのピクセルは、ピクセル内に互いに電気的に接続が必要なポリシリコン402と活性領域401を有するイメージセンサにおいて、前記ポリシリコン膜が、前記活性領域の上部に一部が重なるように拡張され、前記ポリシリコン膜が、前記活性領域と埋没コンタクト403されるようにする。

(もっと読む)

1 - 20 / 743

[ Back to top ]