Fターム[4M118FA29]の内容

固体撮像素子 (108,909) | CCD、MOS型固体撮像素子の細部 (13,257) | 分離構造 (2,603) | フィールドシールド電極による分離 (12)

Fターム[4M118FA29]に分類される特許

1 - 12 / 12

光検出素子、光検出素子の制御方法

【課題】光電変換部での飽和の可能性を低減して光電変換部の小型化を可能にし、全体としてのサイズの小型化を可能にする。

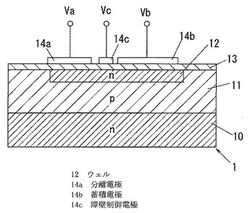

【解決手段】分離電極14aと蓄積電極14bとが障壁制御電極14cを挟んで配置される。分離電極14aと蓄積電極14bと障壁制御電極14cとに正極性の電圧が印加されてウェル12にポテンシャル井戸が形成された状態で光照射による電子が集積される。その後、障壁制御電極14cに印加された電圧に応じて形成されるポテンシャル障壁の高さが調節されることにより、規定した一定量の不要電荷が電荷分離部で分離される。電子の集積と不要電荷の分離とが複数回繰り返された後、蓄電電極14bに対応して形成された電荷蓄積部に流れ込んだ有効電荷が受光出力として取り出される。

(もっと読む)

光検出素子、光検出素子の制御方法、空間情報の検出装置

【課題】光照射により電荷を生成する過程で電荷量を調節することにより光電変換部の小型化を可能にし、全体としてのサイズの小型化が可能になる光検出素子を提供する。

【解決手段】分離電極14aと蓄積電極14bとが障壁制御電極14cを挟んで配置される。分離電極14aと蓄積電極14bと障壁制御電極14cとに正極性の電圧を印加してウェル12にポテンシャル井戸を形成した状態で受光し、光照射による電子を集積する。その後、障壁制御電極14cの電圧を制御して、ポテンシャル井戸を電荷分離部と電荷蓄積部とに2分し、電荷分離部の電荷を廃棄し、さらに、電荷蓄積部から電荷分離部に電荷を転送する。その後、障壁制御電極14cに印加した電圧に応じて形成されるポテンシャル障壁の高さを調節することにより、規定した一定量の不要電荷を電荷分離部で分離し、ポテンシャル障壁を越えて電荷蓄積部に流れ込んだ有効電荷を受光出力として取り出す。

(もっと読む)

固体撮像素子及びその製造方法

【課題】微細化に対応することができると共に、画質劣化を抑制することができるCMOS型固体撮像素子及びその製造方法を提供する。

【解決手段】N型シリコン基板1にトレンチ加工が施されて設けられた溝部に、ホウ素を含んだアモルファスシリコンが埋め込まれて形成された素子分離層2を備えるCMOS型固体撮像素子であって、素子分離層には負電圧が印加される様に構成する。

(もっと読む)

固体撮像装置及びその製造方法

【課題】 飽和特性や感度特性を低下させることなく画素セルを微細化した固体撮像装置及びその製造方法を提供する。

【解決手段】 画素分離のためのトレンチ203の側壁に設けられた欠陥抑制層205とフォトダイオード208との境界部分に反転層209を設ける。欠陥抑制層205はP型となっており、フォトダイオード208と反転層209とはN型となっている。ここで、反転層209の不純物濃度はフォトダイオード208の不純物濃度の2倍以上である。

(もっと読む)

固体撮像素子及びその製造方法

【課題】 電荷蓄積領域の実効面積を犠牲にすることなく単位画素の微小化を可能とする固体撮像素子及びその製造方法を提供する。

【解決手段】 基板上に所定の開口を有するハードマスクを形成する工程と、前記基板に前記開口側に一部延長し、該延長部分が主要部分と異なる不純物濃度を有する前記画素を構成する第1導電型の電荷蓄積領域を形成する工程と、前記電荷蓄積領域の延長部分の、少なくとも一部の第1導電型不純物濃度を、前記電荷蓄積領域の主要部分の形成とは独立に制御する工程と、前記開口下に形成された前記拡散層に接するように、前記開口内に前記絶縁膜を形成する工程とによって固体撮像素子を製造する。

(もっと読む)

フォトダイオード領域を埋め込んだイメージセンサ及びその製造方法

【課題】 実質的な開口率を高くし且つ光感度を向上させたCMOSイメージセンサとその製造方法を提供する。

【解決手段】 フォトダイオードとリセットトランジスタとソースフォロワトランジスタとを有するピクセルを複数形成されるイメージセンサであって,各ピクセルは,フォトダイオードとリセットトランジスタとの間に電荷転送用のトランスファーゲートトランジスタを有し,リセットトランジスタとトランスファーゲートトランジスタとの接続ノードであるフローティング・ディフュージョン領域がソースフォロワトランジスタのゲートに接続される。そして,各ピクセルのリセットトランジスタ及びソースフォロワトランジスタが形成されるウエル領域の下に,フォトダイオード領域が埋め込まれる。さらに,フォトダイオード領域は,フローティング・ディフュージョン領域の少なくとも一部領域の下には形成されていない。

(もっと読む)

固体撮像素子

【課題】フォトダイオードの開効率の低下を招くことなく、低電圧を使用してブルーミングを抑制すること。

【解決手段】フォトダイオード部21とフローティングディフュージョン部22を有する画素の周りで素子分離絶縁膜27の下側にオーバーフローパス領域28を形成し、このオーバーフローパス領域28の不純物濃度をN型シリコン基板25方向に変化させてポテンシャル勾配を形成することにより、低電圧のCMOSプロセスでも、オーバーフローパス領域28に周囲のP型ウエル領域26よりも低いポテンシャルを付与でき、フォトダイオード部21から溢れた電荷を捕らえてN型シリコン基板25に排出することによって、フォトダイオード部21の開効率の低下を招くことなく、低電圧を使用してブルーミングを抑制することができる。

(もっと読む)

半導体装置とその製造方法、並びに固体撮像素子とその製造方法

【課題】 マスク微細化の限界を超えた領域上へのマスク形成を可能にし、工程削減を可能し、信頼性の向上を図った固体撮像素子を含む半導体装置、及びその製造方法提供する。

【解決手段】 不純物領域による素子分離領域23を有し、素子分離領域23上にイオン注入阻止用マスク29が残存して成る。イオン注入阻止用マスク29は、半導体素子の構成要素、例えばMOSトランジスタのゲート制御部25と同じ構成で形成される。

(もっと読む)

固体撮像素子

【課題】 同一画素内のシールド電極用のコンタクト部とP型ウェル領域用のコンタクト部を形成する場合にコンタクト部の配置面積を縮小して、画素の微細化や撮像特性の向上を図る。

【解決手段】 同一画素内のシールド電極用のコンタクト部とP型ウェル領域用のコンタクト部を共用コンタクト部によって形成する。具体的には、シリコン基板のフォトダイオードを設けたP型ウェル領域の上部に素子分離部の絶縁層及び埋め込みシールド電極を設け、絶縁層の底面に形成した開口部を通してシールド電極の一部がP型ウェル領域の上面に設けた高濃度拡散領域に接触するようにし、シールド電極とP型ウェル領域とが導通した状態に形成し、この素子分離部の上部に共用コンタクト部のプラグを設ける。

(もっと読む)

光電変換装置、固体撮像装置及び固体撮像システム

【課題】 隣接する光電変換素子間の暗電流差がなく又は暗電流差が小さい、高速読み出しをした際にも高感度でかつ低暗電流な固体撮像装置を得る。

【解決手段】 ウエハ基板301上にウエル302を設け、ウエル内に拡散層101a,101bを形成してフォトダイオードを構成する。拡散層101a,101b 間にウエルコンタクト306を形成する。ウエルコンタクトと拡散層間に素子分離領域303b,303aを設け、素子分離領域303b,303aの下にチャネルストップ層307b,307aを設ける。素子分離領域303b上に導電層304を設け、導電層304の側面にサイドウォール308を設ける。素子分離領域303bの端部と導電層304間の距離をa、サイドウォール308の幅をb、素子分離幅をcとすると、c>a≧bなる関係を有する。

(もっと読む)

光電変換装置、固体撮像装置及び固体撮像システム

【課題】 隣接する光電変換素子間の暗電流差がなく又は暗電流差が小さい、高速読み出しをした際にも高感度でかつ低暗電流な固体撮像装置を得る。

【解決手段】 ウエハ基板301上にウエル302を設け、ウエル内に拡散層101a,101bを形成してフォトダイオードを構成する。拡散層101a,101b 間にウエルコンタクト306を形成する。ウエルコンタクトと拡散層間に素子分離領域303b,303aを設け、素子分離領域303b,303a上の両方に導電層304,305を設ける。素子分離領域303b,303a上の両方に導電層304,305を設けることで、ウエルコンタクトからフォトダイオード(拡散層)への少数キャリアの拡散の差を少なくする。

(もっと読む)

固体撮像装置及び固体撮像装置を用いたカメラシステム

【課題】 信号電荷がフォトダイオード以外の領域に吸収され難く、隣接するフォトダイオードへの信号電荷の漏れこみを低減する。

【解決手段】 本発明は、第1導電型よりなる第1の半導体領域と、第2導電型よりなる第2の半導体領域と、前記第2の半導体領域より不純物濃度が低い第2導電型よりなる第3の半導体領域と、第1導電型よりなる第4の半導体領域と、を光入射側より順に設けた光電変換部と、

第2導電型のソースおよびドレイン領域と、を有するトランジスタと、を有する画素の複数と、隣接する前記画素間に配された素子分離領域と、を有し、前記トランジスタのゲート電極の下部に配された第1導電型の第5の半導体領域と、前記素子分離領域下に配された第1導電型の第6の半導体領域とを有し、前記第3の半導体領域は、前記第4の半導体領域と、前記第5の半導体領域と、前記第6の半導体領域と、により囲まれていることを特徴とする。

(もっと読む)

1 - 12 / 12

[ Back to top ]