Fターム[4M118FA32]の内容

固体撮像素子 (108,909) | CCD、MOS型固体撮像素子の細部 (13,257) | 受光部から転送部への電荷移送 (3,593) | 素子形態 (3,076)

Fターム[4M118FA32]の下位に属するFターム

Fターム[4M118FA32]に分類される特許

1 - 20 / 22

リニアセンサ及び画像読み取り装置

半導体装置の駆動方法

【課題】グローバルシャッタ方式で電荷の蓄積を行うイメージセンサにおいて、蓄積期間

終了時から最後の行を読み出すまでの期間、蓄積電荷保持部からの電荷の流出を極力抑制

することのできる半導体装置の提供を目的とする。

【解決手段】画素がマトリクス状に複数配置されたCMOSセンサ型のイメージセンサに

おいて、画素部の電荷蓄積制御トランジスタ及びリセットトランジスタにチャネル形成領

域が酸化物半導体で形成されたトランジスタを使用し、マトリクス状に配置された全ての

画素で信号電荷蓄積部のリセット動作を行った後、全ての画素でフォトダイオードによる

電荷の蓄積動作を行い、行毎に画素から信号の読み出し動作を行うことで歪みの無い撮像

を可能とする。

(もっと読む)

固体撮像装置とその製造方法、及び電子機器

【課題】半導体基板の受光面側に形成された光電変換部を有する固体撮像装置において、画素の微細化を損なうことなく転送効率が向上された固体撮像装置、及びその製造方法を提供する。また、その固体撮像装置を用いた電子機器を提供する。

【解決手段】半導体基板内に、縦方向に積層された接続部21、電位障壁層22、電荷蓄積層23からなる縦型転送路50を形成する。半導体基板17の裏面側には、下部電極31及び上部電極33に挟持された光電変換部32が形成されており、下部電極31と接続部21は、コンタクトプラグ29により電気的に接続されている。これにより、光電変換部で生成された信号電荷は、コンタクトプラグ29を介して接続部21に読み出され、電荷蓄積層23に縦方向にオーバーフローされる。

(もっと読む)

固体撮像素子およびその駆動方法

【課題】裏面を入射光の受光面とした裏面照射型の固体撮像素子において、残像、クロストーク等の発生を防止すること。

【解決手段】半導体基板10内において裏面から表面に向かう順に、P型の受光表面層12と、光電変換された信号電荷を蓄積するN型のフォトダイオード11と、P型の電位障壁層14と、フォトダイオード11から転送される信号電荷を蓄積するN型の電荷蓄積層13を設ける。フォトダイオード11から電荷蓄積層13に信号電荷を転送するとき以外には、裏面バイアス発生回路7により受光表面層12に0Vの電圧が印加され、信号電荷の転送時には、負のパルス信号が印加される。

(もっと読む)

光電変換装置及び撮像システム

【課題】光電変換部から電荷電圧変換部への電荷の転送効率を向上するとともに、転送電極の下における素子分離部の界面準位に起因した暗電流によるノイズを低減する。

【解決手段】アクティブ領域を規定する素子分離部EIと、第1導電型の電荷蓄積領域14を含む光電変換部51と、電荷電圧変換部53と、光電変換部51で発生した電荷を電荷電圧変換部53へ転送するための転送電極2と、光電変換部51と電荷電圧変換部53との間の第1導電型の第1の半導体領域12と、第1の半導体領域12と素子分離部EIとの間の第1導電型と反対導電型である第2導電型の第2の半導体領域11とを備え、第2の半導体領域11は、転送電極2の下におけるチャネル幅方向に沿って延びた第4の部分11cと、転送電極2の下におけるチャネル長方向に沿って延びた第3の部分11dとを含み、第4の部分11cの幅は、第3の部分11dの幅より広い。

(もっと読む)

固体撮像素子

【課題】 従来よりも受光感度が向上する固体撮像素子を提供する。

【解決手段】 固体撮像素子において、半導体基板10と、半導体基板10の表面及びその近傍に形成された第1のウエル13と、半導体基板10の表面及びその近傍に第1のウエル13を囲って形成された第2のウエル12と、半導体基板10の表面及びその近傍に第2のウエル12を囲って形成された第3のウエル11と、少なくとも第1〜第3のウエル13〜11のいずれかの表面から突出する細長形状部15と、細長形状部15が突出する表面及びその近傍に、細長形状部15に離間して形成されたドレイン16と、を備えている。細長形状部15は、その先端部に設けられたソース33と、細長形状部15が突出する表面とソース33との間の領域にソース33に離間して設けられたゲート31と、を有する。

(もっと読む)

固体撮像素子およびその駆動方法

【課題】センサラインの間隔を狭くしたとしても色ずれの発生を防止することが可能な固体撮像素子およびその駆動方法を提供する。

【解決手段】センサライン110,120,130は、複数の画素が第1ピッチをもってリニアに配列されたセンサ列111,121,131と、センサ列の各画素で光電変換された信号電荷を読み出す読み出しゲート112,122,132と、読み出しゲートより読み出された信号電荷を出力部側に転送する水平転送レジスタ114,124,134と、読み出しゲートにより読み出された信号電荷を、アクティブの保持信号Vgate1,Vgate2,Vgate2を受けている期間保持して水平転送レジスタに供給するメモリレジスタ113,123,133とを有し、駆動部170は各センサライン110,120,130に信号電荷の保持期間を設定可能に保持信号Vgate1,Vgate2,Vgate2を生成する。

(もっと読む)

固体撮像素子

【課題】多チャンネル出力方式を有する全画素読み出し方式の固体撮像素子において、多画素化及び高フレームレート化の要求に対応するために、出力アンプのゲインレベルの調整を容易に行えるようにすると共に、画質劣化を抑制する。

【解決手段】多数マトリクス状に配された受光部2と、各受光部2に対応して垂直2画素×水平2画素の配列規則で配されたカラーフィルタと、対応する受光部2の両側に夫々分離して配された、第1の垂直転送レジスタ3及び第2の垂直転送レジスタ3と、その一端に設けられた4つの水平転送レジスタ5A,5B,5C,5Dとを含み、2つの水平転送レジスタ5A,5Dと、他の2つの水平転送レジスタ5B,5Cとは、信号電荷の転送方向が互いに逆方向とされている固体撮像素子111を構成する。

(もっと読む)

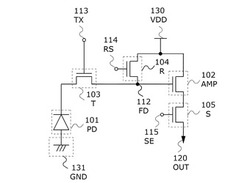

二つのゲートからなるセンシングトランジスタを備えたイメージセンサー及びその駆動方法

【課題】二つのゲートからなるセンシングトランジスタを備えたイメージセンサー及びその駆動方法を提供する。

【解決手段】光電変換領域と、光電変換領域からの電荷が保存されるフローティング拡散領域に連結された第1ゲート及び該第1ゲートと離隔された第2ゲートを備えたセンシングトランジスタと、フローティング拡散領域に連結され、フローティング拡散領域の電位をリセットするリセットトランジスタと、第2ゲートに印加される制御電圧を供給する制御電圧源と、センシングトランジスタのソースに連結されたカラム出力ラインと、を備える二つのゲートからなるセンシングトランジスタを備えたイメージセンサーである。

(もっと読む)

イメージセンサー及びその製造方法

【課題】フォトダイオードと読み出し回路の間にフォトチャージの円滑な移動通路を提供することで、暗電流ソースを最小化し、サチュレーション及び感度の低下を防止することができるイメージセンサー及びその製造方法を提供する。

【解決手段】読み出し回路120が形成されたピクセル部及び周辺回路が形成された周辺部を含む第1基板100と、前記読み出し回路120及び周辺回路と繋がるように前記第1基板100上に形成された配線150及び層間絶縁層160と、前記ピクセル部に対応する前記層間絶縁層160上に形成された結晶型半導体層200と、前記結晶型半導体層200に形成されて素子分離トレンチによって配線とそれぞれ繋がるフォトダイオード205と、第1基板100に形成された電気接合領域140を含む。

(もっと読む)

固体撮像素子、及び固体撮像装置

【課題】固体撮像素子においてあらゆる解像度で転送スピードを上げたりデータレート変えたりせずに信号を出力する。

【解決手段】固体撮像素子において2つの独立した電荷転送部を設ける。この2つの電荷転送部を電荷加算用電極を介して転送方向に沿って接続し、光電変換部から読み出された電荷を1つめの電荷転送部で受け、2つめの電荷転送部の転送スピードを解像度に応じて落として、1つめの電荷転送部で受けた電荷の加算を行う。電荷加算の終了後、2つの電荷転送部間に配置された読み出しゲートによって2つめの電荷転送部から1つめの電荷転送部へ戻し、電荷加算用電極に接続されたラストゲートを通って信号を出力する。信号出力前に電荷加算動作を行うので、データレートを変える必要も、転送スピードを上げる必要もない。

(もっと読む)

イメージセンサ及びその製造方法

【課題】イメージセンサ及びその製造方法を提供する。

【解決手段】実施の形態によるイメージセンサは、読み出し回路を含む第1基板と、前記第1基板上に形成され、内部に下部配線が形成された層間絶縁膜と、前記層間絶縁膜上に形成された結晶半導体層と、前記結晶半導体層内部に形成され、積層された第1不純物領域と第2不純物領域を含むフォトダイオードと、前記下部配線を露出させるように前記結晶半導体層及び層間絶縁膜を貫通する第1ビアホールと、前記下部配線及び第1不純物領域のみに連結されるように前記第1ビアホール内部に形成されたプラグと、前記フォトダイオードが単位ピクセルごとに分離されるように前記結晶半導体層内部に形成された素子分離領域と、を含む。

(もっと読む)

イメージセンサー

【課題】充てん比を高め、且つ電荷共有現象が発生しないイメージセンサーと、フォトダイオードとリードアウト回路の間にフォトチャージの円滑な移動通路を提供することで、暗電流ソースを最小化し、サチュレーション及び感度の低下を防止することができるイメージセンサーを提供する。

【解決手段】第1基板100に形成されたリードアウト回路120と、前記第1基板100に前記リードアウト回路120と電気的に接続して形成された電気接合領域140と、前記電気接合領域140上に形成された配線150と、前記配線150上に形成されたイメージ感知部210を含む。

(もっと読む)

固体撮像素子及び撮像装置

【課題】多画素化が進んだ場合でも電荷転送効率や感度を維持可能にすると共に、電荷の混合を行った場合でも高画質の画を作ることが可能な固体撮像素子を提供する。

【解決手段】互いに隣接する1対の光電変換素子1,2からなる光電変換素子組を複数有し、1対の光電変換素子1,2のうちの光電変換素子2に隣接して設けられた、光電変換素子2に蓄積された電荷を垂直方向Yに転送するための垂直電荷転送路3と、垂直電荷転送路3と光電変換素子2との間に設けられた、光電変換素子2に蓄積された電荷を垂直電荷転送路3に読み出すための素子−転送路間電荷読出し部10と、光電変換素子2とこれと対をなす光電変換素子1との間に設けられた、該光電変換素子1に蓄積された電荷を該光電変換素子2に読み出すための素子−素子間電荷読出し部11とを備える。

(もっと読む)

撮像方法および撮像装置並びに駆動装置

【課題】電荷転送方向における読出転送電極と電荷生成部の各中心位置が略一致した構造の撮像素子において、逆変調パルスを効果的に印加できるようにする。

【解決手段】読出転送電極12Bに読出パルスΦROGを供給してセンサ部から垂直転送レジスタへ信号電荷を読み出す際に(t11〜414)、読出転送電極12Bを挟む両側の専用転送電極12Aに、読出パルスΦROGとは逆極性の逆変調パルスを供給する(t12)。信号電荷を読み出す際に、読出転送電極12Bに読出パルスを印加した瞬間に両側の専用転送電極12Aに逆変調パルスを均等に印加することにより、読出しの間口に対して電荷転送方向の上流側と下流側の双方から対称に逆変調を加えることができ、センサ部から垂直転送レジスタへの信号電荷の均等かつ完全なる読出しを可能にし、さらに読出電圧を低減化することができる。

(もっと読む)

固体撮像素子

【課題】 異なる時刻に得られた複数の画像を高速に加算することができる固体撮像素子を提供する。

【解決手段】 マトリクス状に配置された複数のフォトダイオード32と、各フォトダイオード32の電荷を読み出して第1画像を構成する電荷として記憶する電極φH2と電荷を水平方向に転送する各電極φH0〜φH3とを有する水平転送レジスタ33と、第1画像とは異なる時刻に各フォトダイオード32の電荷を読み出して第2画像を構成する電荷として記憶する電極φV2と電荷を垂直方向に転送する各電極φV0〜φV3とを有する垂直転送レジスタ34と、を備え、電極φH0と電極φV0とは共通の電極であって、第1画像と第2画像とをこの共通の電極位置においてアナログ加算するようにした固体撮像素子。

(もっと読む)

固体撮像素子の製造方法及び固体撮像素子

【課題】感度を低下させずに小型化を実現することが可能な固体撮像素子の製造方法を提供する。

【解決手段】W又はAl等の光を透過しない遮光材料からなる遮光材料膜71を、電荷転送電極3の形状を反映した形状となるように、CVD又はスパッタによって堆積する(図3(a))。次に、フォトダイオード30の一部の上方に形成された遮光材料膜71をエッチング除去して、パターニングされた遮光膜71を形成する(図3(b))。次に、図3(b)に示す状態からスパッタエッチングを行う。ここでは例えばアルゴンガスを用いたスパッタエッチングを行う。スパッタエッチングを行うと、エッジ部分に電界が集中するため、遮光材料膜71のシリコン基板1に平行な面とシリコン基板1に垂直な面との境界部分が集中的に削られてなだらかになる(図3(c))。以上の工程により、固体撮像素子の遮光膜を形成する。

(もっと読む)

撮像素子およびそれを用いた撮像素子用装置

【課題】 蓄積部に蓄積する手順について汎用性が高い撮像素子およびそれを用いた撮像素子用装置を提供することを目的とする。

【解決手段】 フォトダイオード11に最も隣接する蓄積用CCDセル12について、その1つの蓄積用CCDセル12について3つのフォトダイオード11を並列的に接続するようにそれぞれを構成しているので、並列的に接続された各フォトダイオード11から蓄積用CCDセル12(蓄積部)に蓄積する手順について汎用性が高くなる。

(もっと読む)

固体撮像装置及びその製造方法

【課題】ジャンクションFETが形成されることを防止して黒スミアを抑制する。

【解決手段】 光電変換素子と該光電変換素子の隣に形成されたトランジスタとを含む固体撮像装置の製造方法において、前記光電変換素子及び前記トランジスタの形成領域の一導電型の基板に、逆導電型の第1拡散層を形成する工程と、前記光電変換素子の形成領域の前記第1拡散層上に一導電型の第2拡散層を形成する工程と、前記トランジスタの形成領域の前記第1の拡散層上に、前記第2拡散層と連続するように一導電型の第3拡散層を形成する工程と、前記第3拡散層上方の前記基板上方に開口部を有して形成されるゲート電極の前記開口部の位置において、前記基板を突出させて突部を形成する工程と、前記ゲート電極を形成する工程と、前記ゲート電極及び突部上に絶縁膜を形成する工程と、前記絶縁膜にコンタクトホールを形成する工程と、前記突部の基板表面近傍にソース領域を形成する工程とを具備したことを特徴とする。

(もっと読む)

CCD固体撮像素子

【課題】 本発明は、電荷転送効率を低下させることなく転送レジスタにおける消費電力を低減するCCD固体撮像素子を提供するものである。

【解決手段】 本発明のCCD固体撮像素子は、転送電極が単層で形成され相互にギャップを置いて配列された単層電極構造の転送レジスタを有し、前記転送電極の両端のギャップ幅が中央部よりも広く形成されていることを特徴とする。

(もっと読む)

1 - 20 / 22

[ Back to top ]