Fターム[4M119BB01]の内容

MRAM・スピンメモリ技術 (17,699) | 記憶素子の種類 (1,713) | TMR素子 (1,199)

Fターム[4M119BB01]に分類される特許

1 - 20 / 1,199

磁気抵抗効果素子、および磁気ランダムアクセスメモリ

磁気抵抗素子の製造方法

半導体装置の製造方法

記憶素子、記憶装置

【課題】熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。

そして、上記記憶層は非磁性体と酸化物が積層された積層構造層を含み、上記層構造の積層方向に電流を流すことにより、上記記憶層の磁化の向きが変化して、上記記憶層に対して情報の記録が行われる。

(もっと読む)

記憶素子、記憶装置

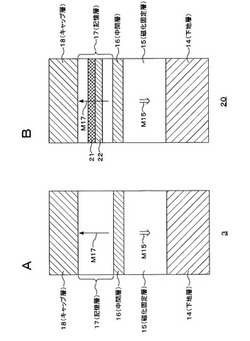

【課題】少ない電流で高速に動作させることが可能な記憶素子・記憶装置を提供する。

【解決手段】記憶層14と磁化固定層12とこれらの間に配された非磁性体による中間層13とキャップ層15とを少なくとも含み、上記記憶層として、第1の強磁性層14iと第2の強磁性層14pとが結合層14cを介して磁気的に結合され、上記第1の強磁性層が上記中間層に接し、上記第2の強磁性層が上記キャップ層に接しており、上記第1の強磁性層と上記第2の強磁性層のうち一方が膜面内磁化が優位な面内磁化層とされ、他方が垂直磁化が優位な垂直磁化層とされ、上記第1の強磁性層及び上記第2の強磁性層の磁化の向きが膜面に垂直な方向から傾斜しているものを用いる。記憶層の磁化の向きが傾斜しているので、記憶素子に対し膜面に垂直な方向の電流を流すと速やかに強磁性層の磁化の歳差運動の振幅増加が始り、短い時間の反転動作が可能になる。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性の情報書き込み方向に対する非対称性をすくなくし特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、磁化固定層を少なくとも2層の強磁性層とCrを含む非磁性層とを有する積層フェリピン構造とする。

(もっと読む)

記憶素子、記憶装置

【課題】書き込みエラーを生じることなく、短い時間で書き込み動作を行うことができる記憶素子及び記憶装置を提供する。

【解決手段】情報に対応して磁化の向きが変化される記憶層と、磁化の向きが固定された磁化固定層と、上記記憶層と上記磁化固定層との間に配された非磁性体による中間層とを含む層構造を有する記憶素子を構成する。そして上記磁化固定層が、少なくとも2つの強磁性層が結合層を介して積層され、上記2つの強磁性層が上記結合層を介して磁気的に結合し、上記2つの強磁性層の磁化の向きが膜面に垂直な方向から傾斜している。このような構成により、上記記憶層及び上記磁化固定層のそれぞれの磁化の向きがほぼ平行又は反平行とされてしまうことによる磁化反転時間の発散を効果的に抑えることができ、書き込みエラーを低減し、より短い時間で書き込みができる。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。その上で、上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。記憶層は、少なくともCo−Fe−B磁性層を有する。また記憶層に接する中間層と、該中間層とは反対側で記憶層が接する他方の層は、少なくとも記憶層と接する界面が酸化物層とされており、さらに上記他方の層は、酸化物層が、Liを含むLi系酸化物層とされている。

(もっと読む)

記憶素子、記憶装置

【課題】短パルス幅領域での反転電流の増加を防ぎ、熱安定性を確保して高速動作が可能な記憶素子を提供する。

【解決手段】記憶素子は、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。

そして、上記記憶層は、グラニュラー構造の酸化物の領域を含み、上記層構造の積層方向に電流を流すことにより、上記記憶層の磁化の向きが変化して、上記記憶層に対して情報の記録が行われる。

(もっと読む)

記憶素子、記憶装置

【課題】書き込みエラーを生じることなく、短い時間で書き込み動作を行うことができる記憶素子を提供することを目的とする。

【解決手段】記憶素子は、情報に対応して磁化の向きが変化される記憶層と、非磁性体による中間層と、上記記憶層に対して、上記中間層を介して設けられ、磁化の向きが固定された磁化固定層とを有する層構造を備える。

そして、上記記憶層は、少なくとも2つの強磁性層が結合層を介して積層され、上記2つの強磁性層が上記結合層を介して磁気的に結合し、上記2つの強磁性層の磁化の向きが膜面に垂直な方向から傾斜しており、上記層構造の積層方向に電流を流すことにより、上記記憶層の磁化状態が変化して、上記記憶層に対して情報の記録が行われる。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性の情報書き込み方向に対する非対称性をすくなくし特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、磁化固定層を少なくとも2層の強磁性層と非磁性層とを有する積層フェリピン構造とし、かつ、いずれかの上記強磁性層に接して反強磁性酸化物層が形成されているようにする。

(もっと読む)

記憶素子、記憶装置

【課題】書き込みエラーを生じることなく、短い時間で書き込み動作を行うことができる記憶素子及び記憶装置を提供する。

【解決手段】情報に対応して磁化の向きが変化される記憶層14と、磁化の向きが固定された磁化固定層12と、上記記憶層14と上記磁化固定層12との間に配された非磁性体による中間層13と、垂直磁気異方性誘起層15とを含む層構造を有する記憶素子3を構成する。そして、上記記憶層14が、第1の強磁性層14aと第1の結合層14bと第2の強磁性層14cと第2の結合層14dと第3の強磁性層14eとが同順に積層されて、上記第1の強磁性層14aが上記中間層13に接し、上記第3の強磁性層14eが上記垂直磁気異方性誘起層15に接し、上記結合層14b,14dを介して隣接する上記強磁性層14a,14c,14eの磁化の向きが膜面に垂直な方向から傾斜している。

(もっと読む)

記憶素子、記憶装置

【課題】環境温度によらず、熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。そして上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。この場合に、記憶層は正の磁歪定数を持つ磁性層を有するようにし、上記層構造に加えてさらに、負熱膨張材料層が設けられるようにする。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

記憶素子、記憶装置

【課題】熱安定性を確保して特性バランスに優れた記憶素子を実現する。

【解決手段】記憶素子は、膜面に垂直な磁化を有し、情報に対応して磁化の向きが変化される記憶層と、上記記憶層に記憶された情報の基準となる膜面に垂直な磁化を有する磁化固定層と、上記記憶層と上記磁化固定層の間に設けられる非磁性体による中間層とを有する層構造を備える。その上で、上記層構造の積層方向に電流を流すことで記憶層の磁化の向きが変化して、記憶層に対して情報の記録が行われる。そして記憶層は、Co−Fe−B磁性層と、少なくとも1つの非磁性層を有し、酸化物層、Co−Fe−B磁性層、非磁性層が順に積層された積層構造が形成されているようにする。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

最適化された信頼性を有する自己参照MRAMセル

【課題】MRAMセルに比べてより高い温度で確実に書き込まれ得る熱アシストされた書き込み操作と自己参照読み出し操作とに適した磁気ランダムアクセスメモリ(MRAM)セルを提供する。

【解決手段】メモリセルは、第1部分2’と第2部分2”とを有する磁気トンネル接合部分から構成され、各部分が、記憶層23,24とセンス層21,22とトンネル障壁層25,26とから構成され、この磁気トンネル接合が、当該2つの記憶層との間に反強磁性層20をさらに有し、これらの記憶層の各々の記憶磁化方向を臨界温度未満でピン止めし、これらの記憶磁化方向を臨界温度以上で自由にする。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、Fin型FETおよび従来型トランジスタを混載した半導体記憶装置を提供することである。

【解決手段】半導体記憶装置は第1の領域および第2の領域を備える。メモリ部のトランジスタは第1導電型のFin型半導体層を備える。第1導電型の第1のソース層および第1のドレイン層はFin型半導体層の両端に設けられる。第1のゲート電極はFin型半導体層の両側面に設けられる。第2導電型のパンチスルーストッパ層は第1のゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は第1のソース層および第1のドレイン層の下の不純物濃度よりも高い。周辺回路部のトランジスタは、第2のゲートトレンチを備える。第1導電型の第2のソース層および第1導電型の第2のドレイン層は、第2のゲートトレンチの両側に設けられる。第2のゲート電極は、第2のゲートトレンチ内に充填される。

(もっと読む)

磁気メモリの製造装置

【課題】より小さい磁場で磁性層の磁化方向を所定の方向に設定する。

【解決手段】磁気メモリ21の磁場印加装置30は、磁気メモリ21の磁性層に磁場を印加し、磁性層の磁化方向を初期化する磁石32A及び32Bと、磁性層に磁場が印加されている間に、磁気メモリ21の温度を上昇させる温度上昇機構33と、制御回路34とを含む。磁石32A及び32Bはそれぞれ、設定する磁化方向に応じて、磁場を発生し、磁気メモリ21の上から下へ向かう磁場、又は下から上へ向かう磁場が印加される。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

1 - 20 / 1,199

[ Back to top ]