Fターム[4M119DD02]の内容

MRAM・スピンメモリ技術 (17,699) | セル構成 (5,615) | 記憶素子 (3,263) | 記憶素子の層構造、接合 (2,545)

Fターム[4M119DD02]の下位に属するFターム

バリア層の構造 (128)

自由層の構造 (399)

固定層の構造 (555)

バッファ層又はシード層 (122)

キャップ層又は保護層 (155)

SyAF、積層フェリ磁性 (535)

2重トンネル接合 (184)

接合面が基板面と平行でないもの (18)

界面構造制御(ラフネス制御) (24)

垂直磁化膜を用いたもの (336)

Fターム[4M119DD02]に分類される特許

1 - 20 / 89

磁気記憶素子

【課題】書き込み電流を低減する。

【解決手段】磁気記憶素子10は、膜面に垂直方向の磁気異方性を有し、かつ磁化方向が可変である記憶層12と、記憶層12上に設けられた非磁性層13と、非磁性層13上に設けられ、かつ膜面に垂直方向の磁気異方性を有し、かつ磁化方向が不変である参照層14とを含む。記憶層12の面積は、参照層14の面積より大きく、記憶層12の端部の磁化は、記憶層12の中央部の磁化より小さい。

(もっと読む)

磁気記憶素子

【課題】記憶層に印加される漏れ磁界を低減する。

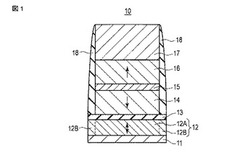

【解決手段】磁気記憶素子10は、膜面に垂直方向の磁気異方性を有し、かつ磁化方向が可変である記憶層11と、記憶層11上に設けられた非磁性層12と、非磁性層12上に設けられ、かつ膜面に垂直方向の磁気異方性を有し、かつ磁化方向が不変である参照層13と、参照層13上に設けられた非磁性層14と、非磁性層14上に設けられ、かつ参照層13からの漏れ磁界を低減する調整層15とを含む。調整層15は、界面層16と、膜面に垂直方向の磁気異方性を有する磁性層17とが積層されて構成され、界面層16の飽和磁化は、磁性層17の飽和磁化より大きい。

(もっと読む)

磁気メモリ素子及び磁気メモリ装置

【課題】電流で書き込み動作を行うことができる大容量の磁気メモリ及び磁気メモリ装置を提供する。

【解決手段】磁化が固定された第1の磁性層10と、磁化が可変の第2の磁性層30と、第1の磁性層10と第2の磁性層30との間に設けられた第1の中間層20と、第1の磁性層10と第2の磁性層30とを結ぶ第1の方向に直交する第2の方向に延在し、第2の磁性層30に隣接し、スピン波を伝搬する第1の磁性細線40と、第1の磁性細線40の一端に設けられた第1のスピン波入力部と、第1の磁性細線40の他端に設けられた第1のスピン波検出部と、を備える。

(もっと読む)

結晶性化合物及びこれを用いた可変抵抗素子並びに電子デバイス

【課題】磁気抵抗効果の大きい新たな可変抵抗素子を提供する。

【解決手段】本発明による可変抵抗素子は、次の3つの特徴を備えた結晶性化合物を含む。第1の特徴は、トポロジカル誘電体特性を示すことにより、伝導帯と価電子帯がディラックコーンを形成する点である。第2の特徴は、ディラックコーンを構成する伝導帯の谷と価電子帯の山との間に、バンドギャップが形成される点である。第3の特徴は、異なるスピンが入る二つのバンドがΓポイントを中心に時間反転対称を持つことである。これら3つの特徴を全て備えることにより、著しい磁気抵抗効果が発現する。

(もっと読む)

光不揮発性メモリ

【課題】光信号を直接不揮発的に記憶する光不揮発性メモリを提供すること。

【解決手段】第1導電型を有する第1半導体層12と、前記第1導電型とは異なる第2導電型を有する第2半導体層16と、前記第1半導体層と前記第2半導体層とに挟まれ、逆バイアスが印加されることにより受光し、順バイアスが印加されることにより発光する活性層14と、前記活性層の受光する光の強さによって磁化方向が変化する強磁性体層20と、を具備する光不揮発性メモリ。

(もっと読む)

磁気抵抗素子及び磁気メモリ

【課題】磁気抵抗素子の微細化に伴って増大する漏洩磁界をキャンセルする。

【解決手段】実施形態に係わる磁気抵抗素子は、垂直及び可変の磁化を持つ記憶層2と、垂直及び不変の磁化を持つ参照層4と、垂直、不変及び参照層3の磁化に対して逆向きの磁化を持つシフト調整層6と、記憶層2及び参照層4間の第1の非磁性層3と、参照層4及びシフト調整層6間の第2の非磁性層5とを備える。参照層4の反転磁界は、記憶層2の反転磁界と同じ又はそれよりも小さく、参照層4の磁気緩和定数は、記憶層2の磁気緩和定数よりも大きい。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】磁気抵抗効果素子のスピン注入磁化反転特性の劣化が抑制され、製造歩留まりが高い不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、複数のメモリセルを有する不揮発性記憶装置の製造方法であって、前記メモリセルのそれぞれは、第1電極を含む下地層と、前記下地層の上に設けられた磁気抵抗効果素子と、前記磁気抵抗効果素子の上に設けられた第2電極と、を有する。前記磁気抵抗効果素子は、記憶層である第1磁性層と、前記第1磁性層の上に設けられたトンネルバリア層と、前記トンネルバリア層の上に設けられ、参照層である第2磁性層と、を含む。前記第2磁性層の表面の一部もしくは前記第1磁性層の表面の一部にイオン化されたガスクラスタを照射して、前記第2磁性層の一部および前記第1磁性層の一部をエッチングする。

(もっと読む)

交換バイアスを有する磁気デバイス

【課題】所与の厚さの反強磁性層に対する交換バイアスが増加した磁気デバイスを提案することによって従来技術の欠点を克服すること。

【解決手段】本発明は、自由層として知られている、可変磁化方向を有する磁気層と、前記自由層と接触している、前記自由層の磁化方向をトラップすることができる第1の反強磁性層とを備えた磁気デバイスに関する。磁気デバイスは、さらに、安定化層として知られている、自由層とは反対側の面を介して第1の反強磁性層と接触している、強磁性体から作製される層を備えており、前記自由層および安定化層の磁化方向は実質的に垂直である。前記自由層および安定化層のうちの第1の層は磁化を有しており、その方向は、前記第1の層の平面内に配向されており、一方、前記自由層および安定化層のうちの2つの層の第2の層も磁化を有しており、その方向は、前記第2の層の平面外に配向されている。

(もっと読む)

垂直磁化磁気抵抗効果素子及び磁気メモリ

【課題】垂直磁気異方性を有する強磁性材料を用いて作製した磁気抵抗効果素子において、ビット情報に対応する磁化の平行状態及び反平行状態の熱安定性が不均衡になり、保存している情報により記録保持時間が異なる状態を改善する。

【解決手段】磁気抵抗効果素子を構成する参照層106と記録層107の面積を異ならせることにより、保存している情報に応じた記録保持時間の差を補正する。

(もっと読む)

磁気抵抗素子および磁気メモリ

【課題】書込み電流の範囲を広くすることができるとともに書込み電流を低減することができる磁気抵抗素子および磁気メモリを提供する。

【解決手段】本実施形態の磁気抵抗素子は、膜面に垂直方向に磁化容易軸を有し、磁化が可変の第1強磁性層と、膜面に垂直方向に磁化容易軸を有し、磁化が不変の第2強磁性層と、第1強磁性層と第2強磁性層との間に設けられた第1非磁性層と、第2強磁性層に対して第1非磁性層と反対側に設けられ、それぞれが異なる発振周波数の回転磁界を発振する強磁性体の複数の発振体を有し、各発振体が膜面に平行な磁化を有する、第3強磁性層と、を備え、第3強磁性層と、第1強磁性層との間に電流を流すことにより、スピン偏極した電子を第1強磁性層に作用させるとともに、第3強磁性層の複数の発振体に作用させて前記発振体の磁化に歳差運動を誘起し、歳差運動によって生じた複数の回転周波数を有し第1強磁性層の磁化反転をアシストする回転磁界が第1強磁性層に印加される。

(もっと読む)

磁気メモリ

【課題】データ記憶層が強い垂直磁気異方性を有し、かつ、データ記憶層とその下方に設けられた磁化固定層との間の磁気的結合が強い磁気メモリを提供する。

【解決手段】磁気メモリが、垂直磁気異方性を有し、磁化方向が固定された磁化固定層50a、50bと、層間絶縁層60と、磁化固定層50a、50bと層間絶縁層60の上面に形成された下地層40と、下地層40の上面に形成された、垂直磁気異方性を有するデータ記憶層10とを備えている。下地層40は、磁性材料で形成された第1磁性下地層41と、第1磁性下地層41の上に形成された非磁性下地層42とを備えている。第1磁性下地層41の膜厚は、層間絶縁層60の上において第1磁性下地層41が面内磁気異方性を発現しないように調節されている。

(もっと読む)

磁気トンネル接合素子及び磁気ランダムアクセスメモリ

【課題】 GMR素子では、十分大きなMR比を得ることが困難である。大きなMR比を実現することが可能なMTJ素子において、反転電流を低減させることが望まれている。

【解決手段】 下部電極の上に、磁化容易方向が厚さ方向を向く垂直磁気異方性膜が形成されている。垂直磁気異方性膜の上に、非磁性材料で形成されたスペーサ層が配置されている。スペーサ層の上に、アモルファスの導電材料からなる下地層が配置されている。下地層の上に、磁化容易方向が面内方向を向く磁化自由層が配置されている。磁化自由層の上にトンネルバリア層が配置されている。トンネルバリア層の上に、磁化方向が面内方向に固定された磁化固定層が配置されている。スペーサ層は、垂直磁気異方性膜と磁化自由層との間に交換相互作用が働かない厚さであり、かつスピン緩和長よりも薄い。

(もっと読む)

分極層を備える磁気トンネル接合

【課題】 分極層を備える磁気トンネル接合を提供する。

【解決手段】 本発明は、一定の向きの第1磁化を有する第1強磁性層と自由に偏向可能な第2磁化を有する第2強磁性層との間にあるトンネル障壁層と、第1磁化及び第2磁化にほぼ垂直な磁化極性を有する分極層とを備える磁気トンネル接合を備えるメモリ素子であって、第1及び第2強磁性層が、磁気トンネル接合のトンネル磁気抵抗が約150%以上になるようにアニールされるメモリ装置に関する。さらに、本発明は、当該MRAMセルを製造する方法に関する。

(もっと読む)

磁気スタックおよびメモリセル、ならびにセルを製造する方法

【課題】データ記憶装置における増加された記憶容量をもたらし得るより小さい全体セル厚さを提供する。

【解決手段】STRAMセルのような、不揮発性メモリセルについての装置および関連する方法が開示される。さまざまな実施形態に従えば、磁気自由層は、非磁気スペーサ層によって反強磁性層(AFM)から横方向に分離されるとともに、磁気トンネル接合によって合成反強磁性層(SAF)から内側に分離される。AFMは、磁気トンネル接合を超えて横方向に伸延するSAFのピニング領域との接触を通じて、SAFの磁化を固定する。

(もっと読む)

マルチレベルセル(MLC)磁気メモリセルを有する装置およびマルチレベルセル磁気メモリにデータを記憶させる方法

【課題】スピントルク注入ランダムアクセスメモリ(STRAM)メモリセルのような磁気メモリ素子にデータを書込むための方法および装置を提供する。

【解決手段】さまざまな実施の形態に従うと、マルチレベルセル(MLC)磁気メモリセルスタックは、第1の制御線に接続された第1および第2の磁気メモリ素子と、第2の制御線に接続されたスイッチング素子とを有する。第1のメモリ素子は並列に第2のメモリ素子と接続され、第1および第2のメモリ素子はスイッチング素子に直列に接続される。第1および第2のメモリ素子は、さらに、スタック内において、異なる、重ならない高さに配置される。プログラミング電流が第1および第2の制御線の間に流れて、第1および第2の磁気メモリ素子を、異なるプログラムされた抵抗に同時に設定する。

(もっと読む)

磁気トンネル接合構造体の製造方法及びこれを利用する磁気メモリ素子の製造方法

【課題】本発明は、磁気トンネル接合構造体の製造方法及びこれを利用する磁気メモリ素子の製造方法を提供する。

【解決手段】磁気トンネル接合構造体の製造方法は、基板上に第1磁性層、トンネル絶縁層、及び第2磁性層を順次に積層して磁気トンネル接合層を形成し、前記第2磁性層上にマスクパターンを形成し、少なくとも1回のエッチング工程と少なくとも1回の酸化工程を複数回行い、磁気トンネル接合層パターン及び前記磁気トンネル接合層パターンの少なくとも一つの側壁上に側壁絶縁層パターンを形成し、前記少なくとも一つのエッチング工程は、不活性ガスと前記マスクパターンを利用して前記磁気トンネル接合層の一部をエッチングする第1エッチング工程を含み、前記少なくとも一つの酸化工程は、前記磁気トンネル接合層のエッチング面に付着した第1エッチング生成物を酸化する第1酸化工程を含む。

(もっと読む)

メモリ装置およびそのプログラミング方法

【課題】磁気層を用いて選択することができるマルチビットメモリのための装置および関連する方法を提供する。

【解決手段】高保磁力を有する第1および第2の記憶層の間に配置される低保磁力を有する第1の選択層を配置し、第1の選択層の磁気飽和に応答して、第2の記憶層への論理状態のプログラミングが許可され、各ビットが選択的にプログラムされることにより、マルチビットメモリが達成され、データ記憶容量を増加することができる。

(もっと読む)

半導体装置

【課題】メモリ素子の信頼性と消費電流の抑制を両立させることができる半導体装置を提供する。

【解決手段】半導体装置は、複数の磁気メモリセルMCと、複数のディジット線DLと、ディジット線ドライブ回路28Bと、ビット線BL[0:95」とを備える。複数のビット線BL[0:95」は、たとえば12本ごとの複数の群に分割される。半導体装置は、複数のビット線の各々を少なくとも2段階の強度で駆動可能に構成されたビット線ドライブ回路22L,22Rとをさらに備える。ビット線ドライブ回路22L,22Rは、書込群に対しては、書込データに対応する極性の電流で2段階のうち強い強度でビット線を駆動し、非書込群に対しては、2段階のうち弱い強度で自分自身のデータに対応する極性のデータ保持電流を流す。

(もっと読む)

薄膜磁性体記憶装置

【課題】製造時ばらつきに対応して、データ読出時における高い信号マージンを確保可能な薄膜磁性体記憶装置を提供する。

【解決手段】ダミーメモリセルDCPは、2個のセルユニットCU0およびCU1を含む。各セルユニットCU0,CU1は、メモリセルと同様の構成を有し、ビット線BLと接地電圧Vssとの間に直列に結合された、トンネル磁気抵抗素子TMRおよびアクセストランジスタATRを有する。セルユニットCU0,CU1に対しては、異なる記憶データ“0”および“1”がそれぞれ書込まれる。データ読出時において、2個のセルユニットCU0,CU1が、読出参照電圧Vrefを伝達するためのビット線BLと接地電圧Vssとの間に並列に接続される。さらに、ダミーメモリセルDCPに対して、電流供給回路52からメモリセルに供給されるセンス電流Isの2倍、すなわち2・Isの一定電流が供給される。

(もっと読む)

1 - 20 / 89

[ Back to top ]