Fターム[4M119EE26]の内容

MRAM・スピンメモリ技術 (17,699) | 配線構成 (2,374) | ワード線(WL) (935)

Fターム[4M119EE26]の下位に属するFターム

WLが1セル、ユニットに1本だけ有するもの (617)

WLが1セル、ユニットに複数本有するもの (300)

Fターム[4M119EE26]に分類される特許

1 - 18 / 18

半導体記憶装置

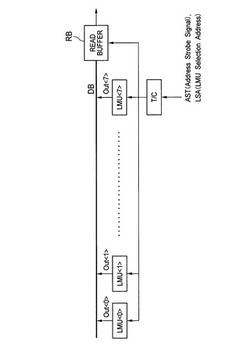

【課題】共通データバスを共有する複数のローカルメモリユニットが重複してデータを転送すること、あるいは、複数のローカルメモリユニットに対して重複してデータを転送することを抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルを含む複数のローカルメモリユニットLMU<0>〜LMU<7>を備える。共通データバスDBは、複数のローカルメモリユニットに共有され、複数のローカルメモリユニットからデータを転送し、あるいは、複数のローカルメモリユニットへデータを転送する。タイミングコントローラT/Cはローカルメモリユニットの単位で配置するのではなく、インターリーブ動作を行なう単位(ローカルメモリユニットLMU<0>〜LMU<7>のグループ)に対して1つ配置する。これにより読出しデータまたは書込みデータは、共通データバスDBにおいて衝突しない。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

合成記憶層を有するマルチビットセル

【課題】

2データビットより多いデータビットをMRAMセルに対して書き込み読み出すための方法であって、当該MRAMセルは、読み出し磁化方向を呈する読み出し層と、第1記憶磁化方向を呈する第1記憶強磁性層と第2記憶磁化方向を呈する第2記憶強磁性層と から成る記憶層とから形成された磁気トンネル接合から構成される。

【解決手段】

本発明の方法は、前記磁気トンネル接合を高温閾値より上で加熱するステップと前記第1記憶磁化方向を前記第2磁化方向に対して或る角度で指向させるステップとを有する。その結果、前記磁気トンネル接合が、読み出し磁化方向の方向に対する前記第1記憶磁化方向の方向によって決定される1つの抵抗状態レベルに到達する。書き込み領域を発生させるためのただ1つの電流線を使用することで、当該方法は、異なる少なくとも4つの状態レベルをMRAMセル内に記憶することを可能にする。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

磁気メモリセル及び磁気メモリ

【課題】電気的手段により磁気情報の書込みを行う磁気メモリセル及びそれを装備した大容量多値磁気メモリを提供する。

【解決手段】スピン蓄積層1上に配置した複数の磁気記録ビット31〜34と、1つの検出部によって磁気メモリセルを構成し、その磁気メモリセルを多数組み合わせて大容量磁気メモリを構成する。磁気記録ビットは、スピン蓄積層上に中間層、磁気記録層、障壁層、固定層、電極保護層を積層した構造を有し、検出部はスピン蓄積層上に中間層、固定層、電極保護層を積層した構造を有する。検出部は、各記録ビットを構成する磁気記録層の磁化方向の組合せを多値情報として電気的に検出する。

(もっと読む)

半導体装置

【課題】高速のデータ読出しが可能であるとともに、ワード線の活性化用のドライブ回路の面積を削減した半導体装置を提供する。

【解決手段】ワード線WLと複数箇所で接続される低抵抗の杭打ちワード線CWLを介した信号伝達によって、高速のデータ読出が可能となる。また、杭打ちワード線CWLは複数のメモリブロックBKで共通に設けられるので、ワード線ドライバ50Cを、複数のメモリブロックBKで共通化できる。さらに、サブディジット線SDLに対応して、杭打ちワード線CWLの活性状態を保持するラッチ回路92を設けることによって、杭打ちワード線CWLを介してデータ書込時の行選択信号を伝送することができ、金属配線層を削減できる。

(もっと読む)

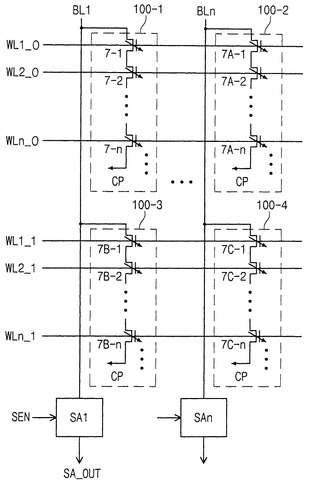

磁気抵抗ラム

【課題】セル構造が簡単かつセルサイズが小さく、従って製造工程が容易な磁気抵抗ラムを提供すること。

【解決手段】1つのビットラインとセルプレートとの間にNAND型に直列連結され、各々のゲートに複数のワードラインの信号が印加されるMRAMセルグループ、及び前記1つのビットラインに連結されセンスアンプイネーブル信号が印加されると、前記ビットラインに印加されたデータをセンシングするセンスアンプを備え、もしくは、

ビットラインとセルプレートとの間にNAND型に直列接続され、各々のゲート端子に複数のワードラインの信号が印加されるMRAMセルグループ、及び前記ビットラインに接続され前記MRAMセルグループに流れる電流を電圧に変換した後、前記MRAMセルグループ内のMTJの磁気分極方向の差による多重データを検出する多重データ検出回路を備える。

【選択図】図15  (もっと読む)

(もっと読む)

データ記録装置

【課題】小型化回路規模のオーバーライト回避機能を備えたデータ記録装置を提供する。

【解決手段】第1の閾値を超える第1の電気信号の供給によって第1の状態への書き込みが行われ、前記第1の電気信号とは逆極性であってかつ第2の閾値を超える第2の電気信号の供給によって第2の状態への書き込みが行われ、第1及び第2の端子を有する抵抗変化型メモリ素子と、第1及び第2の端子にそれぞれ第1及び第2の電気信号を供給する第1及び第2の電源回路と、第1の端子に接続され、第1の端子に供給される電気信号で前記メモリ素子の前記第1の状態を検出する第1の検出回路と、第2の端子に接続され、第2の端子に供給される電気信号でメモリ素子の第2の状態を検出する第2の検出回路と、抵抗変化型メモリ素子のオーバーライトを防止するため第1及び第2の検出回路の検出信号に従って第1及び第2の電源回路の出力を制御する制御回路とを具備する。

(もっと読む)

磁気記憶装置

【課題】メモリセルのサイズをより小さくして、小型化に寄与する磁気記憶装置を提供する。

【解決手段】1つのメモリセル1は、アクセストランジスタ2と磁気抵抗効果素子3とから構成される。一方向に沿って位置するメモリセル1では、各磁気抵抗効果素子3の一端側はビット線4aに接続され、他端側はアクセストランジスタ2のドレインに接続されている。そのアクセストランジスタ2のソース側はソース線5に接続されている。磁気抵抗効果素子3のフリー層のスピンの向きを磁場のアシストによって反転させるためのデータアシスト線7が形成されている。データアシスト線7は、2つの磁気抵抗効果素子3で一本のデータアシスト線を共有する態様で、一方向に互いに隣接する2つの磁気抵抗効果素子3,3a,3bの間に平面的に位置するように形成されている。

(もっと読む)

半導体装置

【課題】レイアウト面積のさらなる削減を図ることが可能な半導体装置を提供する。

【解決手段】半導体装置は、主表面S1を有する基板SUBと、基板SUBの主表面S1から離間して配置され、データを記憶する記憶素子M1と、書き込み電流線DL<0>と、記憶素子M1にデータを書き込むためのデータ書き込み電流を書き込み電流線DL<0>に流し、基板SUBの主表面S1において形成される導通電極を有し、かつ記憶素子M1の下方に配置されるドライブトランジスタDLDTR0とを備える。

(もっと読む)

スピン蓄積磁化反転型のメモリ素子及びスピンRAM

【課題】 耐久性に優れたスピンメモリの実現。

【解決手段】 強磁性ワード線と、強磁性ワード線と交差する非磁性ビット線と、強磁性ワード線と対向する配線と、強磁性ワード線及び非磁性ビット線の交差部分と配線との間に設けられた磁気抵抗効果素子201とを備える。書き込み動作時には、強磁性ワード線と前記非磁性ビット線との間に電流を流し、強磁性ワード線から非磁性ビット線にスピンを蓄積させることで磁気抵抗効果素子の自由層の磁化方向を反転させる。読み出し動作時には、非磁性ビット線と配線との間に電流を流し、磁気抵抗効果素子の膜厚方向に電流を流す。

(もっと読む)

微小角度トグル書き込み線を有する磁気抵抗ランダムアクセスメモリデバイス、そのアレイ及びそのスイッチング方法

【課題】本発明は、スイッチ磁界を低減し書き込み時の低エラー率を実現するトグルモードM-RAMデバイスを提供する。

【解決手段】本発明は、第1面上の第1方向に沿って延びる第1書き込み線と、第1面に平行な第2面上において第1方向と直交しない第2方向に沿って延びる第2書き込み線と、スイッチング可能な磁化状態を有し、それらの交差領域に配列される磁気抵抗メモリ素子とを備え、第1書き込み線は、第1書き込み電流が印加されると、第1磁界をメモリ素子に印加するように設けられ、第2書き込み線は、第2書き込み電流が印加されると、第2磁界をメモリ素子に印加するように設けられ、第1及び第2磁界はそれぞれ、メモリ素子における磁化容易軸に対して45度未満の方向を有し、所定の処理でメモリ素子に印加される場合に、第1及び第2磁界を合成した磁界が、メモリ素子の磁化状態をスイッチングするために十分な大きさであることを特徴とする。

(もっと読む)

半導体記憶装置

【課題】メモリセルの高密度化を図れるMRAMやPRAM等の半導体記憶装置を提供する。

【解決手段】間隔を有して順に配置され、膜面に対して垂直方向に電流を流すことで記録が行われる第1乃至第4の抵抗変化素子MTJ1〜MTJ4と、第1及び第2の抵抗変化素子を接続する第1の電極15と、第3及び第4の抵抗変化素子を接続する第2の電極15と、第2及び第3の抵抗変化素子を接続するビット線BL2と、抵抗変化素子と対をなし、第1及び第2の電極と離間して配置されたワード線WL1〜WL4と、第1乃至第4の抵抗変化素子の中の選択素子にデータを書き込む時、第1乃至第4の抵抗変化素子と第1及び第2の電極とビット線とを有するチェーン構造部に第1の電流Iw1を流す第1の電流源と、選択素子にデータを書き込む時、選択素子に対応する第1乃至第4のワード線の中の選択ワード線に第2の電流Iw2を流す第2の電流源とを具備する。

(もっと読む)

半導体記憶装置

【課題】センスアンプ回路の特性を劣化させることがなく、かつ、出力電圧レンジを大きく取ることができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、それぞれビット線BLx0,BLx1に接続された複数の磁気抵抗素子Rx0,Rx1と、それぞれビット線BL_Bx0,BL_Bx1に接続された複数のリファレンス抵抗Rmin,Rmaxと、センスアンプ回路10とを備える。磁気抵抗素子Rx0,Rx1は、2値のデータを蓄積する。リファレンス抵抗Rmin,Rmaxは、基準抵抗値Rrefを発生するために用いられる。センスアンプ回路10は、磁気抵抗素子Rx0,Rx1からデータを読み出すときに、上記各ビット線上を流れる電流IA〜IDをそれぞれ分流させ、各分流された電流を、各分流された電流が流れるビット線とは異なる対応するビット線を流れる電流と合流させるN型トランジスタ28a〜31a,28b〜31bを備える。

(もっと読む)

磁気記憶装置及びその書き込み/読み出し方法

【課題】大容量メモリを実現する。

【解決手段】磁気記憶装置は、磁壁12で区切られた磁区11からなる複数のセルで構成され、このセル毎に情報が記録された磁性配線10と、この磁性配線の一端部に配置された書き込み用素子20と、磁性配線の他端部に配置された読み出し用素子30とを具備する。書き込み動作時には、金属配線からなる書き込み用素子に書き込み電流Iwを流し、この書き込み電流Iwにより発生する磁場を磁性配線10の一端部に位置するターゲットセル(書き込みたいアドレスのセル)TC−wに印加する。読み出し用素子30はMTJ素子(磁気抵抗効果素子)からなる。

(もっと読む)

交換結合膜及び磁気デバイス

【課題】従来に比べて交換結合力が高く、かつ製造が容易な交換結合膜及びその交換結合膜を備えた磁気デバイスを提供する。

【解決手段】本発明に係る交換結合膜30は、Ru−Rh合金からなる非磁性層31を2つの強磁性層32a,32bで挟んだ構造を有している。本発明の交換結合膜を磁気ヘッド(読み取り素子)に適用する場合、例えば非磁性層31の厚さを0.4〜0.5nmとし、Rh含有量を5〜40at%とする。また、本発明の交換結合膜を磁気記録媒体に適用する場合、例えば非磁性層31の厚さを0.4〜0.6nmとし、Rh含有量を5〜70at%とする。更に、本発明の交換結合膜をMRAMに適用する場合、非磁性層31の厚さを例えば0.3〜0.7nmとし、Rh含有量を5〜40at%とする。

(もっと読む)

トンネル電界効果トランジスタを用いたメモリ

【課題】抵抗メモリの一種として挙げられ、抵抗記憶素子に相変化材料を用いた相変化メモリを提供する。

【解決手段】メモリは、第1ドレイン124と第1ソース122aとを含む第1トンネル電界効果トランジスタ108aを含んでいる。上記第1ドレインは、第1抵抗記憶素子106aに結合されている。上記メモリは、第2トンネル電界効果トランジスタ108bを含んでいる。上記第2トンネル電界効果トランジスタは、第2ドレインを含み、上記第1ソース122aを共有している。上記第2ドレインは、第2抵抗記憶素子に結合されている。上記メモリは、ソースノードを設けるために、上記第1ソースに結合されている第1領域114を含む。

(もっと読む)

導電制御デバイス

【課題】種々の用途に使用できる導電制御デバイスを提供すること。

【解決手段】導電制御デバイスは、比較的大きい飽和保磁力を有する第1強磁性領域(6)と、比較的小さい飽和保磁力を有する第2強磁性領域(8)と、第1強磁性領域と第2強磁性領域との間に配置された接合領域(11)とを備え、このデバイスは、更に接合領域内の電荷キャリア密度を制御するよう接合領域に電界を加えるためのゲート(3)も備える。

(もっと読む)

1 - 18 / 18

[ Back to top ]