Fターム[5B001AB01]の内容

Fターム[5B001AB01]に分類される特許

1 - 20 / 106

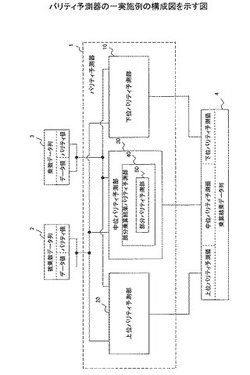

パリティ予測器、キャリーレス乗算器、及び演算処理装置

【課題】キャリーレス乗算器の誤動作の検出を可能にする。

【解決手段】pビット(pは2以上の自然数)のデータユニットがそれぞれq個(qは自然数)並べられたデータ列である被乗数データ列2と乗数データ列3とのキャリーレス乗算を行う乗算回路が出力する乗算結果データ列4のパリティ値をパリティ予測器1が予測する。下位パリティ予測部10は、乗算結果データ列4における下位より1番目のデータユニットのパリティ値を、被乗数データ列2と乗数データ列3とにおける、下位より1番目のデータユニットの値及びパリティ値に基づき予測する。上位パリティ予測部20は、乗算結果データ列4における下位より2q−1番目のデータユニットに続く上位p−1ビットのデータのパリティ値を、被乗数データ列2と乗数データ列3とにおける、下位よりq番目のデータユニットの値及びパリティ値に基づき予測する。

(もっと読む)

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置を提供する。

【解決手段】メモリ・システム100は、ホスト110とメモリ・デバイス120との間でデータを転送するためにデータ・フレームを使用する。いくつかの場合には、システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。いくつかの実施形態では、データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

情報処理システム、データエラー検出方法、プログラム及び記憶媒体

【課題】データの冗長化を行わずにデータを書き換えながらデータエラーの検出を行うことである。

【解決手段】情報記憶装置の中の監視対象領域にあるデータの整合性を確認するための第一チェック値を算出する第一チェック値算出手段と、第一チェック値を算出している途中で監視対象領域にあるデータを書き換える場合にその書き換えによる第一チェック値の変化を表す情報を作成する変化情報作成手段と、第一チェック値の算出が完了したときに第一チェック値及び変化情報作成手段により得られる第一チェック値の変化を表す情報から第二チェック値を繰り返し算出する第二チェック値算出手段と、第二チェック値算出手段で得られた第二チェック値とそれ以前に得られた第二チェック値とを比較することによりデータエラーを判定するデータエラー判定手段とを備える。

(もっと読む)

ICカード及びプログラムコードの診断方法

【課題】 プログラムコードの自己診断によって特定のコマンド処理に不具合が発生すること、あるいはプログラムコード自己診断の実行が不十分となることを回避することのできるICカード及びプログラムコードの診断方法を提供する。

【解決手段】 外部からのコマンドを解釈実行し、その結果を応答するICカード(1)において、ICカードで実行されるプログラムを格納するプログラム領域(104)と、外部からコマンドを受信する受信部(13)と、コマンドに対応した処理、及びプログラム領域内のプログラムについてプログラムコードの良否診断処理を実行する制御部(101)とを有し、制御部は、プログラムコードの良否診断を、受信部が所定のコマンドを受信する毎の複数回に分割して実行し、分割された良否診断を実行した後で当該所定のコマンドの処理を実行するICカードである。

(もっと読む)

CRC演算回路及びプロセッサ

【課題】少ない処理段数でCRC演算を行うことができるCRC演算回路を提供することを課題とする。

【解決手段】CRC演算回路は、第3のデータのうちの最上位ビットのデータと、第4のデータとの排他的論理和を演算する第1の排他的論理和回路(1403)と、第3のデータのうちの最上位ビットのデータと、第1のデータとの論理積を演算する複数の第1の論理積回路(1401)と、複数の第1の論理積回路の出力データと、第3のデータのうちの最上位ビット以外のデータとの排他的論理和を演算する複数の第2の排他的論理和回路(1402)と、第1の排他的論理和回路の出力データと、第2のデータとの論理積を演算する複数の第2の論理積回路(1404)と、複数の第2の排他的論理和回路のうちの一部の出力データと、複数の第2の論理積回路のうちの一部の出力データとの論理和を演算する複数の論理和回路(1405)とを有する。

(もっと読む)

情報処理装置、情報処理システム、情報処理装置の制御方法、および、プログラム

【課題】誤動作が生じない電源電圧または周波数の正確な値を情報処理装置に設定することを容易にする。

【解決手段】第1パリティ生成部420は、演算器310により処理された処理データのエラーを検出するための第1のエラー検出符号を生成する。第2パリティ生成部は、第1のエラー検出符号から処理データのエラーを検出するための第2のエラー検出符号を生成する。第1パリティ検査部460は、保持された第1のエラー検出符号を使用して保持された処理データのエラーを第1のエラーとして検出する。第2パリティ検査部470は、保持された第2のエラー検出符号を使用して保持された処理データのエラーを第2のエラーとして検出する。制御量出力部500は、第1のエラーの発生率が第1の閾値以下であるときに、第2の閾値を第2のエラーの発生率の目標値として電源電圧または周波数を制御する制御量を出力する。

(もっと読む)

PCIバス制御システム

【課題】イニシエーターとターゲットとをPCIバスにより接続したPCIバス制御システムに関し、コマンドエラーを回避する。

【解決手段】

イニシエーター1とターゲット2−1,2−2との間をPCIバスにより接続したPCIバス制御システムであって、監視回路3と救済回路4とを設け、PCIバスによりイニシエーター1とターゲット2−1,2−2間を監視回路3と救済回路4とを介して接続すると共に、イニシエーター1と監視回路3と救済回路4との間を、コマンドCOMMとパリティPARとパリティエラーPERRとを転送するローカルバスにより接続し、監視回路3によりコマンドのパリティチェックを行って送出し、救済回路4は、PCIバスとローカルバスとを介してそれぞれ転送されたコマンドについて、正常な側を選択して、ターゲット2−1,2−2にコマンドを転送する構成を備えている。

(もっと読む)

データ障害処理装置、及びデータ障害処理方法

【課題】繰り返しの障害発生を回避してプロセッサリリーフを実現するデータ障害処理装置、及びデータ障害処理方法を提供すること

【解決手段】データ障害処理装置は、誤り訂正機能を持つ記憶装置に格納されたデータにアクセスするプロセッサ3を備える。記憶装置は、データ供給時にデータに対して誤り訂正符号を付与する。障害識別部302は、誤り訂正符号に基づいて、前記記憶装置から供給されたデータに障害が発生しているか否かを識別する。事前評価部305は、訂正不可能障害が生じたデータが格納されたアドレスに再度アクセスする事前評価リクエストを発行する。救済可否判定部306は、前記事前評価リクエストの発行結果に応じてプロセッサリリーフが実行可能かを判定する。障害処理部307は、救済可否判定部の判定に応じて障害対応処理を行う。

(もっと読む)

車両用電装部品の制御装置およびその制御方法

【課題】内容の異なる第1のプログラムがインストールされたマイクロコンピュータに対して記憶部全体の検査を容易に行え、マイクロコンピュータの動作の信頼性を確保することができる車両用電装部品の制御装置およびその制御方法を提供する。

【解決手段】第1記憶部31には調整データ記憶領域33が設けられ、基本プログラム記憶領域32に記憶される基本プログラムのバージョンに応じた調整データが記憶される。調整データは、第1記憶部31に対する検査プログラムによる検査結果(検査値)が、基本プログラムのバージョンによらず、同値となるように調整される。よって、検査プログラムによるフラッシュメモリ30のすべての記憶領域の検査のため、基本プログラムのバージョンに応じた検査プログラムを用意する必要がない。

(もっと読む)

アドレス変換検査装置、中央処理演算装置、及びアドレス変換検査方法

【課題】メモリ管理装置に設けられたバッファに読み込まれた変換テーブルを用いて、中央処理演算装置が物理メモリへ正常にアクセスできるか否かを他のプログラムを実行したままで検査する。

【解決手段】情報処理装置10は、物理メモリのアドレスである物理アドレスと仮想メモリのアドレスである仮想アドレスとを変換するための変換テーブルに基づいて、前記仮想アドレスと前記物理アドレスとを変換するMMU20を備えている。そして、RAM14には、ページテーブルを示すページテーブル情報、及びページテーブル情報に付加され、MMU20による仮想アドレスと物理アドレスとの変換の異常の有無を検出するための異常検出情報が記憶されている。そして、CPU12は、異常検出情報に基づいて、MMU20による仮想アドレスと物理アドレスとの変換の異常の有無を検出する。

(もっと読む)

プログラム実行装置、プログラム生成装置、プログラム正否判定方法、および、プログラム加工方法

【課題】製造コストの削減や小型軽量化を図ると共に、スループットの低下を回避しつつ、オブジェクトプログラムを実行するタイミングでの誤り検出が可能となる。

【解決手段】プログラム実行装置120は、オブジェクトプログラムを実行する命令実行部220と、オブジェクトプログラムを一時的に保持するキャッシュメモリ222と、命令実行部によるオブジェクトプログラムのフェッチ要求を契機に、オブジェクトプログラムを読み込み、キャッシュメモリに保持させるプログラム読込部224と、読み込まれたオブジェクトプログラムに対し、順次、チェックコード導出式を計算し、ブロック単位でチェックコードを生成し、オブジェクトプログラムに予め挿入されているチェックコードと比較してオブジェクトプログラムの正否をブロック単位で判定するチェックコード判定部226とを備える。

(もっと読む)

冗長化制御システム、及びその演算データの伝送方法

【課題】受信側で伝送誤り検出と、冗長系毎の演算データの誤りと故障診断とを可能とした冗長化制御システムの演算データの伝送方法を提供することを目的とする。

【解決手段】第1の演算データを生成し、返信時の誤り検出用の第1の生成アルゴリズムを使用して第1の生成データを生成するステップと、第2の演算データを生成し、誤り検出用の第2の生成アルゴリズムを使用して第2の生成データを生成するステップと、相互に第1/第2の演算データとを比較照合するステップと、一致した演算データと、第1/第2の生成データとを含む伝送データを送信するステップと、受信装置では、演算データと予め設定された第1/第2の生成アルゴリズムとから第3/第4の生成データとを生成するステップと、第1/第3の生成データとを、また、第1/第3の生成データとを比較照合して、受信した演算データの誤りを検出するステップとを備えた演算データの伝送方法。

(もっと読む)

車両制御システム

【課題】多数のECUがネットワークを介して協調動作を行う車両制御システムにおいて

、低コストでネットワーク内の障害ノードを正確に特定する。

【解決手段】各ノードは、ネットワーク内ノード状態判定手段,自ノードによるノード状

態判定結果送信手段および他ノードによるノード状態判定結果受信手段、および障害ノー

ド特定手段から構成され、前記ネットワーク内ノード状態判定手段による判定結果を他ノ

ードと相互に交換することにより、障害ノードを特定する。

(もっと読む)

演算処理装置、情報処理装置および演算処理装置の制御方法

【課題】演算処理装置において、読み出されたデータのエラーを検出してからエラーを訂正して通常の動作状態に復帰するまでの時間を短縮すること。ハードウェアの量を減らすこと。

【解決手段】チェック部43が記憶部33の出力データのエラーを検出すると、演算制御部31はエラー検出信号EU_PDを出力する。演算制御部31は、記憶部33にエラーが発生したことを示すエラー識別信号GPR_DATA_ERRORを出力する。命令制御部36は、エラー検出信号およびエラー識別信号に基づいてキャンセル信号CANCELおよび訂正開始信号CORRECT_STARTを出力する。演算処理装置12は、キャンセル信号によって演算部32の動作を停止し、エラーの報告処理を開始する。演算処理装置12は、訂正開始信号によってエラー訂正部34でのエラーの訂正処理を開始する。エラーの訂正処理はエラーの報告処理と並行して行われる。

(もっと読む)

判定装置及び判定方法

【課題】複数のデータ処理回路を備える半導体集積回路の不具合箇所を特定することができる判定装置を提供すること。

【解決手段】本発明の一態様に係る判定装置は、第1OSDプレーン23A及び第2OSDプレーン23B、ビデオプレーン23Cを備えるLSI20Aの良否判定を行うものである。入力されるテストパターンに応じて複数の画像処理回路が形成する1フレームの画像において、第1OSDプレーン23Aからの出力に対応する領域Aと、第2OSDプレーン23Bからの出力に対応する領域BとをCRC演算する領域として設定する。CRC演算回路15は、領域A、領域BのCRC演算を行ってそれぞれの演算結果を算出し、それぞれの領域に対応する期待値と演算結果とをそれぞれ比較して、複数のデータ処理回路の良否判定を行うCPU22に出力する。

(もっと読む)

パリティチェック回路およびコンピュータシステム

【課題】パリティエラー信号を強制的に発生させることができるパリティチェック回路を提供する。

【解決手段】レジスタ131aに入力されるデータのパリティビットを算出する第1パリティ算出回路133aと、レジスタ131aから出力されるデータのパリティビットを算出する第2パリティ算出回路136aと、第1パリティ算出回路133aが算出したパリティビットと第2パリティ算出回路136aが算出したパリティビットとを比較し、双方のパリティビットが互いに異なる場合、パリティエラー信号を出力するEXOR回路137aと、を備えるパリティチェック回路132aにおいて、自パリティチェック回路外部から入力されるパリティエラー信号発生指令に基づいて第1パリティ算出回路133aが算出したパリティビットを反転するEXOR回路134aをさらに備える。

(もっと読む)

ストレージデバイス内のエラーデータを追跡するシステムおよび方法

エラーデータを追跡するシステムおよび方法を開示する。この方法が、第1のエラー訂正コード演算のエラー場所に関連づけられた第1のチェックサムを受信するステップと、第2のエラー訂正コード演算のエラー場所に関連づけられた第2のチェックサムを受信するステップとを含む。第1のチェックサムは、第2のチェックサムと比較され、その比較結果に基づいてメモリアレイの領域に動作が開始される。  (もっと読む)

(もっと読む)

半導体集積回路及び半導体集積回路の故障診断方法

【課題】CPUのパフォーマンスに影響を及ぼすことなく、故障診断を行うことを可能にする半導体集積回路を提供する。

【解決手段】通常動作において利用される第1のバスBUSA、及びそれとは異なる第2のバスBUSAに接続されたCPU1から第2のバスを介して出力される診断情報に基づいて、診断マクロ6が誤り検出情報を求め、プログラムの実行に応じて求められた最終の誤り検出情報と保持している1つの期待値との比較によりCPUが故障しているか否かを判定するようにして、通常動作に利用される第1のバスの負荷を増加させずに、故障診断を行えるようにする。

(もっと読む)

データ保護回路及び方法、並びにデータ処理装置

【課題】誤り検出符号の変換過程において十分なデータ保護を行う。

【解決手段】データ保護回路4内の生成部100_1は、入力データD1inを、これを出力データD1outとして出力するための経路(P2→P4→P10→P13)上の一の箇所(例えば、P2とP4の接続ノード)から取得し、第2の誤り検出符号(例えば、ECC C1)を生成する。検査部200_1は、入力データD1inを、前記経路上の生成部100_1の取得箇所よりも出力側に近い他の箇所(例えば、P10とP13の接続ノード)から取得し、第1の誤り検出符号(例えば、パリティC2)を用いて入力データD1inの検査を行う。また、接続部300_1は、入力データD1inが生成部100_1に次いで検査部200_1により取得されるよう、生成部100_1の取得箇所(P2とP4の接続ノード)と検査部200_1の取得箇所(P10とP13の接続ノード)とを接続する。

(もっと読む)

エラー検出機能付き演算回路、および演算回路のエラー検出方法

【課題】ソフトエラーに基づく演算結果の誤りを確実に検出する。

【解決手段】エラー検出機能付き演算回路は、グレイコード形式の第1の数値を保持するレジスタと、前記レジスタに保持された前記第1の数値から、該第1の数値に対する所定の数値演算の結果である第2の数値をグレイコード形式で求めて出力する数値演算手段と、前記レジスタに保持された前記第1の数値に対するパリティ値である第1のパリティ値を使用して、前記数値演算に対応する所定の論理演算を行うことにより、前記第2の値に対するパリティ値である第2のパリティ値を生成するパリティ演算手段と、前記パリティ演算手段により生成された前記第2のパリティ値を使用して、前記数値演算手段により出力された前記第2の数値に対するパリティチェックを行うパリティチェック手段と、を有する。

(もっと読む)

1 - 20 / 106

[ Back to top ]