Fターム[5B001AD08]の内容

Fターム[5B001AD08]に分類される特許

1 - 5 / 5

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置を提供する。

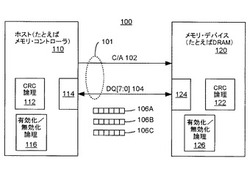

【解決手段】メモリ・システム100は、ホスト110とメモリ・デバイス120との間でデータを転送するためにデータ・フレームを使用する。いくつかの場合には、システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。いくつかの実施形態では、データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

仮想計算機システム

【課題】

PCI-Expressバスに代表される汎用のIOバスを有するサーバにおいて、32bitアドレッシングモードのI/Oアクセスを可能とするLPAR環境を提供する。

【解決手段】

(1) LPAR上のOSで発行されたIOトランザクションが32bitフォーマットであった場合で、かつ変換後の絶対アドレスが32bit空間を超えている場合に、IOトランザクションのパケットフォーマットを変換する。

(2) LPAR上のOSで発行されたIOトランザクションにECRCが付与されていた場合に、ECRCを再計算して最終受領先で正常に受信できるようにする。

(3) ECRCが既にエラーになっていた場合には、同じエラーを再現するようなECRCパターンを生成してパケットに付与する。

(4) 前記のECRC生成について、32bitと64bitのCRC演算器を搭載して同時に計算し、パケット生成時にバス上のデータ長を元に正しいCRC演算結果を選択する。

(もっと読む)

エラー処理方法及び情報処理装置

【課題】本発明は、エラー処理方法及び情報処理装置に関し、ハーバードアーキテキチャを有するCPUの命令バス又はデータバスで発生したバスエラーを適切に処理可能とすることを目的とする。

【解決手段】CPUのバスで発生したエラーを処理するエラー処理方法において、CPUの命令バス及びデータバスのうち少なくとも一方のバスで発生したバスエラーをバスエラー入力手段によりCPUに入力し、バスエラーをCPU内のバスエラーカウンタでカウントし、バスエラーカウンタの値に基づいてCPUに接続されたメモリ部の領域を指定するように構成する。

(もっと読む)

二重化制御システム

【課題】バックボードバスの片側に異常が発生した場合でも、無駄なアクセスよるプロセッサ装置のパフォーマンス低下を防止した二重化制御システムを実現する。

【解決手段】二重化されたプロセッサ装置間の通信の異常検出を向上させた二重化制御システムに関するものである。2つのプロセッサ装置は、二重化されたシリアルバスにより接続され、制御演算及び相手側のプロセッサ装置とのアクセスを実行する上位コントローラと、シリアルデータの送信を制御する二重化された送信コントローラと、シリアルデータの受信を制御する二重化された受信コントローラと、受信データの正当性を診断する二重化された診断手段とを設けた。

(もっと読む)

送信モジュール、受信モジュール、及びシステム

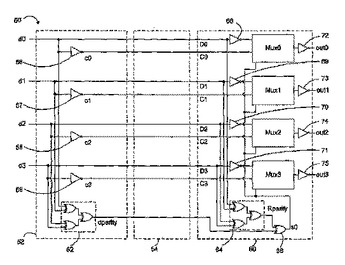

データビットのセットを別のモジュールへ通信バスを介してデュアルエンコーディングを用い送信する、切り替え動作の少ないモジュールが提供される。前記モジュールは、データビットのセットを前のデータビットのセットと比較し、データビットの送信に必要な遷移の数の表示を決定し、データビットの送信に必要な遷移の数がデータビットのセットの全ビット数の半数より大きいと決定された場合、データビットを送信前に反転し、及びデータビットのセットが反転されているか否かの表示を提供するバス反転符号化手段;及び他のモジュールへ通信バスを介しデータビットのセット、それらの対応するコピー及びデータビットのセットが反転されているか否かの表示を送信する手段を有する。前記モジュールはまた、データビットのセットのデータビットの対応するコピーを生成する手段;及び他のモジュールへ通信バスを介しデータビットのセット、それらの対応するコピー及びデータビットのセットが反転されているか否かの表示を送信する手段を有する。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]