Fターム[5B005JJ00]の内容

階層構造のメモリシステム (9,317) | 目的、効果 (1,912)

Fターム[5B005JJ00]の下位に属するFターム

Fターム[5B005JJ00]に分類される特許

1 - 5 / 5

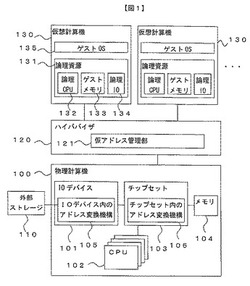

仮想計算機システムにおけるメモリ割り当て方法

【課題】 アドレス変換機構を持ったIOデバイスを含む仮想計算機システムにおいて、IOデバイスのハードウェア上の制限を回避し、柔軟なゲストメモリ割り当てを可能とする。

【解決手段】 IOデバイス内のアドレス変換機構とチップセット内のアドレス変換機構を併用し、ゲスト物理アドレスからホスト物理アドレスへの変換を行う際には、仮想的なアドレスである仮アドレスを経由する。仮アドレスでゲストメモリ領域の分散を抑え、IOデバイス内のアドレス変換テーブルエントリを節約することで、フラグメント化によるゲストメモリ割り当て失敗を抑える。また、仮アドレスからホスト物理アドレスへの変換にチップセット内のアドレス変換機構を用いることで、仮想計算機に割り当てるメモリサイズを細かく指定できるようになる。

(もっと読む)

計算機仮想化装置、そのプログラム、及びその方法

【課題】

計算機の仮想化において、性能低下の少ないTLB仮想化方式を実現しようとすると、メモリ空間識別子(以下、RID)の仮想化が必要となるが、RIDの一部をゲストIDを現す領域にするとLPARの数に制限があり、運用上問題となる。

【解決手段】

ハイパーバイザ13は、動的に項目を登録・管理するゲストRID-物理RIDマッピングテーブル137を用意し、このゲストRID-物理RIDマッピングテーブル137を用いてRID変換を行う。このマッピングテーブル137を用いることにより、変換されるRIDに各ゲストに対応するLPAR11をあらわす特定の情報領域を設ける必要がないため、LPAR11の数に関する制限がなくなり、運用上の問題を無くすことができる。

(もっと読む)

記憶装置、記憶方法、プログラムおよび記録媒体

【課題】 特定の条件のときに記憶装置が発生する音を軽減し、音の発生を軽減した状態でも情報を記憶することができる記憶装置を提供する。

【解決手段】 データ制御部13は、記録要求データ20を受信したとき、許可条件が成立しているか否かを判断部15に問い合わせる。判断部15が、許可条件が成立していると判断すると、記録要求データ20を第1の記憶部11に記憶し、判断部15が、許可条件が成立していないと判断すると、記録要求データ20を第2の記憶部12に記憶する。第2の記憶部12に記憶された記録要求データ20は、許可条件が成立すると、データ制御部13によって第2の記憶部12から読み出され、第1の記憶部11に記憶される。

(もっと読む)

低電力プログラマブルプロセッサ

本グラフィックスプロセッサは、画素パケットを処理するためのスカラ算術演算を行うことのできるプログラマブル算術論理演算装置(ALU)段を有する。画素パケット内のオペランドは、ダイナミックレンジを改善するためにS1.8形式でフォーマット設定されてもよく、異なるデータ形式でフォーマット設定されてもよい。グラフィックスプロセッサは、構成可能なグラフィックスパイプラインとして実施されてもよい。一実装形態では、パイプラインを通る画素パケットのプロセスフローが、ホストからのコマンドに応答して再構成され得るようにするために、分配器がグラフィックスパイプラインの要素を結合する。各画素は、偶数画素または奇数画素に割り当てられ、次いで、奇数と偶数の画素の画素パケットがALU待ち時間を引き受けるようにインターリーブされてもよい。 (もっと読む)

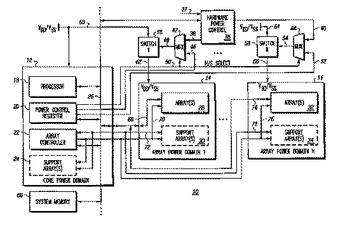

回路アレイの漏れ電流を低減するための集積回路電力管理及びそのための方法

漏れ電流は、メモリ・アレイ(28)とインターフェースするプロセッサ(18)を有する処理システム(12)の低電力モードの間に当該メモリ・アレイの中で排除される。2つの電力プレーンが生成されるので、プロセッサ(18)は、アレイがパワーダウンされるときメモリ・アレイ(28)をバイパスしながら、システム・メモリ(80)を用いて命令を実行し続け得る。スイッチ(56)が、命令の実行から、又はプロセッサ以外のどこかのシステムで発生するソースから結果として生じるプロセッサにより開始された制御に応答して電圧供給端子に対する電気接続を選択的に取り去る。メモリ(28)への電力が回復すると直ぐに、データは、メモリ・アレイに対する2つの電力プレーン・サポート・アレイのうちのどちらが配置されるかに依存して使用不能として印をされることが必要であっても、又はなくてもよい。所定の判定基準を用いて、電力の回復のタイミングを制御し得る。多重アレイが、漏れ電流を独立に低減するため実行され得る。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]