Fターム[5B005KK12]の内容

階層構造のメモリシステム (9,317) | 適用環境 (907) | 要求元 (807) | CPU (641)

Fターム[5B005KK12]の下位に属するFターム

マルチCPU (447)

Fターム[5B005KK12]に分類される特許

1 - 20 / 194

演算処理装置

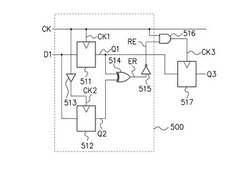

【課題】キャッシュメモリから高速にデータを読み出すことができる演算処理装置を提供することを課題とする。

【解決手段】演算処理装置は、複数の記憶素子にそれぞれ複数のデータを記憶するキャッシュメモリと、前記キャッシュメモリからデータが読み出されたタイミングが閾値より遅いときにはエラーを検出するエラー検出回路(500)と、前記エラーが検出されないときには前記キャッシュメモリから読み出されたデータをラッチし、前記エラーが検出されたときには待機期間経過後に前記キャッシュメモリから読み出されたデータをラッチするラッチ回路(517)と、前記ラッチ回路によりラッチされたデータの処理を行う演算処理装置コアとを有する。

(もっと読む)

情報処理装置、ハイブリッド記憶装置、およびキャッシュ方法

【課題】記憶装置をHDDのキャッシュとして利用する場合に、アクセス性能の低下、およびキャッシュヒット率の低下を抑制すること。

【解決手段】実施形態によれば、ホストからのハードディスクドライブへのアクセス要求に対して、前記ハードディスクドライブの設定数以上の連続するセクタのデータにアクセスするかを判定する判定手段と、記憶装置を前記ハードディスクドライブのキャッシュとして用いるキャッシュ手段であって、前記設定数以上の連続するセクタのデータにアクセスすると判定された場合に前記記憶装置をキャッシュとして用いない、キャッシュ手段とを具備する。

(もっと読む)

メモリ管理装置、メモリ管理方法、および、制御プログラム

【課題】主記憶装置の使用量を削減する。

【解決手段】メモリマネージャのメモリ管理部は、ステップS41において、ROM上のページと値が合致するRAM上のページを検出した場合、ステップS43において、値が合致するROM上のページを参照するように変換テーブルを更新し、ステップS44において、検出したRAM上のページを破棄する。本技術は、例えば、組み込み機器に適用できる。

(もっと読む)

演算処理装置および演算処理装置の制御方法

【課題】キャッシュメモリを実装した演算処理装置およびキャッシュメモリ制御装置において、プロセスIDに対応してキャッシュメモリ領域をブロック単位で任意に分割可能として、プロセッサの実効性能を向上することを可能とする。

【解決手段】各セット103のキャッシュブロック102毎に物理プロセスID(PPID)が記憶されるとともに、#1から#nの各インデックス値毎に、各PPID値に対するMAX WAY数105が記憶される。或るインデックス値における或るPPID値に対応するMAX WAY数105は、そのインデックス値において記憶可能なそのPPID値を有するキャッシュブロック102の最大数を示す。各インデックス値毎に、各PPID値のMAX WAY数105が守られるように、キャッシュミス時のウェイ数の制御が実施される。

(もっと読む)

ルータ及びメニーコアシステム

【課題】ルータ又は共有メモリの構造を複雑にすることなく、リードアクセスレイテンシを低減する。

【解決手段】ルータ14は、複数のコアと、複数のコアからアクセス可能なキャッシュメモリとの間で転送されるパケットの経路を管理する。ルータ14は、解析部144と、パケットメモリ145と、制御部143と、を備え,解析部144は、パケットがリードパケット及びライトパケットの何れかを解析し、パケットメモリ145は、発行されたライトパケットの一部を格納可能である。制御部143は、解析部144の解析結果に基づいて、ライトパケットの場合に、パケットのキャッシュデータと、格納されるべきキャッシュアドレスとを格納し、リードパケットであり、且つ、キャッシュデータがパケットメモリ145に格納されている場合に、キャッシュデータをリードパケットに対するレスポンスデータとして、コアへ出力する。

(もっと読む)

メモリアクセス制御回路、プリフェッチ回路、メモリ装置および情報処理システム

【課題】プリフェッチバッファのプリフェッチサイズを動的に切り替える。

【解決手段】モード切替レジスタ250はプリフェッチバッファ210におけるプリフェッチサイズのモード切替えをプロセッサから指示する。モード切替指示検出部225はプリフェッチバッファ210におけるプリフェッチサイズのモードを切り替える指示を検出する。転送状態監視部242はデータ転送処理部241におけるデータ転送処理が実行中か否かの状態を監視する。モード切替部227は、モード切替指示が検出された際にデータ転送処理が実行中でなければ、すみやかにプリフェッチバッファ210におけるプリフェッチサイズの切替を実行する。一方、モード切替指示が検出された際にデータ転送処理が実行中である場合には、モード切替部227はデータ転送処理の終了を待ってプリフェッチサイズの切替を実行する。

(もっと読む)

ベクトル演算処理装置、ベクトル演算処理方法およびベクトル演算処理プログラム

【課題】キャッシュメモリと主記憶装置との間の負荷を軽減し、ロードバッファの解放タイミングを早める。

【解決手段】投機的に実行されるベクトルロード命令が発行された場合に、ベクトルデータのバッファ領域M2を確保するロードバッファ管理部31と、メモリアクセスリクエストに基づいて要素データをキャッシュメモリM1又は主記憶装置9から読み出し、読み出した要素データをバッファ領域M2に格納させるキャッシュ処理部4と、投機的実行に成功した場合にバッファ領域の要素データをベクトルレジスタM3に転送してからバッファ領域M2を解放し、一方、投機的実行に失敗した場合にバッファ領域M2の要素データをベクトルレジスタM3に転送せずにバッファ領域M2を解放するベクトル処理部6とを備え、キャッシュ処理部4は投機的実行に失敗した場合に要素データの主記憶装置9からの読み出しを抑止する。

(もっと読む)

プログラマブルコントローラ

【課題】ラダー言語用のビット演算プロセッサを備えるプラグラマブルコントローラにおいて多発する、リードモディファイライトによるパイプライン処理の中断を防ぐ。

【解決手段】リードモディファイライトの対象データをバッファレジスタにロードするとともに対象データのアドレスをレジスタファイル152に保持しておくパイプラインステージR(リードステージ)の後ろに、ビット演算及びビットデータのマージを行うパイプラインステージEX(実行ステージ)を設け、その後ろにリードステージRにて保持したアドレスにマージ結果をストアするパイプラインステージW(ライトステージ)を設ける。

(もっと読む)

情報処理装置及び情報処理方法

【課題】キャッシュメモリが無効な状態でキャッシュライン中の複数の要素データをアクセスするロード命令に関し、実行性能を向上させる。

【解決手段】

情報処理装置400は、プロセッサ410、主記憶420、ネットワーク430を備え、主記憶420に記憶された要素データのうち、命令で指定された複数の要素データを1命令でアクセスできるメモリアクセス命令を命令セットに含む。プロセッサ410は、メモリアクセス命令に従って主記憶420にアクセスする場合に、メモリアクセス命令ごとに指定されたキャッシュラインの有効/無効と、当該キャッシュライン中における要素データの有効な数又は位置の少なくとも1つと、に基づいてアクセス対象バンクへの最適なアクセス単位を判定し、当該判定したアクセス単位でメモリアクセスリクエストを生成し、発行するメモリアクセスリクエスト生成発行手段440を備える。

(もっと読む)

ディスクアレイ装置のエラー制御方法

【課題】ディスクアレイ装置に接続されるハードディスクのエラー処理が影響して,データ読出し/書き込みの応答時間が遅延することを抑止することである。

【解決手段】冗長化された記録デバイスが接続される状態において,ディスクアレイ装置から記録デバイスに対するコマンド発行時にホストコンピュータ応答用の記録デバイス処理時間を監視する事により,所定の時間を経過した場合に記録デバイスからの応答が無くてもホストコンピュータへ正常応答する事により,短時間での応答時間を実現する。

(もっと読む)

メモリ制御装置、メモリ制御方法

【課題】DRAMを主記憶に使用しLSI内蔵メモリを一時記憶として使用するメモリシステムにおいて、DRAMへの書き戻し時間を短くする。

【解決手段】内蔵メモリからDRAMへの書き戻し時に同一のDRAMページのアクセスは連続して発行されるようにアクセス順序を生成し、別のDRAMページへのアクセスは直前に書き戻しを行ったDRAMバンクと異なるバンクとなるようにアクセス順序を生成する。さらに、内蔵メモリをキャッシュとして使用し、キャッシュ内に保持されたデータの無効化を行う際に同一のDRAMページに対応するエントリは連続して無効化し、別のDRAMページに対応するエントリは直前に無効化したDRAMバンクとは異なるバンクとなるように無効化する。

(もっと読む)

メモリアクセス判定回路、メモリアクセス判定方法、キャッシュ制御装置および電子機器

【課題】データ処理の高速化を可能とすること。

【解決手段】キャッシュ制御部32のキャッシュ判定部33は、カウンタ部22のカウント値CTに対応するアドレスADRをキャッシュ判定する。基準値算出部49は、アドレスADRに対するキャッシュヒットのヒット率HRと、キャッシュミスのときにカウント値CTに対応するアドレスADRに対するキャッシュミスのミス率MRとに基づいて、カウンタ部22がカウント値CTをカウントするための基準値m,nを変更する。

(もっと読む)

可変長命令の固定数を持つ命令キャッシュ

【課題】可変長命令の存在のもとで命令キャッシュアクセスを改善する。

【解決手段】可変長命令の固定数が、命令キャッシュの各ライン200,260に記憶される。可変長命令I1〜I8は予め定められた境界に沿って整列される。ラインの各命令の長さ、従って命令が占めるメモリのスパンが知られていないので、次に続く命令のアドレス240,300が計算され、キャッシュラインで記憶される。命令境界を確認し、命令を整列させ、次のフェッチアドレスを計算することは、キャッシュに命令を置く前にプレデコーダで行なわれる。

(もっと読む)

アドレス変換検査装置、中央処理演算装置、及びアドレス変換検査方法

【課題】メモリ管理装置に設けられたバッファに読み込まれた変換テーブルを用いて、中央処理演算装置が物理メモリへ正常にアクセスできるか否かを他のプログラムを実行したままで検査する。

【解決手段】情報処理装置10は、物理メモリのアドレスである物理アドレスと仮想メモリのアドレスである仮想アドレスとを変換するための変換テーブルに基づいて、前記仮想アドレスと前記物理アドレスとを変換するMMU20を備えている。そして、RAM14には、ページテーブルを示すページテーブル情報、及びページテーブル情報に付加され、MMU20による仮想アドレスと物理アドレスとの変換の異常の有無を検出するための異常検出情報が記憶されている。そして、CPU12は、異常検出情報に基づいて、MMU20による仮想アドレスと物理アドレスとの変換の異常の有無を検出する。

(もっと読む)

メモリ管理装置及びメモリ管理方法

【課題】不揮発性半導体メモリに記憶されているデータを、高速アクセス可能な記憶装置にアクセス発生前に記憶し、効率的なアクセスを実行する。

【解決手段】実施形態に係るメモリ管理装置3は、履歴管理部16、アドレス変換テーブル13、アドレス管理部17、先読みデータ管理部18を含む。履歴管理部16は、メインメモリ4として使用される不揮発性半導体メモリ61〜6kに記憶されているデータに対するアクセス履歴を管理する。アドレス変換テーブル13は、データについての論理アドレスと物理アドレスの変換テーブルを含む。アドレス管理部17は、アドレス変換テーブル13の第1の論理アドレスに対するアクセスの後にアクセスされる第2の論理アドレスをアクセス履歴に基づき決定し、第2の論理アドレスに対応する第2の物理アドレスを第1の論理アドレスに対応付けてアドレス変換テーブル13に登録する。先読みデータ管理部18は、第2の物理アドレスに対応するデータをバッファ11に格納する。

(もっと読む)

ビデオサーバ、管理情報キャッシュ方法及び管理情報キャッシュプログラム

【課題】 管理情報を半導体記録メディアに記録する場合であっても、長期の運用に耐えることが可能なビデオサーバと、このビデオサーバで用いられる管理情報キャッシュ方法及び管理情報キャッシュプログラムとを提供する。

【解決手段】 素材データを符号化データに変換する符号化部と、前記符号化データを記録する記録部と、前記符号化部及び前記記録部を制御すると共に、前記素材データの管理情報を管理する制御部とを具備するビデオサーバにおいて、前記制御部は、メモリ、CPU、キャッシュメモリ及び接続インタフェースを備える。CPUは、メモリに記録される操作履歴に基づいて、前記管理情報が変更される可能性が高いか否かを判断し、高いと判断した場合、キャッシュメモリに管理情報を一時的に記録し、低いと判断した場合、管理情報を接続インタフェースに接続される半導体記録メディアに書き込む。

(もっと読む)

情報処理装置およびキャッシュの制御方法

【課題】取り外されたキャッシュ装置を再度取り付けた場合に、キャッシュ装置内のキャッシュデータを有効に用いること。

【解決手段】情報処理装置は、メモリと、取り外し要求検出手段と、設定手段と、無効化手段とを具備する。メモリには、キャッシュ装置に格納されているキャッシュデータを管理するための情報が記述されているキャッシュ管理情報が格納される。取り外し要求検出手段は、キャッシュ装置の取り外し要求を検出する。設定手段は、取り外し要求が検出された場合に、キャッシュとしてのキャッシュ装置の使用を中断するキャッシュ無しモードに設定する。無効化手段は、キャッシュ無しモードにおいて記憶装置に第1データを書き込む場合、キャッシュ管理情報内の第1データに対応する第1キャッシュデータに係わる情報を無効化する。

(もっと読む)

キャッシュユニット及びプロセッシングシステム

【課題】クリティカルワードファースト(CWF)非対応バスに接続されたユニットからCWF対応バスに接続されたユニットにデータが転送される場合のCWF対応バスに接続されたユニットの処理効率を改善する。

【解決手段】キャッシュユニット10は、2次キャッシュL2と、第1ラインサイズを有する1次キャッシュの第1リフィル要求のバースト転送の先頭アドレスが2次キャッシュL2に存在していない場合に、第1リフィル要求のバースト長を変更することにより、第1リフィル要求を、バースト転送の先頭アドレスが処理対象となる処理データのアドレスでありバースト長が第1ラインサイズ未満である第2リフィル要求に変換する要求変換部142と、第2リフィル要求を主記憶装置に転送し、第2リフィル要求に対応する処理データを主記憶装置から受け取り、受け取った処理データを1次キャッシュに転送する非キャッシュ制御部16を備える。

(もっと読む)

ストレージ装置及びストレージ装置のリビルド処理方法

【課題】ストレージ装置の性能を低下させずにリビルド処理の高速化を図るとともに、リビルド処理中の突発的な障害の発生にも対応すること。

【解決手段】ストレージ装置2は、ライトキャッシュを有する複数の磁気ディスク装置21、22、23と、データを冗長的に記憶するプロセッサ部11と、リビルド処理を行うリビルド実行制御部13と、リビルド処理時にリビルドしたデータを記憶する記憶装置のライトキャッシュを有効にするライトキャッシュ制御部15と、リビルド処理の進捗情報を管理する、不揮発性メモリを用いて構成されるリビルド進捗管理部14とを備える。リビルド処理中に電源断となった後電源が再投入された場合、リビルド実行制御部13は、進捗管理部で管理されるリビルド処理の進捗情報に基づいて、最後に書き込んだリビルドされたデータのアドレスからライトキャッシュの容量相当分前のアドレスを算出し、当該算出したアドレスからリビルド処理を再開する。

(もっと読む)

キャッシュ制御装置及びキャッシュ制御方法

【課題】ロード命令とストア命令が競合した場合に、データの整合性を保つことができ、かつ、処理レイテンシを低減することができるキャッシュ制御装置及びキャッシュ制御方法を提供すること。

【解決手段】本発明にかかるキャッシュ制御装置5は、メモリ2に格納されるデータを、メモリ2と上位装置との間でキャッシュするキャッシュ制御装置5である。データが格納されるデータ格納部51と、データ格納部51に対してリフィルを実行中に、上位装置からデータ格納部51にデータがストアされたか否かを示すストア情報が格納されるストア情報格納部52と、リフィルによるデータがメモリ2から出力されたときに、ストア情報格納部52に格納されたストア情報がデータがストアされたことを示す場合、メモリ2から出力されたデータを、上位装置に直接出力するリプライ制御部53と、を備える。

(もっと読む)

1 - 20 / 194

[ Back to top ]