Fターム[5B005MM22]の内容

階層構造のメモリシステム (9,317) | 階層メモリの種類 (2,100) | バッファメモリ (133) | 転送バッファ (102)

Fターム[5B005MM22]の下位に属するFターム

W/Rバッファ (56)

Fターム[5B005MM22]に分類される特許

1 - 20 / 46

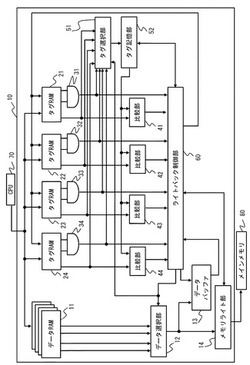

キャッシュ装置、メモリシステム及びデータ転送方法

【課題】キャッシュデータを効率的にメインメモリへライトバックすることができるキャッシュ装置、メモリシステム及びデータ転送方法を提供すること

【解決手段】本発明にかかるキャッシュ装置は、複数のキャッシュデータが、メインメモリ80に格納されている複数のデータと一致しているか否かを判定するライトバック制御部60と、複数のキャッシュデータのうち、不一致と判定されたキャッシュデータであって、メインメモリ80において連続するアドレスへ書き込まれる複数のキャッシュデータを格納するデータバッファ部13と、データバッファ部13へ格納されたキャッシュデータを一括してメインメモリ80へ書き込むメモリライト部14と、を備えるものである。

(もっと読む)

同時保留中データアクセスリクエストのためのデータハザード処理

【課題】イニシエータデバイスではなく、コヒーレンシコントローラでデータハザードを管理する、データ処理システムを提供する。

【解決手段】2つの部分形式で書き込みリクエストを処理する。同じアドレスに対し同時保留の読み出しおよび書き込みが存在する時、書き込みの第1の部分に応答しないことでコヒーレンシコントローラにより延期され、イニシエータデバイス10は、書き込みが保留中に関係なく、書き込みのアドレスに受信されたいずれのスヌープリクエストも処理するように進行する。保留中の読み出しが完了すると、コヒーレンシコントローラは、書き込みの第1の部分に応答し、イニシエータデバイスは、データおよびスヌープ後のデータの状態のインジケータを送信することによって、書き込みを完了する。コヒーレンシコントローラは、必要に応じてメモリを更新するためにこの情報を使用して潜在的なデータハザードも回避することができる。

(もっと読む)

データ供給装置、キャッシュ装置、データ供給方法、キャッシュ方法およびプログラム

【課題】 データ供給装置において、受信の際に必要となる記憶領域(受信領域)が大きい。またノンブロッキング動作のときに受信領域からデータを保持する記憶領域への転送が必要となる。データを保持する記憶領域(データ領域)と受信領域とを一体化し、受信領域からデータ領域への転送をなくし、装置全体の回路規模を抑制するための技術を提供する。

【解決手段】 フェッチ手段に備えられたデータを保持する記憶領域の一部に受信領域を割り当て、プリフェッチ手段の出力する情報に従い、受信領域の割り当てを更新してデータを取得しフェッチ手段からデータを供給する。

(もっと読む)

メモリシステム

【課題】

実施形態は、複数のバッファ部それぞれに保持されたデータを交換可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムは、データを保持可能なページバッファを含むNAND型フラッシュメモリと、前記NAND型フラッシュメモリとデータバスを介して電気的に接続された複数の記憶部と、前記NAND型フラッシュメモリ、前記複数の記憶部を制御する制御部とを備え、前記データバスの幅は、前記データの容量よりも小さく、前記制御部は、前記NAND型フラッシュメモリに書き込み又は読み出しを行うとき、前記ページバッファに保持するデータと前記複数の記憶部のうち1の記憶部に保持するータとを交換することを特徴とする。

(もっと読む)

半導体集積回路、情報記憶方法

【課題】異常画像を発生させることなく、プリフェッチの読み出し時間を短縮することができる半導体集積回路及び情報記憶方法を提供すること。

【解決手段】メモリアービタ15にメモリアクセス要求を発行する周辺回路14の有無を監視するアービタアクセス監視手段35と、周辺回路14がメモリアービタ15にメモリアクセス要求を発行してない場合に、メモリアービタにメモリアクセス要求を発行し、命令又はデータをバーストリードするバーストリード手段37と、メモリ23からバーストリードされた命令又はデータをメモリアービタよりもCPU側で記憶するバッファ手段33,34と、命令のアドレスをデコードするアドレスデコード手段31と、命令又はデータが前記バッファ手段に記憶されているか否かを判定するアドレス判別手段32と、命令又はデータが前記バッファ手段に記憶されている場合は、バッファ手段に記憶されている命令又はデータをCPUに供給する、ことを特徴とする。

(もっと読む)

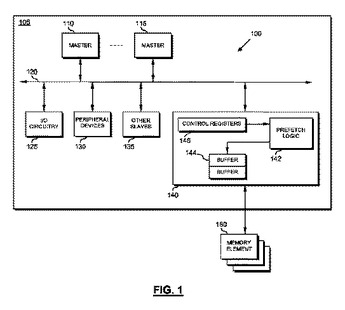

プリフェッチ・モジュールを備える信号処理システムおよび集積回路、並びにそのための方法

信号処理システム(100)は、少なくとも1つのマスタ・デバイス(110、115)と、少なくとも1つのメモリ素子(160)とを備え、さらに、少なくとも1つのマスタ・デバイス(110、115)から少なくとも1つのメモリ素子(160)へのメモリアクセス要求に応じて、少なくとも1つのメモリ素子(160)からのプリフェッチを実行するように構成されたプリフェッチ・モジュール(142)を備える。プリフェッチ・モジュール(142)は、少なくとも1つのマスタ・デバイス(110、115)からメモリアクセス要求を受信すると、メモリアクセス要求が関連するアドレスに少なくとも部分的に基づいて、そのメモリアクセス要求に関連する命令情報およびデータ情報の少なくとも一方のプリフェッチの許可を設定するように構成されている。  (もっと読む)

(もっと読む)

データ処理装置

【課題】複数の1次キャッシュ間におけるデータ転送を効率よく行なうことができるデータ処理装置を提供する。

【解決手段】本発明のデータ処理装置1は、複数の演算器11、21、32、41と、複数の1次キャッシュ12、22、32、42と、2次キャッシュ50と、順次連続的に接続された複数のバッファキャッシュ13、23、33、43とを備えている。第1段目のバッファキャッシュ13には2次キャッシュ50からデータが転送されており、複数のバッファキャッシュ13、23、33、43は、各バッファキャッシュ13、23、33、43のデータの一部を後段側に順次転送すると共に、各バッファキャッシュ13、23、33、43のデータの一部を各バッファキャッシュ13、23、33、43に対応する1次キャッシュ12、22、32、42に転送する。

(もっと読む)

オーディオデータ転送装置、転送方法およびオーディオデータ処理システム

【課題】演算装置よって処理されるマルチチャネルのオーディオデータが格納されている外部メモリと演算装置との間にキャッシュメモリシステムを配置する場合、キャッシュメモリと外部メモリとの間のデータ転送効率の悪化を抑制する。

【解決手段】オーディオデータ転送装置40は、バッファメモリ45及び先読み部44を有する。先読み部44は、外部メモリ1に格納されているn個のチャネル(ただし、nは2以上の整数)のオーディオデータのうち少なくとも一部をバッファメモリ45へ転送する処理を制御する。さらに、先読み部44は、n個のチャネルのオーディオデータのうち演算装置30によって処理されるm個のチャネル(ただし、mは1以上、n以下の整数)に応じて、m個のチャネルのオーディオデータを外部メモリ1とバッファメモリ45の間で転送する際のデータ転送サイズを調整する。

(もっと読む)

キャッシュ記憶装置

【課題】キャッシュのウェイを制限するかどうかをH/W側で判断することにより、S/W作成の負荷を軽減するキャッシュ記憶装置を提供する。

【解決手段】キャッシュ記憶装置100は、ウェイ制限開始アドレスレジスタ19とウェイ制限終了アドレスレジスタ20とからなるアドレス範囲格納部110と、ウェイ制限判定部21、置換ウェイ制御部17等を備えている。アドレス範囲格納部110は、所定のアドレスの範囲を示すアドレス範囲情報を格納する。ウェイ制限判定部21は、キャッシュ対象のキャッシュ対象データを格納するときに、キャッシュ対象データの持つアドレスがアドレス範囲格納部110のアドレス範囲情報の示す範囲内かどうかを判定する。置換ウェイ制御部17は、アドレス範囲に含まれると判定された場合には、ウェイ0、1のうち、最も過去に置換されたウェイを前記キャッシュ対象データを格納するウェイとして選択する。

(もっと読む)

メモリシステム

【課題】ホスト装置に対するコマンド処理応答を規定時間内に収めること。

【解決手段】ホスト装置に対しセクタ単位で読み出し/書き込みが行われるWC21と、ページ単位で読み出し/書き込みが行われるFS12と、トラック単位で読み出し/書き込みが行われるMS11と、FS12の入力バッファとして機能するFSIB12aと、MS11の入力バッファとして機能するMSIB11aと、が備えられるとともに、FSIB12aには、WC21の記憶容量以上の容量を有し、WC21に書込まれたデータを格納するFSBB12acが設けられる。上記各記憶部を管理するデータ管理部120は、各記憶部間で行われる処理の一つが所定時間を超えると判断した場合に、当該所定時間を超えると判断した処理を中断し、WC21に書込まれているデータをFSBB12acに退避するよう制御する。

(もっと読む)

メモリシステム

【課題】キャッシュメモリからフラッシュメモリへのデータ追い出しの処理時間を短縮化すること。

【解決手段】第2の記憶部の入力バッファとして機能する第1の入力バッファと、第3の記憶部の入力バッファとして機能する第2の入力バッファとを備え、コントローラは、第1の記憶部に書き込まれた複数のデータを第1、第2の入力バッファに追い出すキャッシュ追い出し処理と、第1、第2の入力バッファに書き込まれた複数のデータを、第2、第3の記憶部にそれぞれ追い出し、第2の記憶部に書き込まれた複数のデータを第2の入力バッファに追い出す追い出し処理および第3の記憶部内における第3の単位内の有効なデータを第4の単位で複数選択して第3の記憶部内の新たな第3の単位内に書き直すコンパクション処理を含むバッファ追い出し処理とに書き込みステージを分離する。

(もっと読む)

演算処理装置

【課題】本発明は、命令キャッシュメモリからフェッチした、リピートブロック(反復実行する命令コード群)を含む命令コードを実行するマイクロプロセッサにおいて、プログラム中のリピートブロックを実行する場合に余計な電力の消費を抑制できるようにする。

【解決手段】たとえば、プログラム中のリピートブロックの実行時、リピートブロックの最初の反復により、リピートブロックの先頭にプログラム実行が戻るタイミングから、リピートバッファ14上にリピートブロックの先頭からの命令コードの格納を開始する。リピートバッファ14への命令コードの格納を終了した後は、リピートブロックの反復により、リピートブロックの先頭にプログラム実行が戻るたびに、命令フェッチユニット18にリピートバッファ14から命令コードを供給する構成とされている。

(もっと読む)

ストレージ装置、データ回復方法及び計算機システム

【課題】容易且つ迅速にオリジナルデータを管理する論理ボリュームのデータを回復することのできる技術を提供する。

【解決手段】P−Vol10pのLU#と、S−Vol10sのLU#とを対応付けて記憶するLU管理テーブル61を備え、CPU53が、磁気テープ74へのデータの退避元のS−Vol10sのLU#を特定し、特定したLU#に対応付けられたP−Vol10pのLU#をLU管理テーブル61から取得し、磁気テープドライブ71により、データを格納した磁気テープ74から、退避されたデータを読み出させ、取得したLU#のP−Vol10pに、磁気テープ74から読み出したデータを格納させる。これにより、容易且つ適切にP−Vol10pにデータをリストアすることができる。

(もっと読む)

情報再生装置および情報再生方法

【課題】ハードウエア機能への依存を抑制した情報再生処理装置および情報再生処理方法を提供する。

【解決手段】データが一時保存される第1メモリ14と、第1メモリ14から供給されたデータを復号化する復号化手段16と、復号化手段16による復号後のデータを一時保存する第2メモリ18と、復号化手段16から供給されたデータをデコードする第1および第2デコーダ20、22と、第1デコーダ20あるいは第2デコーダ22によるデコード後のデータを一時保存する第3メモリ24と、第2メモリ28あるいは第3メモリ24のメモリ領域が再生処理に十分であるか否かを判断する判断手段Dと、判断手段Dによって第2メモリ16あるいは第3メモリのメモリ領域24が十分であると判断された際に情報再生処理を並列処理とし、第2メモリ18あるいは第3メモリ24のメモリ領域が十分ではないと判断された際に情報再生処理を直列処理とする切替手段SWを有する。

(もっと読む)

マイクロプロセッサ

【課題】未実行の命令と実行済みの命令の両方についてキャッシュヒットが可能なマイクロプロセッサを提供する。

【解決手段】プリフェッチバッファ6は、SDRAM2からプリフェッチした命令を格納する。バッファ制御部16は、書込みアドレスを表わす第1のレジスタ10内のトップホインタ、読出しアドレスを表わす第2のレジスタ12内のリードホインタおよび最も古い有効な命令の格納アドレスを表わす第3のレジスタ14内のボトムホインタに基づいて、分岐先の命令がプリフェッチバッファ6内に存在するか否かを判定し、分岐先の命令が存在するときには、リードホインタの値を分岐先の命令のアドレスを指定するように変更し、分岐先の命令が存在しないときには、トップホインタ、リードホインタ、ボトムホインタの値を初期値にリセットするとともに、分岐先の命令をプリフェッチバッファ6にプリフェッチさせる。

(もっと読む)

キャッシュ制御方法およびキャッシュ装置並びにマイクロコンピュータ

【課題】キャッシュ・メモリの容量を削減すると共に、CPUの性能低下を防ぐ。

【解決手段】前回のリード・アドレスと連続しない非順次アドレスへのリードである非順次リードがあったときに、第1のキャッシュ・メモリ回路270により該非順次アドレス、および該非順次アドレスに続くn個(n:1以上の整数)のアドレスのデータを順次キャッシングすると共に、キャッシングしたn個のアドレスのデータを第2のキャッシュンメモリ回路280に保存する。その後、次の非順次リードがなされるまで、第1のキャッシュ・メモリ回路270を介さずに、n個のアドレスの末尾のアドレスに続くアドレスのデータをメモリから第2のキャッシュ・メモリ回路280に順次読み出して保存する。非順次リードに続く各順次リードに対して、第2のキャッシュ・メモリ回路280から該順次リードのリード・アドレスのデータを出力する。

(もっと読む)

ベクトル処理装置及びベクトル処理システム

【課題】プロセッサ−メモリ間のデータ転送遅延を抑制し、処理の迅速化を図る。

【解決手段】ベクトルプロセッサ31、32、…、3nとメモリ制御部41、42、…、4mとを備えるベクトル処理装置であって、ベクトルプロセッサ31、32、…、3nは、命令種別と、ベースアドレス、ディスタンス、及び要素数からなる命令内容とに基づいて、メモリアクセスに関する制御情報を生成するメモリアクセス制御部(制御情報生成回路9)33とを有してなるとともに、生成された前記制御情報に基づいて、キャッシュ登録有無、又は/及び登録サイズを切り替えるポートキャッシュ36とを有すると共に、前記メモリ制御部41、42、…、4mは、生成された前記制御情報に基づいて、キャッシュ登録有無、又は/及び登録サイズを切り替えるバンクキャッシュ44と、メモリアクセス単位を切り替えるメモリバンク44とを備えている。

(もっと読む)

ハブ装置、プリフェッチ・モードを選択するための方法、メモリ・システム及びメモリ・サブシステム

【課題】メモリ装置用のプリフェッチ機能の可能化及び不能化のうち何れか一方を動的に選択するためのシステム及び方法を提供する。

【解決手段】

ハブ装置は、入力コマンド・ストリーム・インタフェース及び適応的プリフェッチ論理装置(APLU)を含む。前記入力コマンド・ストリーム・インタフェースは、前記ハブ装置に接続された1つ以上のメモリ装置に向けられる、メモリ・コントローラからのコマンドを検出する。前記APLUは、前記メモリ装置に対するアクセス・パターンを決定するためにこれらのコマンドを独立的に分析するとともに、かかる分析の結果に基づいて、前記メモリ装置用のプリフェッチ機能の可能化及び不能化のうち何れか一方を動的に選択する。

(もっと読む)

情報処理装置、ECC制御装置およびECC制御方法

【課題】バッファーメモリの使用効率およびアクセス速度を出来るだけ落とさずに、最適なECC制御を行う。

【解決手段】情報処理装置1は、データおよび当該データを訂正するためのECCを格納するバッファーメモリ5と、バッファーメモリから転送されるデータおよびECCを取り込んで、データおよびECCを格納するキャッシュメモリ20と、バッファーメモリからキャッシュメモリにデータおよびECCが転送される場合に、データをECCを用いて訂正するECC処理部28と、キャッシュメモリに格納されたデータを利用して処理を行うプロセッサ12と、を有するECC制御装置10を備える。

(もっと読む)

ストレージ装置、ストレージコントローラ、及び情報処理装置

【課題】情報処理装置からHDD等のストレージ装置に対するデータ記録処理動作における消費電力及び所要時間の削減を実現できる技術を提供する。

【解決手段】情報処理装置(ホスト)からストレージドライブ(SD)であるHDDのディスクに対するデータ記録処理において、そのDMA転送を、SDのメモリ上に用意したライトバッファ(WB)を境にパイプライン化し、この動作のためのコマンドをSDに追加した構成である。HDC(コントローラ)は、情報処理装置のCPUからのコマンドを解釈し、主記憶に対するDMAリードを試みてWBに蓄積し、蓄積した一定量のデータを駆動部のディスクに一気に書き込む。直後、HDCは、ファイル管理情報をディスクのFAT領域に書き込んで、自発的にアクティブ状態からスタンバイ状態に遷移させることにより節電する。

(もっと読む)

1 - 20 / 46

[ Back to top ]