Fターム[5B005MM23]の内容

階層構造のメモリシステム (9,317) | 階層メモリの種類 (2,100) | バッファメモリ (133) | 転送バッファ (102) | W/Rバッファ (56)

Fターム[5B005MM23]に分類される特許

1 - 20 / 56

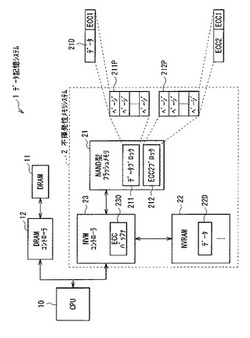

メモリシステムおよびその動作方法

【課題】動作速度を低下させることなくシステムの信頼性を向上させることが可能なメモリシステムおよびその動作方法を提供する。

【解決手段】不揮発性メモリシステム2は、ブロック(ページ)単位でデータのアクセスが行われるNAND型フラッシュメモリ21(第1の不揮発性メモリ)と、ワード単位でデータのランダムアクセスが行われるNVRAM22(第2の不揮発性メモリ)と、NAND型フラッシュメモリ21およびNVRAM22の動作の制御を行うNVMコントローラ23(制御部)とを備えている。NVRAM22のデータに適用されるエラー訂正コードECC2が、NAND型フラッシュメモリ21内に保持されている。NVRAM22に対するアクセス速度の低下が回避されつつ、このNVRAM22におけるデータ保持特性が改善される。

(もっと読む)

共有されるL2マッピング・キャッシュのための対称的割り当てのための方法およびシステム

【課題】タイル式メモリからデータを読み取るための方法、装置、システムおよび媒体を提供する。

【解決手段】一つのタイル式X方式キャッシュ読み取り要求について、そのタイル式X方式キャッシュ読み取り要求を分解することなくタイル式メモリから二つのキャッシュ・ラインを要求する段階305と、二つの要求されたキャッシュ・ラインに関連付けられたデータを返す段階325とを含む。また、二つのキャッシュ・ラインを並列に割り当てる段階310と、二つのキャッシュ・ラインの整合性を並列に維持する段階315と、二つのキャッシュ・ラインに関連付けられたデータをデータ・キャッシュから並列に読む段階320を含む。

(もっと読む)

プロセッサシステム

【課題】メインメモリから同じデータを2度読み出さない形で画像処理を実行可能な、大容量のキャッシュメモリを内蔵させることなく低消費電力で実現できるプロセッサシステムを、提供する。

【解決手段】プロセッサシステム10は、或るブロックのデータの掃き出し時にそのデータの書戻要求を発行するキャッシュメモリ12と、キャッシュメモリ12からの書戻要求に基づき、再度キャッシュメモリ12内に読み込ませることが必要なデータをローカルメモリ14上に用意し、キャッシュメモリ12からのリード要求にローカルメモリ14上のデータを利用して応答するインターコネクト13とを備える。

(もっと読む)

キャッシュを搭載した情報装置及びそれを用いた情報処理装置並びにプログラム

【課題】従来の不揮発性メモリはリードキャッシュあるいはライトキャッシュとして使用した場合、その書き換え耐性が低いために、キャッシュとしての効果の持続性が短い、あるいは、そのリード速度あるいはライト速度が遅いために速度向上効果が低い、あるいはまたリード時あるいはライト時の消費電力が大きいために省電力効果が低い、等の問題があった。

【解決手段】リードキャッシュ及びライトキャッシュを、特性の異なる2種類の不揮発性メモリで構成する。例えば、ライトキャッシュに書き換え耐性の高い不揮発性メモリを、リードキャッシュに書き換え耐性の低い不揮発性メモリを割り当て、それらのキャッシュにおけるデータの管理テーブルを書き換え耐性の高い不揮発性メモリに記憶する。あるいはまた、ライトキャッシュにはライト速度が速くリード速度が遅い不揮発性メモリを、リードキャッシュにはリード速度が速く、ライト速度が遅い不揮発性メモリを採用する。

(もっと読む)

ストアマージ装置、情報処理装置、ストアマージ方法およびプログラム

【課題】主記憶上の異なるアドレスに対するストア命令が中央処理装置から出力された場合にも記憶装置へのアクセスを抑える。

【解決手段】ストアバッファ回路12が、複数のストア命令を記憶しておく。そして、ストアバッファ回路12は、中央処理装置60からストア命令が出力されると、当該ストア命令と主記憶装置70上で同一のアドレスに対するストア命令を記憶しているか否かを判定し、記憶していると判定した場合は、この記憶しているストア命令をマージ回路11に出力する。これにより、主記憶装置70(記憶装置)へのアクセスを抑えることができる。

(もっと読む)

ディスクアレイ装置間のリモートコピー処理システム、処理方法、及び処理用プログラム

【課題】少ないバッファで非同期順序保証コピーを実現できるディスクアレイ装置間のリモートコピー処理システムを提供する。

【解決手段】更新データを格納する送信用データバッファ26Dを設ける。ホスト10からディスクアレイ装置20に更新データ(Z1)の書き込み要求があった場合、更新データ(Z1)が前回に書き込み要求があってキャッシュ22に書き込まれている更新データ(Z0)と重複していない時は、その更新データ(Z1)をキャッシュ22に書き込む。これに対して、更新データ(Z1)が前回の更新データ(Z0)と重複している時は、キャッシュ22に格納されていた前回の更新データ(Z0)を送信用データバッファ26Dにコピーした後に、その更新データ(Z1)をキャッシュ22に書き込む。このように同じ領域に書き込みがあった場合のみ送信用データバッファ26Dにデータを書き込む。

(もっと読む)

キャッシュメモリ、キャッシュメモリシステム

【課題】よりキャッシュヒット率を向上させたキャッシュメモリを提供する。

【解決手段】キャッシュメモリ6は、4つのワード(Word0,Word1,Word2,Word3)を含むラインを有するデータ格納部16と、各ラインを識別するタグを格納するタグ格納部14を備える。タグ格納部は、ラインがリフィル中であるか否かを示すリフィルビット(R)と、ワード毎にワードにおけるデータがダーティであるか否かを示すダーティビット(D0,D1,D2,D3)と、ラインに格納されたデータの主記憶におけるアドレスを示すタグビット(Tag)を格納している。ヒット判定器20は、リードアクセス対象のタグアドレス(AD[31:16])とタグビット(Tag)に示されるアドレスとが一致し、リードアクセス対象に係るラインに対応するリフィルビット(R)がリフィル中を示し、かつ、当該ラインに含まれリードアクセス対象に係るワードに対応するダーティビットがダーティを示していれば、リードヒットと判定する。

(もっと読む)

データ処理装置およびデータ処理プログラム

【課題】 データ処理装置において、ストレージへのデータバッファリングに起因する後段処理の遅延を低減する。

【解決手段】 メインコントローラー2は、書込側スレッド31aから読出側スレッド32aへ、HDD4におけるファイルの識別子を通知した後に、書込側スレッド31aで一連の複数のバンドデータのそれぞれについてのデータ書込要求を順番にキューイングし、ファイル書込スレッド31bを用いて、キューイングされたデータ書込要求の順番で、HDDコントローラー14に一連の複数のバンドデータを書き込ませ、読出側スレッド32aで、ファイルのファイル識別子を受領すると、一連の複数のバンドデータのそれぞれについてのデータ読出要求を順番にキューイングし、ファイル読出スレッド32bを用いて、キューイングされたデータ読出要求の順番で、HDDコントローラー14に一連の複数のバンドデータを読み出させる。

(もっと読む)

情報処理装置

【課題】フラッシュメモリのリード回数を減らし、フラッシュメモリの寿命を延ばす。

【解決手段】第1のメモリデバイスと、前記第1のメモリデバイスの誤り発生率より誤り発生率が小さく、かつ前記第1のメモリデバイスのデータがコピーされる第2のメモリデバイスと、前記第1のメモリデバイスからコピーした第2のメモリデバイス上のデータが削除された回数を第1のメモリデバイス上のデータ毎にカウントする削除回数計数部を備えた構成を有し、前記第1のメモリデバイスからデータがコピーされた第2のメモリデバイス上のデータを削除する際に前記削除回数計数部で計数された削除回数が小さいデータを削除することができ、第1のメモリデバイスのリード回数を減らすことが可能となり、ビット化けが起こる可能性が低くなると共に、リフレッシュ動作による書き換え回数が減ることで第1のメモリデバイスの寿命を延ばす。

(もっと読む)

ディスクアレイ装置、ディスクアレイシステム、及びキャッシュ制御方法

【課題】マスター権限を有しないコントローラ側にホスト装置からのライト要求があった場合にも、データの一貫性を維持しつつ、応答性能の向上を図るディスクアレイ装置、ディスクアレイシステム、及びキャッシュ制御方法を提案する。

【解決手段】ディスクアレイ装置は、マスターコントローラとスレーブコントローラとを備える構成である。スレーブコントローラは、ライトデータがバッファメモリに保存されたことを示す識別情報を前記ライト要求に付加すると、識別情報が付加されたライト要求及びライトデータをマスターコントローラに送信する。マスターコントローラは、ライトデータを保存した後、識別情報が付加されたライト要求をスレーブコントローラに送信する。スレーブコントローラは該ライト要求を受信すると、ライトデータを保存するバッファメモリの属性をバッファメモリからキャッシュメモリに変更する。

(もっと読む)

メモリ管理装置及びメモリ管理方法

【課題】不揮発性半導体メモリの寿命を延ばすとともに、シーケンシャルデータのアクセス効率及び管理効率を向上させる。

【解決手段】本発明の一態様に係るメモリ管理装置12,14は、プロセッサ2から不揮発性半導体メモリ3に書き込まれるデータが通常データの場合に、発生済みのアドレスの示す位置と通常データの書き込み位置が重ならないように第1の書き込みアドレスを発生させ、シーケンシャルデータの場合に、シーケンシャルデータをシーケンシャルに格納するための書き込み位置を示す第2の書き込みアドレスを発生させる手段16と、発生した書き込みの新しさを表わす順序情報を発生させる手段17と、第1の書き込みアドレスが発生された場合に、第1の書き込みアドレスに対して、発生された順序情報を対応付けて通常データを書き込み、第2の書き込みアドレスが発生された場合に、第2の書き込みアドレスに対して、シーケンシャルデータをシーケンシャルに書き込む手段18とを具備する。

(もっと読む)

処理ユニットのローカルメモリ読み出し

【解決手段】

処理ユニットのローカルメモリに対する効率的な読み出しを可能にするためのシステム、装置及び方法がここに開示される。ある実施形態においては、処理ユニットは、インタフェース及びバッファを含む。インタフェースは、(i)他の処理ユニットのローカルメモリの領域におけるデータの一部分に対する要求を送ると共に(ii)要求に応答して領域からの全てのデータを受信するように構成される。バッファは、他の処理ユニットのローカルメモリの領域からのデータを記憶するように構成される。

(もっと読む)

マルチプロセッサ環境におけるトランザクションベースの共有データオペレーション

【課題】トランザクショナル実行によるロックのない同期を利用して複数のプロセッサ間での共有メモリアクセスをハンドリングする。

【解決手段】ソフトウェアで境界設定されたトランザクションが投機的に実行される。実行中、共有メモリからロードされたアドレス及び共有メモリに書き込まれるアドレスに対する無効リモートアクセス/要求が、トランザクションバッファによって追跡される(605)。無効化アクセスに遭遇した場合、トランザクションは再実行される(610)。トランザクションを所定の回数だけ再実行した後(615)、トランザクションは、ロック/セマフォで非投機的に再実行することができる(620)。

(もっと読む)

キャッシュメモリ装置、半導体集積回路および演算処理装置

【課題】配線コストを抑えつつ、演算処理部から主記憶部へのデータ書出しに要する時間を短縮する。

【解決手段】演算処理部20によって書出されたデータを一時的に保持するデータメモリ11と、演算処理部20からデータメモリ11への入力経路L50とデータメモリ11から主記憶部30への出力経路L60とを接続する接続部12と、出力経路L60に設けられ、データメモリ11から出力されるデータまたは演算処理部20から接続部12経由で転送されるデータの何れか一方を選択して出力経路L60へ転送する選択部14と、データメモリ11から主記憶部30へデータを書出す場合には、選択部14を制御して、データメモリ11から出力されるデータを出力経路L60へ転送させ、演算処理部20から主記憶部30へデータを書出す場合には、選択部14を制御して、該データを接続部12経由で出力経路L60へ転送させる制御部13とを備える。

(もっと読む)

キャッシュ装置

【課題】高速なアクセスを可能とすること。

【解決手段】キャッシュ装置12は、CPU11とキャッシュメモリ21との間にライトバッファ22a,22bを有する。制御回路26は、CPU11からのアクセス要求に基づいて、キャッシュミスが発生した場合には、CPU11の出力データをライトバッファ22a,22bに格納するとともに、アクセス要求に対応するデータを含むラインのデータをメインメモリからデータを読み出してキャッシュメモリ21に書き込む。そして、制御回路26は、ライトバッファ22a,22bに格納したデータをキャッシュメモリ21に転送する。

(もっと読む)

半導体ディスクシステムのバッファキャッシュプログラミング方法およびバッファキャッシュプログラミング装置

【課題】半導体ディスクシステムにおけるバッファキャッシュのプログラミング方法および装置を提案する。

【解決手段】本発明の実施形態に係る半導体ディスクシステムのバッファキャッシュプログラミング装置は、ページを格納するバッファキャッシュ部と、複数のメモリチップを備えるメモリ部と、前記複数のメモリチップのうち少なくとも1つの目標メモリチップに格納する時に発生し得る待機時間を考慮して前記ページのうち少なくとも1つのページを犠牲ページとして選択する制御部とを備える。

(もっと読む)

メモリ制御装置およびカメラシステム

【課題】カメラシステムにおいてアクセス先アドレスが頻繁に切り替わるデータの処理に関しては、データの先読み機能が有効に発揮されない。最小限のメモリ追加によるシステム構成で、アクセスアドレスを随時切り替える必要のある特定のアクセスパターンにおいても、高速なアクセスを実現し、高いアクセス効率を確保する。

【解決手段】メモリ制御部7が外部メモリ30にアクセスする際のアドレスを取得するアドレス取得手段10と、順次取得されるアドレスの差分情報を一時記憶するアドレスメモリ部11と、差分情報を基に順次アクセスのアドレスが一定周期をもつかを認識する周期認識手段12と、一定周期の連続回数が閾値を超えるか否かを判定する一定周期判定手段14とを備える。メモリ制御部7は、一定周期の連続回数が閾値を超えると判定されたときに先読み機能をアクティブにし、次回アクセスが予想されるアドレスに従って外部メモリに対し先読みのアクセスを行って、その先読みデータをバッファ部9にバッファリングする。

(もっと読む)

キャッシュメモリ制御部を備えるデータ処理装置

【課題】データ処理のスループットが高いデータ処理装置を提供する。

【解決手段】処理対象のデータがキャッシュメモリCMに存在するかどうかを判定するキャッシュヒット・ミス判定部20と、キャッシュヒットの場合にキャッシュメモリCMから処理対象のデータを読み出し、キャッシュミスの場合に、上位メモリコントローラ120から出力される処理対象のデータをキャッシュメモリCMへ書き出すとともに、データ要求元へ出力するキャッシュメモリ読出し書込み部40との間に、キャッシュヒット/ミスの判定結果とブロック内読出位置情報とを先入れ先出しで格納するFIFOメモリ30を介挿する。

(もっと読む)

メモリ・コントローラ

【課題】 複数のアプリケーションを用いるシステムでも、アプリケーションの種類に応じた最適な割合にメモリ領域を再構成するメモリ・コントローラを提供する。

【解決手段】 マイクロプロセッサと主記憶装置の間で送受信される信号を一時的に記憶するキャッシュ・メモリを備えたメモリ・コントローラにおいて、

前記マイクロプロセッサと前記主記憶装置の間で送受信される各アクセス方式の信号がそれぞれどのような割合で存在するか解析するアクセス解析装置と、

このアクセス解析装置から出力された信号に基づいて、前記キャッシュ・メモリの領域の割合を再構成するメモリ再構成装置と

を備える。

(もっと読む)

ストレージサブシステム、及びこれを有するストレージシステム

【課題】複数の種類の記憶デバイスを備えても、キャッシュメモリから複数の種類の記憶デバイスへのライト処理が停滞しないストレージサブシステムを提供する。

【解決手段】HDDおよびSSDに、キャッシュメモリからのライトデータの書込み性能に優劣があっても、書込み性能が低いSSDに対するキャッシュメモリ13A,13BをHDDに対するキャッシュメモリ12A,12Bから区別して設けた。

(もっと読む)

1 - 20 / 56

[ Back to top ]