Fターム[5B005PP03]の内容

階層構造のメモリシステム (9,317) | 一致制御 (671) | 下位のメモリの一致制御 (259) | コピーバック方式 (218)

Fターム[5B005PP03]に分類される特許

1 - 20 / 218

ソフトエラー耐性調整機能を備えた電子システム装置及びソフトエラー耐性調整方法

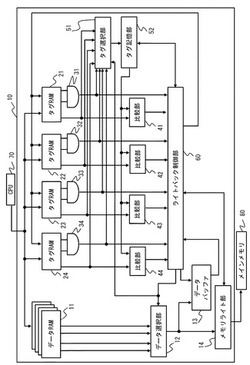

キャッシュ装置、メモリシステム及びデータ転送方法

【課題】キャッシュデータを効率的にメインメモリへライトバックすることができるキャッシュ装置、メモリシステム及びデータ転送方法を提供すること

【解決手段】本発明にかかるキャッシュ装置は、複数のキャッシュデータが、メインメモリ80に格納されている複数のデータと一致しているか否かを判定するライトバック制御部60と、複数のキャッシュデータのうち、不一致と判定されたキャッシュデータであって、メインメモリ80において連続するアドレスへ書き込まれる複数のキャッシュデータを格納するデータバッファ部13と、データバッファ部13へ格納されたキャッシュデータを一括してメインメモリ80へ書き込むメモリライト部14と、を備えるものである。

(もっと読む)

部分読出と非スヌープアクセスとの間のメモリ順序付け要件の充足

【課題】部分的且つ非コヒーレントなメモリアクセスの観点からキャッシュ・コヒーレンス・リンクに基づく相互接続でメモリ順序付けを保つ方法及び装置を提供する。

【解決手段】例えば部分書込のような部分的なメモリアクセスに関連するコンフリクトが検出される場合に、ライトバックフェーズがコンフリクトフェーズで挿入され、ホームエージェントへ部分的データをライトバックする。コンフリクトフェーズでライトバックフェーズを挿入するメッセージの例には、コンフリクトを認めて、コンフリクトフェーズの開始時にライトバックマーカーを、コンフリクトフェーズ前にライトバックマーカーメッセージを、コンフリクトフェーズ内でライトバックマーカーメッセージを、コンフリクトフェーズ後にライトバックマーカーメッセージ及びポスタブル・メッセージを提供するAcknowledge Conflict Write-backメッセージがある。

(もっと読む)

低電力モード中にキャッシュされた情報を保存する技術

【課題】コンピューティング・システムおよびマイクロプロセッサ内の電力管理分野に関するプロセッサ、システム、および、方法を提供する。

【解決手段】低電力モード中にキャッシュされた情報を保持するための技術である。プロセッサ100のローカル・キャッシュ107,113に格納された情報は、プロセッサが低電力モードに置かれる前に共有キャッシュ115に保存されるので、他のプロセッサは、低電力モードのプロセッサを、そのローカル・キャッシュへのアクセスを提供するように低電力モードから復帰させる代わりに、共有キャッシュからの情報にアクセスする。

(もっと読む)

制御システム、制御方法およびプログラム

【課題】消費電力量を低減可能な制御システム、制御方法およびプログラムを提供する。

【解決手段】制御システム100は、検出部51と推定部52と判断部53と制御部54とを備える。検出部51はアイドル状態を検出する。推定部52はアイドル時間を推定する。判断部53は、アイドル状態が検出された場合、主記憶装置への書き戻しが必要なデータの書き戻しを行ってキャッシュメモリに対する電力の供給を停止した場合の第1消費電力量が、当該データの書き戻しを行わずにアイドル時間にわたってキャッシュメモリに対する電力の供給を継続した場合の第2消費電力量よりも大きいか否かを判断する。制御部54は、第1消費電力量が第2消費電力量よりも小さいと判断された場合は、キャッシュメモリに対する電力供給を停止させる一方、第1消費電力量が第2消費電力量よりも大きいと判断された場合は、キャッシュメモリに対する電力供給を継続させる。

(もっと読む)

キャッシュメモリ装置、プロセッサ、および情報処理装置

【課題】十分な消費電力の削減が図ることができるキャッシュメモリ装置を提供する。

【解決手段】キャッシュメモリ装置100aは、記憶装置のデータをキャッシュする。キャッシュメモリ装置100aは、記憶部110aと、制御部120aと、を備える。記憶部110aは、複数のキャッシュラインを有する。制御部120aは、前記複数のキャッシュラインのうち、前記記憶装置に書き込まれていないデータを含むダーティラインの数が予め定めた所定数を超える場合に、前記ダーティラインのデータを前記記憶装置に書き込む。

(もっと読む)

マルチプロセッサ・システムにおけるキャッシュ・コヒーレンスにおいて用いるフォワード状態

【課題】修正、排他的、共有、無効、及びフォワード(MESIF)の5つの状態を有するキャッシュ・コヒーレント・プロトコルを提供する。

【解決手段】MESIFキャッシュ・コヒーレント・プロトコルは、更なる複製を行い得る、データの単一複製を指定するフォワード(F)状態を含む。F状態におけるキャッシュ・ラインは、キャッシュ・ラインの複製の要求に応答するのに用いられる。一実施例では、新たに作成される複製がF状態に置かれ、先行してF状態にあったキャッシュ・ラインは共有(S)状態又は無効(I)状態に置かれる。よって、キャッシュ・ラインが共有されている場合、1つの共有複製はF状態にあり、キャッシュ・ラインの残りの複製はS状態にある。

(もっと読む)

共有キャッシュメモリ制御

【課題】データ共有の効率性とキャッシュ記憶容量の使用との間でバランスのとれた共有キャッシュメモリの制御が可能なデータ処理装置を提供する。

【解決手段】データ処理システムは、複数のローカルキャッシュメモリと、共有キャッシュメモリとを有する、キャッシュ階層を含む。キャッシュライン毎に共有キャッシュメモリ内に記憶された状態データは、データのキャッシュラインがキャッシュメモリシステムの非包括的動作または包括的動作にしたがって記憶または管理されているかどうかを制御するために用いられる。スヌープトランザクションは、データのキャッシュラインが一意的であるかまたは非一意的であるかどうかを示すデータに基づいてフィルタリングされる。非包括的動作から包括的動作への切り換えは、データのキャッシュラインを要求する、受け取られたトランザクションのトランザクション種別に応じて、実行されてもよい。

(もっと読む)

マルチコアプロセッサシステムおよびマルチコアプロセッサ

【課題】キャッシュの一貫性をソフトウェアで維持することができるクラスタ型のマルチコアプロセッサシステムを得ること。

【解決手段】メモリ領域は、1次キャッシュおよび2次キャッシュをともに使用する第1のアクセスによる読み書きが許可され、1つのタスクに独占的な使用権が与えられている第1の状態と、2次キャッシュのみ使用する第2のアクセスによる読み書きが許可され、1つのプロセスに独占的な使用権が与えられている第2の状態と、キャッシュを使用しない第3のアクセスによる読み書きが許可され、全てのプロセスに使用権が与えられている第3の状態とを容認する。カーネル部は、第1の状態から第2の状態に遷移させるとき、1次キャッシュを2次キャッシュにライトバックし、第2の状態から第3の状態に遷移させるとき、2次キャッシュをメモリ領域にライトバックする。

(もっと読む)

データ処理システムのシステムメモリへのデータの書き込み

【課題】システムメモリへのデータの書き込みの際の遅延を減少させる方法およびシステムを提供する。

【解決手段】システムメモリの領域のユニークなセクションに各々関連する複数のキャッシュ線に対応する状態インジケータは、キャッシュ線が関連するセクションにそのキャッシュ線に格納されているデータを書き込む候補であることを示すダーティ指示を含む。ダーティ指示を含む状態インジケータの数を判定し、判定したダーティ指示の数が閾値を超える場合、キャッシュ線を選択し、そのキャッシュ線に格納されているデータをシステムメモリの領域の関連するセクションに書き込み、対応する状態インジケータにクリーン指示を格納する。クリーン指示によって、キャッシュ線がシステムメモリの領域の関連するセクションにそのキャッシュ線に格納されているデータを書き込む候補でないことが識別される。

(もっと読む)

情報処理装置およびプログラム

【課題】2次ストレージへの書き込み頻度を下げて消費電力を下げる。

【解決手段】実施形態の情報処理装置は、補助記憶部と、主記憶部と、蓄電部と、第1書込部と、第2書込部と、を備える。主記憶部は、補助記憶部に記憶するデータを一時記憶するキャッシュ領域を含む不揮発性の記憶部である。第1書込部は、データをキャッシュ領域に書き込む。第2書込部は、蓄電部の電力量が予め定められた第1閾値より大きい場合に、キャッシュ領域に書き込まれたデータを補助記憶部に書き込む。

(もっと読む)

退避処理装置、及び、退避処理方法

【課題】複雑な処理を行わず、キャッシュメモリに蓄積中のデータの退避処理を可能とする。

【解決手段】キャッシュメモリの退避を行う第1の不揮発性メモリと、第2の不揮発性メモリと、キャッシュメモリ内のデータにおいて、第1の不揮発性メモリの書込が失敗した領域の情報の履歴を記録した管理テーブルを記憶する記憶部と、第1の不揮発性メモリへの退避処理を行う第1の制御部と、第1の制御部から送られてくる情報を、時間情報と共に、第2の不揮発性メモリへ書きこむ第2の制御部とを有し、第1の制御部は、停電発生時に、キャッシュメモリに記憶されているデータを不揮発性メモリに書き込む処理を実行し、前記退避処理に当たり、該書込が正常に行われたかを検証するとともに、該検証にて正常に書きこまれていない場合、前記不揮発性メモリの正常な書込ができなかった領域の情報を、記憶部に記憶する。

(もっと読む)

キャッシュメモリおよびキャッシュシステム

【課題】キャッシュメモリの面積の増大を抑制しつつ、高速化する。

【解決手段】キャッシュメモリ2はタグメモリ103と、第1のダーティビットメモリ106と、有効ビットメモリ107と、データメモリ105と、を含む複数のキャッシュラインを有する複数のウエイを備える。また、キャッシュメモリ2は、前記キャッシュラインを特定するためのラインインデックスメモリ101を備える。また、キャッシュメモリ2は、前記ウエイを特定する第1のビットデータおよび前記ラインインデックスを特定する第2のビットデータを記憶するローメモリ202と、前記データメモリへのバイト単位のライトに対応したビット単位の第2のダーティビットを記憶する第2のダーティビットメモリ203と、登録された順番を規定するFIFO情報を記憶するFIFOメモリ204と、を含む複数のラインを有するDBLBシステム201と、を備える。

(もっと読む)

メモリシステム、キャッシュメモリ制御方法及びメモリ制御プログラム

【課題】ストアイン方式のメモリシステムにおいて、アクセス頻度が高いアドレスのリプレース頻度を減らし、メモリシステムの性能悪化を軽減することができるメモリシステムを提供すること

【解決手段】本発明のメモリシステムは、1stキャッシュメモリ10と1stキャッシュメモリ10に優先してプロセッサからアクセスされる1stキャッシュメモリ20と、1stキャッシュメモリ10においてキャッシュデータのリプレースを行う場合に、1stキャッシュメモリ10に格納されているキャッシュデータのうち、それぞれのキャッシュデータが過去にリプレース対象となったか否かを示す履歴情報を用いて、リプレース対象キャッシュデータを決定し、1stキャッシュメモリ20に格納されているキャッシュデータのうちリプレース対象のキャッシュデータと同一のキャッシュデータを無効化するリプレース部4と、を備える。

(もっと読む)

情報処理装置及びエラー訂正支援方法

【課題】リプライデータに訂正不能なエラーが生じたことに起因するシステムの稼働率の低下を改善しつつ、回路規模の膨大化を回避する。

【解決手段】キャッシュミスのときに、メインメモリから出力されるリプライデータRD0に対して、訂正不能なエラーの有無を検出すると共に、該検出の結果とメインメモリとを示す付加情報を付加する。上記付加情報を含むリプライデータRD1でブロックロードする際に、該リプライデータRD1に含まれる付加情報を記憶しておく。キャッシュヒットのときにキャッシュメモリから出力されるリプライデータRD2に対して、ブロックロード時に記憶しておいた付加情報が「エラーがある」を示す場合に上記付加情報を付加する。上記付加情報が「エラーが無い」を示す場合に、訂正不能なエラーの有無を検出すると共に、該検出の結果とキャッシュメモリとを示す付加情報を付加する。

(もっと読む)

ライトバック順序付けによるコヒーレンス制御

【課題】順序が狂って生じるライトバックに対処するための相互接続回路を提供する。

【解決手段】相互接続回路50は、トランザクション要求を受信するための、複数の入力ポート40,42と、トランザクション要求を出力するための、出力ポート48と、複数の入力と少なくとも1つの出力との間でトランザクション要求を伝送するための、複数の経路と、データ処理装置5によって処理されるデータ項目のコヒーレンスを維持するために、同一データ記憶位置へのトランザクション要求のうちの少なくともいくつかが、相互接続回路50を通過する順序を維持するための、コヒーレンス制御回路55と、を備え、相互接続回路50は、コヒーレンス制御回路55を経由するトランザクション要求とは無関係に、ライトバックトランザクション要求が進行するように、コヒーレンス制御回路55でライトバックトランザクション要求を制御しないように構成される。

(もっと読む)

情報処理システム

【課題】情報処理システムの消費電力を低減することで発熱量を抑え、情報処理システムの誤動作や故障を防止する。

【解決手段】異なる範囲のアドレスに割り当てられる複数の副情報処理プログラムから構成される情報処理プログラムを実行する情報処理システムにおいて、CPU501は各副情報処理プログラムにおけるキャッシュメモリ141の使用効率の算出、使用必要性(電源投入必要性)の判定をし、各副情報処理プログラムに対応したキャッシュメモリ141の電源投入/電源切断の電源制御情報を記憶する。CPU501は記憶した電源制御情報を基にキャッシュメモリ141の使用不要な副情報処理プログラム実行時において完全にキャッシュメモリ141の電源切断し、消費電力を低減する。

(もっと読む)

共有キャッシュメモリ装置

【課題】2個のプロセッサに、より高速に連携した処理を行わせることが可能な共有キャッシュメモリ装置を提供する。

【解決手段】共有キャッシュメモリ装置を、第1プロセッサが生成して第2プロセッサが利用するデータを記憶するための幾つかの監視対象記憶領域をデータメモリ部33に確保する機能、管理対象記憶領域毎に第1プロセッサによるデータの書き込みが行われたか否かを管理する機能、データの書き込みが完了していない監視対象記憶領域上のデータを要求するリード要求を受信したときに、その監視対象記憶領域へのデータの書き込みが第1プロセッサにより行われるのを待機してから、当該リード要求に応答する機能を有する装置として構成しておく。

(もっと読む)

マルチコアプロセッサシステムおよびマルチコアプロセッサ

【課題】キャッシュを利用するアクセスのみ許されるメモリ領域にかかるキャッシュの一貫性をソフトウェアで維持する。

【解決手段】状態管理部は、第1メモリ領域のうちの自マルチコアプロセッサに割り当てられている領域を、プロセッサコアに割り当てられていない第1の状態と、プロセッサコアのうちの1つに割り当てられ、読み出しおよび書き込みが実行される第2の状態と、1つ以上のプロセッサコアに割り当てられ、読み出しおよび書き込みが禁止されている第3の状態と、に分類し、前記夫々の状態間の遷移を実行する。キャッシュ/メモリ管理部は、前記状態管理部が前記第2の状態から前記第3の状態に遷移させる際、対応するキャッシュをライトバックする。

(もっと読む)

データ記憶システムおよび非同期レプリケーション方法

【課題】正データ記憶装置の判断によりデータ更新の確実な順序保証を可能とする。

【解決手段】正データ記憶装置10-1のキャッシュメモリ管理部は、第1の記憶媒体へのデータの書き込みがホスト装置13-1から指定された場合、指定されたデータをライトバックデータとして記憶するためのキャッシュ領域と、指定されたデータを副データ記憶装置10-2に送信するためのバッファ領域とを第1のキャッシュメモリに確保しそれぞれにデータを書き込む。正データ記憶装置10-1のレプリケーション管理部は、バッファ領域に記憶されたデータを未確定ライトデータとして第2のキャッシュメモリに書き込むための未確定ライトを副データ記憶装置10-2に要求し、未確定ライトデータが予め定められた量を超える場合、第2のキャッシュメモリに既に書き込まれている未確定ライトデータをライトバックデータに確定する未確定ライト確定を副データ記憶装置10-2に要求する。

(もっと読む)

1 - 20 / 218

[ Back to top ]