Fターム[5B005UU32]の内容

階層構造のメモリシステム (9,317) | メモリの構成 (535) | 多階層のメモリ構成 (167) | セカンドキャッシュ (142)

Fターム[5B005UU32]に分類される特許

1 - 20 / 142

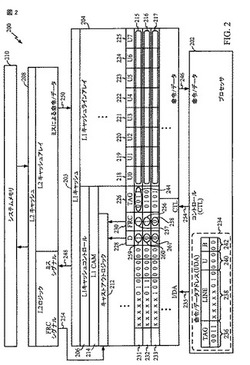

マルチレベルのキャッシュ階層におけるキャストアウトを低減するための装置および方法

【課題】下位レベルキャッシュから置換されたキャッシュラインの上位レベルキャッシュへの割り当てを低減する方法を提供する。

【解決手段】置換ラインがすでに上位レベルに割り当てられと決定されたとき、置換されたキャッシュラインの割り当ては、次のレベルキャッシュにおいて防がれ、これにより、キャストアウトが低減する。そのような目的に、ラインは、下位レベルキャッシュ204において置換されるように選択される。上位レベルキャッシュ208において選択されたラインが存在するか示す選択されたラインに関連する情報が識別される。上位レベルキャッシュにおける選択されたラインの割り当ては、識別された情報に基づいて防がれる。選択されたラインの割り当てを防ぐことは、割り当てに関連するであろう電力を蓄える。

(もっと読む)

低電力モード中にキャッシュされた情報を保存する技術

【課題】コンピューティング・システムおよびマイクロプロセッサ内の電力管理分野に関するプロセッサ、システム、および、方法を提供する。

【解決手段】低電力モード中にキャッシュされた情報を保持するための技術である。プロセッサ100のローカル・キャッシュ107,113に格納された情報は、プロセッサが低電力モードに置かれる前に共有キャッシュ115に保存されるので、他のプロセッサは、低電力モードのプロセッサを、そのローカル・キャッシュへのアクセスを提供するように低電力モードから復帰させる代わりに、共有キャッシュからの情報にアクセスする。

(もっと読む)

異なるキャッシュ・コヒーレンス・ドメインの間の情報共有技法

【課題】異なるキャッシュ・コヒーレンス・ドメイン内のエージェント間での情報共有を可能にする。

【解決手段】ある実施形態では、グラフィック装置が、情報を記憶または読み出しするために一つまたは複数の処理コアによって使用される一つまたは複数のキャッシュを使用しうる。前記一つまたは複数のキャッシュは、前記グラフィック装置に関するプログラミングおよびコヒーレンス規則に影響しない仕方で、一つまたは複数の処理コアによってアクセスされうる。

(もっと読む)

アプリケーションが決定したスケジューリングによる効率的なキャッシュの再利用

【課題】マルチプロセッサコンピュータシステにおいて効率的なキャッシュの再利用を図る。

【解決手段】コンピュータシステム100においてタスクを実行すべく複数のスレッドからスレッドを決定する方法が開示される。複数のスレッドは、コンピュータシステムのキャッシュメモリと関連付けられた少なくとも1つのサブセットにグループ化される。タスクは、命令の集合により決定された型を有する。方法は、複数のスレッドのサブセットの実行履歴を取得し、命令の集合及びデータの集合毎にタスク型に依存する重み付けを決定する。次に、実行履歴及び決定された重み付けに基づいてタスクを実行するスレッドのサブセットの適合性が決定される。決定されたスレッドのサブセットの適合性を条件として、スレッドのサブセットと関連付けられたキャッシュメモリの内容を使用してタスクを実行すべくスレッドのサブセットからスレッドを決定する方法が開示される。

(もっと読む)

メモリシステム

【課題】

実施形態は、複数のバッファ部それぞれに保持されたデータを交換可能なメモリシステムを提供する。

【解決手段】

本実施形態のメモリシステムは、データを保持可能なページバッファを含むNAND型フラッシュメモリと、前記NAND型フラッシュメモリとデータバスを介して電気的に接続された複数の記憶部と、前記NAND型フラッシュメモリ、前記複数の記憶部を制御する制御部とを備え、前記データバスの幅は、前記データの容量よりも小さく、前記制御部は、前記NAND型フラッシュメモリに書き込み又は読み出しを行うとき、前記ページバッファに保持するデータと前記複数の記憶部のうち1の記憶部に保持するータとを交換することを特徴とする。

(もっと読む)

ハードウェアのダイナミックなキャッシュパワー管理

【課題】デジタルシステムにおけるパワー管理、パワー消費を少なくさせる。

【解決手段】一実施例において、制御回路は、回路ブロックのオペレーションを再初期化するために、パワーダウンされた後にパワーアップされる回路ブロックにオペレーションを送信するよう構成される。オペレーションはメモリ(例えば、レジスタの組)に記憶され、制御回路はメモリに結合する。一実施例において、制御回路は、回路ブロックがパワーダウンされる前にメモリから回路ブロックに他のオペレーションを送信するよう構成される。したがって、システム内のプロセッサがパワーダウンされるとき(したがって、ソフトウェアはその時に実行されない)の間であっても、パワーアップ/ダウンイベントのためにプロセッサを起動させることなく、回路ブロックをパワーアップ又はパワーダウンされる。一実施例において、回路ブロックは1以上のプロセッサに結合されるキャッシュである。

(もっと読む)

キャッシュユニット及びプロセッシングシステム

【課題】クリティカルワードファースト(CWF)非対応バスに接続されたユニットからCWF対応バスに接続されたユニットにデータが転送される場合のCWF対応バスに接続されたユニットの処理効率を改善する。

【解決手段】キャッシュユニット10は、2次キャッシュL2と、第1ラインサイズを有する1次キャッシュの第1リフィル要求のバースト転送の先頭アドレスが2次キャッシュL2に存在していない場合に、第1リフィル要求のバースト長を変更することにより、第1リフィル要求を、バースト転送の先頭アドレスが処理対象となる処理データのアドレスでありバースト長が第1ラインサイズ未満である第2リフィル要求に変換する要求変換部142と、第2リフィル要求を主記憶装置に転送し、第2リフィル要求に対応する処理データを主記憶装置から受け取り、受け取った処理データを1次キャッシュに転送する非キャッシュ制御部16を備える。

(もっと読む)

メモリ管理装置およびメモリ管理方法

【課題】フラグメンテーションの発生を抑制でき、メモリの有効利用に有利なメモリ管理装置およびメモリ管理方法を提供する。

【解決手段】実施形態によれば、不揮発性半導体メモリ61〜6nと揮発性半導体メモリ5とを備えるメインメモリ65を管理するメモリ管理装置3であって、前記不揮発性半導体メモリへのデータ書き込み動作の際に、書き込み対象のデータについて、該データのデータ属性により決定される書き込み頻度についての情報22に基づき、前記不揮発性半導体メモリ上の書き込み領域の振り分けを行う振り分け部78と、前記振り分けられたデータを、追記方式により前記不揮発性半導体メモリに書き込む制御部77とを具備することを特徴とするメモリ管理装置。

(もっと読む)

キャッシュメモリ制御システム、その制御方法及び制御プログラム

【課題】処理性能を向上させることができるキャッシュメモリ制御システム、その制御方法及び制御プログラムを提供すること。

【解決手段】キャッシュメモリ制御システム1は、複数のプロセッサ11から出力される所定情報を、キャッシュメモリ12の各レベルに夫々記憶させる制御を行う。また、所定情報は、出力先のプロセッサ11を示すソース情報を含んでいる。さらに、キャッシュメモリ制御システム1は、ソース情報毎に、キャッシュメモリ12の各レベルに記憶されているソース情報の数をカウントしカウント値として算出するカウント手段と、算出されたソース情報毎のカウント値に基づいて、キャッシュメモリ12の各レベルのうち、スワップ処理の対象となるレベルの優先順位を決定する優先順位決定手段と、決定された優先順位に基づいて、キャッシュメモリ12の各レベルうち、スワップ処理を行うレベルを決定するレベル決定手段と、を備えている。

(もっと読む)

移転元処理回路と移転先処理回路との間で作業負荷を移転するためのデータ処理装置および方法

移転刺激に応答して、移転に続いて移転元処理回路が電力節約状態に入れられる準備として、処理作業負荷の実施が移転元処理回路から移転先処理回路へ移転される。移転に続いて移転先処理回路によって必要となる、メモリ取得回数を削減するために、移転元処理回路のキャッシュは、スヌープ期間中、駆動状態に維持される。スヌープ期間中、キャッシュスヌープ回路は、移転元キャッシュのデータ値をスヌープし、移転先処理回路のためにスヌープデータ値を呼び出す。  (もっと読む)

(もっと読む)

エネルギー効率のよいマルチコアプロセッサのための共用メモリ

本明細書では、プロセッサリソースを共用するように適合されたマルチコアプロセッサに関連した技術が説明される。一例示的マルチコアプロセッサは複数のプロセッサコアを含むことができる。マルチコアプロセッサはさらに、複数のプロセッサコアのうちの2つ以上に選択的に結合される共用レジスタファイルを含むことができ、共用レジスタファイルは、選択されるプロセッサコア間で共用リソースとして働くように適合される。 (もっと読む)

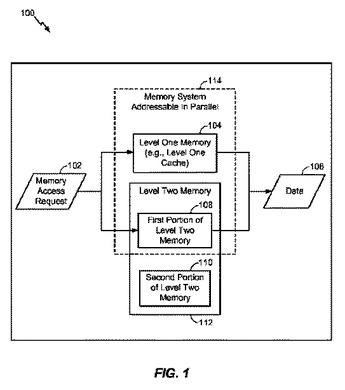

レベル2メモリの一部分とレベル1メモリとにアクセスするシステムおよび方法

レベル2メモリの一部分からのデータまたはレベル1メモリからのデータにアクセスするためのシステムおよび方法が開示される。特定の一実施形態では、本システムはレベル1キャッシュとレベル2メモリとを含む。レベル2メモリの第1の部分が入力ポートに結合され、レベル1キャッシュと並列にアドレス指定可能である。  (もっと読む)

(もっと読む)

キャッシュメモリ

【課題】キャッシュ全体のヒット率を向上させるキャッシュメモリを提供することを課題とする。

【解決手段】キャッシュメモリにおいて、キャッシュメモリに登録されているデータに優先度を付与する優先度付与手段10と、キャッシュメモリに設けられ、優先度に基づいて入れ替え対象のデータが選択される優先度有効領域12と、キャッシュメモリに設けられ、優先度に関係なく入れ替え対象のデータが選択される優先度無効領域11と、データを優先度無効領域11に登録するときに、優先度無効領域11にデータを追加登録することによって入れ替えられるデータの優先度と優先度有効領域12に登録されているデータの優先度とを比較し、当該比較結果に基づいて入れ替えられるデータを優先度有効領域12に登録するか否かを判定する判定手段10を備えることを特徴とする。

(もっと読む)

情報処理装置およびキャッシュメモリ制御装置

【課題】メモリアクセスをアウトオブオーダで処理する情報処理装置において、不要な命令再実行を確実に抑止し、処理性能の低下を招くことなく確実にTSO保証を実現する。

【解決手段】ロード命令の対象データがキャッシュ212から演算器400に転送された後にキャッシュ212のデータに対する無効化要求を受信し、受信した無効化要求の対象アドレスのキャッシュインデクスと一致するキャッシュインデクスを有するロード命令が命令ポート210に存在する場合、第1判定部214Aは、第1フラグ(RIM)を有効化する。命令ポート210のエントリに保持されたロード命令の対象データについてキャッシュミスした後に対象データが転送されてきたと判定した場合、第2判定部215Aは第2フラグ(RIF)を有効化する。命令再実行判定部216は、第1フラグおよび第2フラグがいずれも有効化されている場合に命令の再実行を指示する。

(もっと読む)

演算処理装置及び演算処理装置の制御方法

【課題】主記憶装置へのアクセス時間を短縮する。

【解決手段】第1記憶部を有する演算処理部と、第1記憶部が保持するデータの一部を保持する第2記憶部と、第2記憶部からデータを読み出し、第1論理値を取る第1属性情報を含む第1要求と、第2記憶部からデータを読み出し、且つ第1論理値と異なる第2論理値を取る第2属性情報を含む第2要求とを、演算処理部から受け取り、且つ、第1要求の完了通知を受け取るまで第1要求を保持し又は第2要求の完了通知を受け取るまで第2要求を保持する第3の記憶部と、第1及び第2要求を第3の記憶部から受け取り、且つ第1及び第2要求に対応するアドレスのデータが第2記憶部に無い場合、第1要求の第1属性情報を、第2属性情報に置き換え、且つ第2要求に対する完了通知を第1記憶部に供給する制御部とを有する演算処理装置が提供される。

(もっと読む)

マルチプロセッサシステム

【課題】キャッシュ状態のバックアップ時の電力消費を低減するマルチプロセッサシステムを提供することを課題とする。

【解決手段】キャッシュをそれぞれ備える複数のプロセッサを有し、システム停止時に各プロセッサのキャッシュの状態を外部記憶装置に順次保存するマルチプロセッサシステムであって、複数のプロセッサへの給電を管理する給電管理手段を備え、給電管理手段は、システム停止時に、複数のプロセッサの任意のプロセッサのキャッシュの状態の外部記憶装置への保存が完了する毎に、任意のプロセッサの次にプロセッサのキャッシュの状態を保存するプロセッサのキャッシュの状態の外部記憶装置への保存が完了する前に、任意のプロセッサへの給電を停止することを特徴とする。

(もっと読む)

データ処理装置

【課題】2次キャッシュにおけるキャッシュヒット率を向上させることが可能なデータ処理装置を提供すること。

【解決手段】L2制御部32は、タグメモリ34を参照して、1次キャッシュ12および22のいずれかからの要求データがデータメモリ33に格納されていると判断した場合、データメモリ33から当該データを読み出して要求があった1次キャッシュに出力し、タグメモリ34に格納される当該データに対応するタグ情報の追い出し優先順位を所定よりも高い値に設定する。したがって、2次キャッシュ31にそのデータがしばらく残ることになり、複数のCPUが同じデータに対して集中してアクセスするような場合であっても、2次キャッシュ31におけるキャッシュヒット率が低下するのを防止することが可能となる。

(もっと読む)

制御装置、記憶装置、演算処理装置および制御方法

【課題】命令データRAMの無駄な動作を抑えて低消費電力を実現する。

【解決手段】

上記課題を解決するために、データに対する命令を実行する命令制御部の要求に応じて前記データを出力する記憶装置を制御する制御装置に、前記データを保持するとともに、個別にクロックが供給される複数の個別記憶部を備える記憶部が有する複数の前記個別記憶部のうち、前記命令制御部が要求する第1のデータが記憶されている第1の個別記憶部を特定する個別記憶部特定部と、前記個別記憶部特定部が特定した前記第1の個別記憶部から、前記第1のデータを読み出して出力するデータ出力部と、前記第1の個別記憶部に前記1のデータと連続して記憶されている第2のデータを、前記命令制御部が要求する場合、複数の前記個別記憶部に対してクロックをそれぞれ供給する複数のクロック供給部のうち、前記第1の個別記憶部以外の個別記憶部にクロックを供給するクロック供給部に対して、前記クロックの供給を抑止させるクロック制御部と、を備える。

(もっと読む)

キャッシュメモリ制御装置およびキャッシュメモリ制御方法

【課題】高速で物量の小さいキャッシュメモリ制御装置およびキャッシュメモリ制御方法を提供すること。

【解決手段】対象アドレスをL1キャッシュメモリに保持するプロセッサコアが存在するか否かを示すステータスコードをL2キャッシュタグ22に付す。第1処理判定部25は、L2キャッシュタグ22でヒットした場合にステータスコードを参照して所持コアに対する処理が必要であるか否かを判定する。第2処理判定部26は、所持コアに対する処理が必要である場合にL1キャッシュタグ21を用いて所持コアを特定し、リトライ判定する。

(もっと読む)

マルチプロセッサ

【課題】キャッシュラインの転送時の消費電力を低減したマルチプロセッサを提供する。

【解決手段】メインメモリ2と、その記憶データを一時記憶するL1キャッシュメモリ11a〜11dを備える複数のプロセッサユニット1a〜1dと、L1キャッシュメモリ11a〜11dのコヒーレンシを管理するCMU3とを備え、CMU3は、L1キャッシュメモリに格納されたキャッシュラインのタグを格納するL1タグキャッシュ33a〜33dと、プロセッサユニット1a〜1dからのリフィル要求に応じてインターベンション転送を行うCMUコントローラ31と、インターベンション転送を監視することによって、転送先別に転送元を予測するPIU32とを有し、CMUコントローラ31は、PIU32の予測結果が得られた後は、予測された転送元に対応するタグキャッシュのみを活性化して、リフィル要求に対応するキャッシュラインがキャッシュされているかを判別する。

(もっと読む)

1 - 20 / 142

[ Back to top ]