Fターム[5B011LL00]の内容

電源 (19,167) | 節電(オートパワーオフを除く) (3,178)

Fターム[5B011LL00]の下位に属するFターム

漏れ電流の防止 (57)

電圧の選択制御 (217)

特別な構造 (630)

バックアップ電源の節電 (27)

節電モードへの切替 (2,150)

Fターム[5B011LL00]に分類される特許

81 - 97 / 97

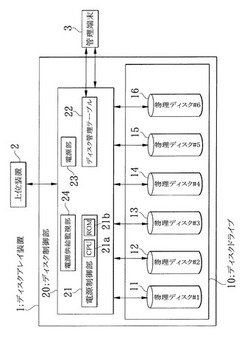

ディスクアレイ装置、該ディスクアレイ装置に用いられる電源制御方法及び電源制御プログラム

【課題】複数台のハードディスク装置の信頼性の格差が解消されると共に消費電力が低減されるディスクアレイ装置を提供する。

【解決手段】ディスク制御部20により、電源部23による各物理ディスク11,12,…,16に対する電源供給のオン/オフ状態が監視され、このオン/オフの回数に対応した各物理ディスク11,12,…,16毎の監視情報が管理され、同監視情報に基づいて、同各物理ディスク11,12,…,16に対する電源供給が個別に制御される。そして、物理ディスク11,12,…,16のうちの電源供給のオン/オフの回数が一定回数に到達している物理ディスクに対し、アクセスの完了後に所定期間だけ電源供給がオン状態に保持され、また、電源供給のオン/オフの回数が一定回数に到達していない物理ディスクは、アクセスの完了後に電源供給がオフ状態とされる。

(もっと読む)

電源制御システム

【課題】簡易な構成で消費電力の低減を図ることが可能な電源制御システムを提供する。

【解決手段】待機時に駆動する必要のある回路については、二次電池VATが電源回路VCTの代わりに電圧を供給することにより必要な駆動電圧を供給する。二次電池は、サブマイコンSPCと、電圧検知回路VDT、リモコン受信器RCと、スイッチSWを介してリレー回路RLと接続されている。電圧検知回路VDTは、二次電池VATの電圧レベルをモニタして、二次電池VATの蓄積された電荷が消費されて二次電池VATの電圧が所定電圧以下となった場合、検知信号をサブマイコンSPCに出力する。サブマイコンSPCは、検知信号に応答してスイッチSWに対して制御信号CTを出力する。スイッチSWは、制御信号CTに応答して導通し、二次電池VATからリレー回路RLの接地されたコイルLに電流が供給され、商用電源と電源回路VCTとが電気的に接続される。

(もっと読む)

プロセッサ性能計測のための重み付けされたイベント計数方法、プロセッサ、および重み付け性能カウンタ回路(プロセッサ性能計測のための重み付けされたイベント計数システムおよび方法)

【課題】短い待ち時間と、低い誤り性能測定能力とを提供する。

【解決手段】プロセッサの性能を測定するための重み付けされたイベント計数システムおよび方法において、重み付け性能カウンタ(WPC)は、プロセッサ内の機能部から与えられる複数のイベント信号に従って性能カウントを累積する。各イベントとプロセッサ性能との相関に従って、互いに異なる重みがイベント信号に印加される。重みは、プログラム制御で調整可能なように、プログラム可能なレジスタから与えられてもよい。イベント信号を合成して、互いに排他的なイベントは組み合わせ結果の単一のフィールドにマージさせ、同一の重みを有するイベントは小計に従ってマージさせて、イベント信号のセットのビット幅を減少させてもよい。重みは、組み合わせ結果に印加され、性能カウントを更新するために使用される。その後、性能カウントを、プロセッサの動作パラメータの調整のために、電源管理ソフトウェアまたはハードウェアが使用することができる。

(もっと読む)

最適制御システム、LSI最適制御回路及びそれに用いるLSI最適制御方法

【課題】 LSIの動作限界点を知り、常にLSIのマージンを知りながらを動作可能とし、徹底的な低消費電力化あるいは限界まで処理能力を高めることを可能とするとともに、LISを含むシステムを高品質かつ最適なパフォーマンスで動作可能な最適制御システムを提供する。

【解決手段】 クリティカルパスマージン測定機能102は予めLSI101の内部のクリティカルパスの限界値を測定し、その測定結果を遅延モニタ結果記憶用メモリ114に保持する。クリティカルパスマージン測定機能102は、LSI101の実動作時に、内部モニタ回路113にてクリティカルパス回路103の動作状態を測定し、LSI101内部の温度を温度測定機能115にて測定する。外部の全体最適制御回路はそのLSI101に与えるパラメータを変化させ、LSI101に与えるパラメータを最適に制御する。

(もっと読む)

電子装置

【課題】1チップマイコンにCMOSメモリを接続した電子装置において、1チップマイコンのアドレスバスのプルアップ抵抗による消費電力を低減する。

【解決手段】リセット信号がラッチ7に入力されると、そのローレベル出力によりトランジスタTR0〜TR20がオンするので、バス2及びラインLiはプルアップ抵抗RA0乃至RA20によりプルアップされる。アドレスデコーダ5で生成されたCS信号がラッチ7に入力されると、ラッチ7のハイレベル出力によりトランジスタTR0〜TR20がオフするので、バス2及びラインLiは電源から切り離される。CS信号生成後はプルアップ抵抗RA0乃至RA20の電流は0になる。

(もっと読む)

実行コードの生成方法及びプログラム

【課題】ソースコードのコンパイルから出力コードの実行までを迅速にしながらも、計算機の消費電力を確実に低減させる。

【解決手段】予め設定したコードを読み込んで、当該コードからCPUの演算量と、キャッシュメモリのアクセス量を解析する手順と、前記演算量とアクセス量に基づいて、前記CPUの実行比率と前記キャッシュメモリのアクセス実行比率を求める手順(S20)と、前記コードのうち、キャッシュメモリのアクセス実行比率が前記CPUの実行比率に比して高い領域を判定する手順(S22)と、前記キャッシュメモリのアクセス実行比率が高い領域に、前記低電力化機能を有効にするコードを付加する手順(S24)と、前記コードから前記計算機で実行可能な実行コードを生成する手順と、を含む。

(もっと読む)

情報処理システム

【課題】各タイマが別々に設けられると、消費電流が大きくなってしまうこと。

【解決手段】RTC2がタイマとして用いられる。虚時刻である「2000年1月11日0:00」がRTC2のレジスタに記憶される。具体的には、虚時刻である「2000年1月11日0:00」よりも後に到来する「2000年1月11日0:30」がRTC2のレジスタに記憶される。RTC2において、アラームのイネーブルビットが「1」に設定される。21日周期の割り込みがRTC2の定周期割り込みビットに設定される。

(もっと読む)

省電力とパフォーマンスを両立したストレージシステム及び記憶制御方法

【課題】ストレージシステムの稼動状態において省電力とパフォーマンスを両立する。

【解決手段】IOコマンドを送信する上位装置に接続されたストレージシステムが、複数の記憶デバイスを含み負荷となる複数の負荷デバイスと、前記複数の負荷デバイスに流れる電流値を測定する電流測定部と、前記測定された電流値を基に前記複数の負荷デバイスによって消費される消費電力値を各時点で算出する電力算出部と、前記上位装置からIOコマンドを受信し、前記複数の記憶デバイスのうち、そのIOコマンドに従う記憶デバイスにアクセスするコントローラ部とを備える。前記コントローラ部が、前記算出される消費電力値が所定の電力許容値以下となり且つ前記消費電力値と前記電力許容値との差分がなるべく小さくなる消費電力制御を実行する。

(もっと読む)

ジョブスケジューリング装置およびジョブスケジューリング方法

【課題】異なるマシンで構成されるシステムに対しても、パラメトリックジョブの最適なジョブスケジューリングを行う。

【解決手段】ジョブスケジューリング装置101は、N種のマシンM1,M2,・・・,MNのそれぞれに対し、パラメトリックジョブ群102のいずれか1つのパラメトリックジョブを試行実行させる試行実行部111と、N種のマシンM1,M2,・・・,MNの試行実行結果の情報を収集する情報収集部112と、N種のマシンM1,M2,・・・,MNの試行実行結果に基づいて、パラメトリックジョブ群102のスケジューリングを行うスケジュール処理部113とを有する。

(もっと読む)

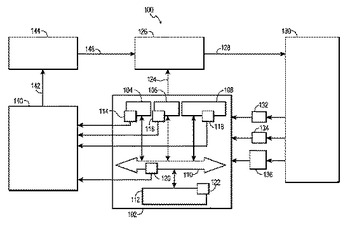

パフォーマンス解析に基づくシステムレベルの電力管理

データ依存アプリケーション実行用のダイナミックアダプティブ電力管理付きマルチプロセッサシステムオンチップ102は、タスクのランタイムパフォーマンス要求を収集するために戦略的に配置されたパフォーマンスカウンタを具える。パワーマネージャ130が、監視している種々のシステムリソースに、DVS132,DFS134,タイムアウト136及び他の制御を与える。タスクがランタイム中に実行するとき、タスクとスケジュールされたリソースとの間の適合品質が解析される。このとき、より正確な電力制御及びスケジュールが使用可能にされ、パフォーマンス要求テーブルに格納される。それゆえ、この電力管理はアダプティブでダイナミックである。スタティック解析フェーズ中に、それらのパフォーマンス要求を予め特徴化できるアプリケーション及びタスクをプロファイルし、ランタイム中の補正のための初期出発点としてプリロードする。  (もっと読む)

(もっと読む)

媒体論理チャネル上でデータが送信されていないときに節電を可能にする方法

【課題】媒体論理チャネル上でデータが送信されていないときに節電を可能にする方法

【解決手段】ネットワークを介して通信するよう構成された通信デバイスの中でスリープ期間を判定する方法及びシステムが提供される。この方法は、データ単位に関係する2つ以上のデータフィールドの内少なくとも1つを解析することと、解析に基づきデバイススリープ期間を判定することとを含む。解析は、オーバーヘッド情報シンボルチャネルの中で特定のMediaFLO論理チャネルデータ(MLC)があるか否かを判定することを含む。MLCデータが存在しない場合、デバイスは所定の時間にわたってスリープする。

(もっと読む)

電力的に効率的な命令プリフェッチ機構

【課題】電力的に効率的な命令プリフェッチメカニズム

【解決手段】

プロセッサは、重み付き分岐予測値を生成する条件付き分岐命令予測機構を含む。強い重み付き予測よりも正確さが低くなる傾向がある弱い重み付き予測に関しては、推測的にキャッシュを満たしてその後にフラッシュすることと関連する電力は、命令プリフェッチを停止させることによって節約される。命令フェッチは、分岐条件がパイプライン内において評価されさらに実際の次のアドレスが知られているときに継続する。代替として、キャッシュからのプリフェッチが継続することができる。適切なキャッシュデータが誤予測された分岐に基づいてプリフェッチされた命令に置き換えられるのを回避するため、キャッシュミスの場合は弱い重み付き予測に応じてプリフェッチを停止させることができる。

(もっと読む)

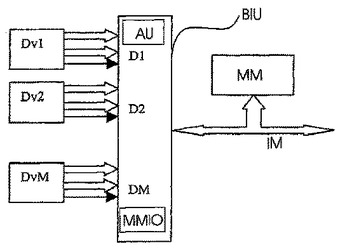

データ処理システム及びインターコネクト・アービトレーション方法

データを処理する複数の処理ユニット(Dv1〜DvM)と、複数の処理ユニット(Dv1〜DvM)からのデータを保存する少なくとも一つのメモリ手段(MM)と、複数の処理ユニット(Dv1〜DvM)と少なくとも一つのメモリ手段(MM)とを接続するインターコネクト手段(IM)とを備えたデータ処理システムが提供される。処理ユニット(Dv1〜DvM)は、少なくとも一つのメモリ手段(MM)にデータを書き込むためにインターコネクト手段(IM)を介して少なくとも一つのメモリ手段(MM)に書き込みアクセスを要求することに適応している。複数の処理ユニット(Dv1〜DvM)から少なくとも一つのメモリ手段(MM)へのアクセスのためにインターコネクト・アービトレーションを行う少なくとも一つのアービター手段(AU)が提供され、複数の処理ユニット(Dv1〜DvM)から少なくとも一つのメモリ手段(MM)への書き込みアクセスによりもたらされるインターコネクト手段の最低論理レベル変化に基づいてインターコネクト・アービトレーションが行われる。従って、異なる処理ユニットからの二つ以上の書き込み要求が受け付けられる場合、その処理ユニットに対して、インターコネクト・アービトレーション、即ち、インターコネクトへのアクセスが許可され、インターコネクトを介してメモリ手段へ送出されるデータがインターコネクト手段に対して最低論理レベル変化となる。それにより、論理レベルのスイッチングに起因する電力消費が低減される。  (もっと読む)

(もっと読む)

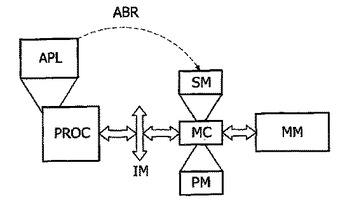

メモリアクセスを制御する方法及び集積回路

固有の通信パラメータを必要とするアプリケーション(APL)を処理する少なくとも1つの処理モジュール(PROC)と、データを格納する少なくとも1つのダイナミックランダムアクセスメモリ手段(MM)であって、該メモリ手段(MM)が複数の既定の動作モードにより動作可能であるメモリ手段とを有する集積回路が設けられる。更に、前記通信パラメータに基づいて前記複数の既定の動作モードの1つを選択する、少なくとも1つのメモリアクセス選択手段(SM)と、前記メモリアクセス選択手段(SM)により選択された前記既定の動作モードにしたがって前記少なくとも1つのダイナミックランダムアクセスメモリ手段(MM)のアクセスを制御する少なくとも1つのメモリ制御器(MC)とが、設けられる。前記メモリ制御器(MC)の各々はダイナミックランダムアクセスメモリ(MM)の1つに関連付けられる。相互接続手段(IM)は処理モジュール(PROC)及びメモリ制御器(MC)を結合し、その結果相互接続手段(MC)上の通信が達成される。  (もっと読む)

(もっと読む)

手持ち式携帯デバイスのための高質・高性能3Dグラフィックスアーキテクチャ

手持ち式携帯デバイスに適した高質および高性能の3Dグラフィックスアーキテクチャが提供されている。この3Dグラフィックスアーキテクチャは、サイズおよび他の特徴によって多角形を分類するためのモジュールを組み込んでいる。一般に、小さく且つ形が整った三角形は、質や性能を何ら犠牲にすることなく(例えば、リアリズム、分解能など)、電力効率がよい回路を有する 「低精度」ユニットを使用して処理することができる。プリミティブを分類し且つより電力効率がよい処理ユニットを選択してプリミティブを処理することにより、質や性能を犠牲にすることなく、電力消費量を低減することができる。 (もっと読む)

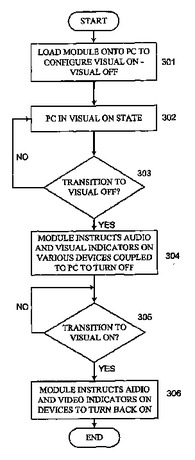

データ処理デバイスを動作させるための方法、装置、及びシステム

データ処理デバイスが外見的に「オフ」である間に動作することを可能にする方法、装置、及びシステム。一つの実施の形態によれば、データ処理デバイスは、新しいシステム状態、すなわち、視覚的オフを認識するように構成される。このようなデータ処理デバイスでは、電源ボタンが押下されると、デバイスをオフにする要求がモジュールによってインターセプトされ、デバイスは視覚的オフ状態へ遷移される。ユーザには、この遷移は瞬時のように見える。遷移中、データ処理デバイス及びデータ処理デバイスに接続されたヒューマン対話デバイス(「HIDデバイス」)の可聴インジケータ及び視覚インジケータをオフ及び/又は無効にすることができる。視覚的オフ状態の間、デバイスは完全に動作することができ、代替的な実施の形態では、デバイスを低電力状態にすることができる。ユーザが電源ボタンを再び押下して、データ処理デバイスを「ウェイクアップ」させると、デバイスは、視覚的オフから「オン」状態(「視覚的オン」)に遷移することができる。すなわち、データ処理デバイス及びそれに接続されたHIDデバイスのすべての可聴インジケータ及び視覚インジケータをオン及び/又は有効に戻すことができる。

(もっと読む)

(もっと読む)

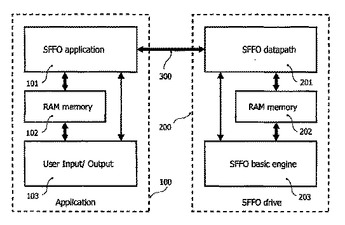

通信方法及びシステム

本発明は、低電力記憶装置のドライブブロックとアプリケーションブロックとの間の通信を行う方法に関する。本方法は、前記アプリケーションブロックに関するアプリケーションについての知識を前記ドライブブロックに与える特定のコマンドをインタフェースにより前記アプリケーションブロックから送信するステップと、前記コマンドに応答して、前記ドライブブロックにおける低電力処理を発行するステップとに対応する実行可能な命令から構成される。  (もっと読む)

(もっと読む)

81 - 97 / 97

[ Back to top ]