Fターム[5B011LL01]の内容

電源 (19,167) | 節電(オートパワーオフを除く) (3,178) | 漏れ電流の防止 (57)

Fターム[5B011LL01]に分類される特許

1 - 20 / 57

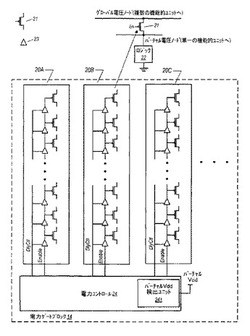

高速ウェイクアップのための電力スイッチ加速機構

【課題】ウェイクアップ中の電力スイッチ加速方法及び装置を提供する。

【解決手段】一実施形態において、集積回路は、少なくとも1つの電力ゲート回路ブロックを含む。電力ゲート回路ブロックは、該ブロックがアクティブであるときにその回路へ電圧を送るバーチャル電圧ノードを含む。バーチャル電圧ノードと、それに対応するグローバル電圧ノードとの間に電力スイッチが結合される。電力ゲート回路ブロックがパワーオンであるときに、電力スイッチが順次にアクチベートされる。電力スイッチがアクチベートされる割合は、バーチャル電圧ノードの電圧が増加するにつれて高くなる。電力スイッチを順次にアクチベートすることで、過剰な電流が電力ゲート回路ブロックに流入するのを防止する。バーチャル電圧ノードの電圧が少なくともあるレベルにあるときに電力スイッチがアクチベートされる割合を高めることで、より高速のウェイクアップを許すことができる。

(もっと読む)

電源制御装置、電源制御装置の制御方法、およびプログラム

【課題】多様な信号規格の処理に対応する半導体集積回路において、様々な周期性の違いに伴いタイミングと時間幅が変わるアイドル状態に対応した電源制御を適用し、消費電力を低減する。

【解決手段】処理状態と待機状態とを周期的に繰り返して処理を行う半導体集積回路の電源ドメインを制御する電源制御装置であって、待機状態の発生期間および発生間隔を含む周期的特徴情報を取得する周期情報取得部103と、電源ドメインが待機状態における待機電圧から半導体集積回路が動作可能となる電圧へ復帰するまでに要する復帰時間と対応付けられた待機電圧候補から、発生期間よりも復帰時間が短くなる待機電圧を電源制御情報として設定する電源制御情報設定部104と、電源制御情報に従って発生期間における電源ドメインの待機電圧を制御する電源制御部105とを備える。

(もっと読む)

電子機器及び電源制御プログラム並びに電源制御方法

【課題】非動作時における待機電力消費を確実に低減して節電を図る。

【解決手段】テープ印字装置1は、直流電源ユニット134から供給される電圧に基づき2次側に定電圧を出力可能に構成されるとともに、外部からの起動制御信号の入力により2次側に定電圧を出力している起動状態と2次側の出力を停止する停止状態とを切り替え可能なレギュレータ147と、1次側電源の初期投入時に供給された電圧に基づき起動制御信号を出力してレギュレータ147を起動状態とするとともに、外部からの解除信号の入力により起動制御信号の出力を停止可能なトリガー回路141と、レギュレータ147から供給される定電圧に基づき動作し、レギュレータ147に対する起動制御信号、及び、トリガー回路141に対する解除信号、を出力可能なCPU137とを有する。

(もっと読む)

回路及び回路の駆動方法

【課題】消費電力を低減する。

【解決手段】入力信号を元に論理演算処理を行い、論理演算処理の結果に応じて設定される電位を記憶データとして保持し、記憶データに応じた値の信号を出力信号として出力する機能を有する演算回路を具備し、演算回路は、論理演算処理を行う演算部と、記憶データの電位を、論理演算処理の結果に応じた電位に設定するか否かを制御する第1の電界効果トランジスタと、記憶データの電位を、基準電位に設定するか否かを制御する第2の電界効果トランジスタと、記憶データに応じた値の信号を出力信号として出力するか否かを制御する第3の電界効果トランジスタと、を備える。

(もっと読む)

データ処理装置

【課題】イベントに対応して待機状態から起動状態に移行するときの消費電力を低減することができるデータ処理装置を提供する。

【解決手段】周辺デバイス20はロジック電源部13の状態移行に関係なく処理データを出力することができるので、この出力完了に対応して迅速に起動状態から待機状態に復帰して無駄な電力の消費を低減することができる。

(もっと読む)

電力の島を使用した集積回路での電力の管理

【課題】集積回路において、消費電力を効率的に利用することを目的とする。

【解決手段】システム及び方法は、電力の島を使用して集積回路の電力を管理する。集積回路は、消費電力が電力の島のそれぞれで独立して制御される複数の電力の島を有する。電力マネージャは、電力の島のうち1つの目的の電力レベルを決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を実行する。

(もっと読む)

電源制御回路及び電源制御方法

【課題】細粒度パワーゲーティングにおいて、オーバーヘッドの?ない小さな改良によって,非常に理想的なエネルギー削減効果を達成する。

【解決手段】アイドルサイクルカウンタ0605は、入力を検知した場合にはアイドルサイクルレジスタ0603をリセットし、入力を検知しない場合にはアイドルサイクルカウンタに加算する。比較器0606は、アイドルサイクルレジスタに保持されたアイドルサイクルとBECレジスタ0602に保持されたBECとを比較して、比較結果に応じて電源遮断処理又は電源非遮断処理のトリガーとなるフラグである予測フラグを予測フラグレジスタ0604に書き込む。電源遮断器0607は、電源0610と論理回路ブロックの間に接続され、アイドル期間が始まったときに、予測フラグレジスタに保持されている予測フラグに応じて電源供給を制御する。

(もっと読む)

半導体装置の電源供給方法、半導体装置の制御方法、半導体装置及び半導体チップ

【課題】同一パッケージ内に複数の半導体チップが搭載された半導体装置において、一部の半導体チップに対する電源供給を、その内部回路を保護しつつ停止することができる、半導体装置の電源供給方法、半導体装置の制御方法、半導体装置及び半導体チップを提供すること。

【解決手段】本発明は、通常時に動作モードが入力側に設定される双方向端子21を有する半導体チップ1と、半導体チップ1と同一パッケージ内に搭載される半導体チップ2と、に電源を供給する。そして、双方向端子21の動作モードを入力側から出力側に切り替える。次いで、半導体チップ1から半導体チップ2にLow信号を出力する。続いて、半導体チップ2の電源供給を停止する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】スタンバイ時の保持データ量の変化に対応すること。

【解決手段】半導体集積回路は、ロジック回路logicと、複数のSRAMモジュール2、3を具備する。複数のSRAMモジュールは、ロジック回路と独立に電源制御が可能とされ、複数のSRAMモジュールの間で独立した電源制御が可能とされる。具体的には、各SRAMモジュールの電位制御回路の一方の端子arvssと他方の端子vssmはセルアレーcell_arrayとローカル電源線vssmに接続される。一方のSRAMモジュール2と他方のSRAMモジュール3とのローカル電源線vssmは、共有ローカル電源線vssm22によって共有されている。一方と他方のSRAMモジュール2、3の一方と他方の電源スイッチPWSW22、PWSW23とは、共有ローカル電源線vssm22に共通に接続される。

(もっと読む)

電圧制御回路および電圧制御方法

【課題】リーク電流を低減し一定電圧を長時間にわたって保持することのできる電圧制御回路を提供する。

【解決手段】

複数の容量と、前記各容量に対応して設けられ前記各容量を所定のノードに選択的に接続する第1のスイッチと、リセット信号に応じて前記ノードをリセットし、該リセット信号が供給されないときにバックバイアスがかけられるリセットトランジスタとを含む。これにより、リーク電流を最小にし、一定電圧を長時間保持することができる。

(もっと読む)

半導体集積回路、半導体集積回路の内部状態退避回復方法

【課題】内部状態を保持しつつ、リーク電流をより削減する半導体集積回路、半導体集積回路の内部状態退避回復方法を提供する。

【解決手段】半導体集積回路は、第3回路部(122)と第4回路部(124)とを備える第1回路部(120)と、第1回路部(120)に供給する第1電源(MPW)の投入切断を制御する第2回路部(110)とを具備する。第3回路部(122)は、第1電源(MPW)の切断により保持する情報が消去されるフリップフロップ群(140)に内部状態を格納する。第4回路部(124)は、第1電源(MPW)が切断される前の情報を退避し、第1電源(MPW)が再投入されたときに回復するリテンションフリップフロップ群(150)に内部状態を格納する。

(もっと読む)

ネットワーク中継装置、ネットワーク中継装置の電力制御方法、および、そのためのコンピュータプログラム

【課題】ネットワーク中継装置において、AC電源からの消費電力を低減しつつ、低消費電力を実現することのできる技術を提供する。

【解決手段】ネットワーク中継装置は、AC電力を受電する主電源部と、外部デバイスから供給されるPoE電力を受電する待機電源部と、中継処理部とを備える。待機電源部は、PoE受電部と、待機電力制御部とを備える。ネットワーク中継装置は、中継処理部へのAC電力およびPoE電力の供給が遮断されている停止状態と、PoE電力の供給により中継処理部が動作する待機状態と、AC電力の供給により中継処理部が動作する動作状態とを有する。待機電力制御部は、外部デバイスからの指示に応じて、主電源部およびPoE受電部に電源オン/オフを指示することによって、停止状態と、待機状態と、動作状態とを切り替える。

(もっと読む)

プロセッサ制御システム、方法、及びプログラム

【課題】本発明は、消費電力を低減しながらもプロセッサの処理能力の低下を防止可能なプロセッサ制御システムを提供する。

【解決手段】管理装置の管理側制御手段の一部11は、温度計測手段にて計測された温度が閾値をこえたら、プロセッサの動作周波数を下げる第1制御機能と、第1制御機能にて前記動作周波数を下げた状態において前記プロセッサの処理性能が低下したら、前記予備用プロセッサを含む前記予備セルを動的に追加する第2制御機能とを含む。

(もっと読む)

マイクロコンピュータ

【課題】暗電流を増加させることなくレジスタのリフレッシュを行うことが可能なマイクロコンピュータを提供する。

【解決手段】CPUの動作モードを、CPUが動作している通常動作モードと、CPUが停止しているスリープモードとの間で切り替える動作モード切換手段と、通常動作モードにて動作し、CPUを動作させるためのメインクロックを生成するメインクロック生成手段と、メインクロック生成手段とは別に設けられ、サブクロックを生成するサブクロック生成手段と、CPUの設定状態や動作状態を含むCPU状態情報を記憶する第一記憶手段と、リフレッシュ用のCPU状態情報を記憶するする第二記憶手段と、スリープモードにおいて、サブクロックに基づいて予め定められたタイミングでリフレッシュ信号を生成するリフレッシュ信号生成手段と、リフレッシュ信号に基づいて、第二記憶手段に記憶されたCPU状態情報を読み出して、第一記憶手段に書き込むデータリフレッシュ手段と、を備えることを特徴とする。

(もっと読む)

特定用途向け集積回路のための電力消費の調整

【解決手段】

例えばグラフィックス処理ユニットのような特定用途向け集積回路(ASIC)における電力消費を調整するためのシステム、方法、及びコンピュータプログラム製品が提供される。当該方法においては、ASIC内に含まれるコンピュータ可読情報からASICの漏れ電流の値が受け取られる。ASICの漏れ電流の値に基いて、ASICの1つ以上の動作パラメータ、例えばASICへの供給電圧、ASICのエンジン速度、及び/又はASICを冷却するために用いられるファンのファン速度が調節される。随意的には、1つ以上の動作パラメータは、ASIC上で実行されているアプリケーションの種類に基いても調節され得る。また、ASICへの供給電圧は、ASICの温度がスレッショルドを超えた場合に遮断されてよい(随意的に)。

(もっと読む)

演算処理装置、演算処理装置の電源制御方法

【課題】CPU等の構成部品である演算器に対して、分割して電源の制御を実施できるようにして一度に発生する電圧変動量を減少させることで、電圧変動が大きくなる問題を解決する。

【解決手段】電源制御シーケンサー302は、電源制御信号301が電源の切断を指示した場合には、各IC303、305に対して入力側の信号値の固定化を指示し、その後に、CNT4〜CNT1信号により、MSB側のBLOCK304から段階的に電源の切断を指示すると共に、対応するOC306に対して出力側の信号値の固定化を指示する。電源制御信号301が電源の投入を指示した場合には、電源制御シーケンサー302は、LSB側のBLOCK304から段階的に電源の投入を指示すると共に、対応するOC306に対して出力側の信号値の固定化の解除を指示し、その後に、CNT5信号により、各IC303、305に対して入力側の信号値の固定化の解除を指示する。

(もっと読む)

電力の島を使用した集積回路での電力の管理

【課題】 集積回路において、消費電力を効率的に利用することを目的とする。

【解決手段】 システム及び方法は、電力の島を使用して集積回路の電力を管理する。集積回路は、消費電力が電力の島のそれぞれで独立して制御される複数の電力の島を有する。電力マネージャは、電力の島のうち1つの目的の電力レベルを決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を決定する。電力マネージャは、電力の島のうち1つの消費電力レベルを目的の電力レベルに変更する動作を実行する。

(もっと読む)

半導体装置

【課題】リーク電流値が変動する場合に効果的に電流消費を削減できる半導体装置を提供する。

【解決手段】第1の電源線と第2の電源線との間にトランジスタで構成されるスイッチが配置され、第2の電源線と第3の電源線との間に半導体回路が配置されている半導体装置は、第2の電源線と第3の電源線と間の電位差を測定する電位検出器と、電位差が初期値から所定値になるまでの時間間隔を測定する遷移時間計測器と、遷移時間計測器により測定された時間間隔に応じた第1の値を記憶する記憶素子と、記憶素子に記憶された第1の値と半導体回路の電源遮断期間を指定する第2の値とを比較する比較器と、比較器の比較結果が示す第1の値と第2の値との大小関係に応じてスイッチを遮断する動作の実行/非実行を選択する制御回路を含む。

(もっと読む)

電子機器

【課題】波形品質の確保と消費電力の低減とを両立する電子機器を提供することを目的とする。

【解決手段】データ信号線11に終端抵抗7が接続された回路構成を有する電子機器1であって、データ処理手段2と、データ処理手段2の主記憶装置となる1つ以上のデータ記憶手段3と、データ処理手段2とデータ記憶手段3とを接続するデータ信号線11に終端抵抗7を介して終端電圧を印加する終端電圧生成手段6と、データ信号線11と終端抵抗7との間に接続される通電遮断手段8と、を有し、データ処理手段2はデータ記憶手段3の構成を検知し、その検知結果に基づいて、通電遮断手段8によりデータ信号線11と終端抵抗7との間を通電させて終端抵抗7を有効にし、又はデータ信号線11と終端抵抗7との間を遮断して終端抵抗7を無効にすることにより上記課題を解決する。

(もっと読む)

電子装置及び揮発性メモリの待機電圧制御方法

【課題】揮発性メモリを搭載する電子装置であって、揮発性メモリの待機時のリーク電力を削減することができるようにした電子装置を提供する。

【解決手段】揮発性メモリ1が待機時から通常動作時に復帰したときは、誤り検出/訂正部8は、揮発性メモリ1を対象として誤りを検出し、誤り検出結果を全体制御部9に送り、全体制御部9は誤り検出結果を保存する。揮発性メモリ1が通常動作時から待機時に移行したときは、全体制御部9は、保存する誤り検出結果から前回待機時に誤りが発生したか否かを判断し、電源電圧供給部4を制御し、前回待機時に揮発性メモリ1に誤りが発生したときは、揮発性メモリ1に前回待機時よりも所定電圧値だけ高い待機電圧VDD3を供給させ、前回待機時に揮発性メモリ1に誤りが発生しなかったときは、揮発性メモリ1に前回待機時よりも所定電圧値だけ低い待機電圧VDD3を供給させる。

(もっと読む)

1 - 20 / 57

[ Back to top ]