Fターム[5B013AA07]の内容

先行制御 (1,991) | 先行制御 (774) | 命令先取、命令バッファ (334) | ワード境界、アラインメント (8)

Fターム[5B013AA07]に分類される特許

1 - 8 / 8

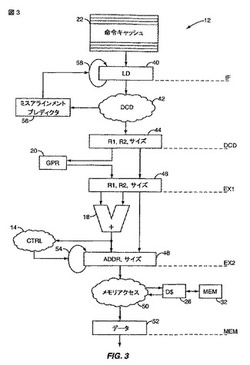

非アラインドメモリアクセス予測

【課題】命令実行パイプラインにおけるメモリアクセス命令のミスアライメントを早期に予測する。

【解決手段】複数のメモリアクセス命令のミスアラインメントを予測し、追加のマイクロ操作を実効アドレス生成に先立って生成する。該追加のマイクロ操作は、所定のアドレス境界を横切る範囲に入るメモリにアクセスする。追加のマイクロ操作を生成して追跡するのに十分なパイプライン制御資源が利用可能であることが保証され、実効アドレス生成時にそれら資源が利用可能でない場合のパイプラインフラッシュを回避する。ミスアラインメント予測は、フラッグ、二重モードカウンタ、局所プレディクタ、広域プレディクタおよび統合プレディクタなど、既知の条件付分岐予測技術を使用することができる。ミスアラインメントプレディクタは、メモリアクセス命令フラッグまたはミスアラインド命令タイプによって使用可能にされてもよいし、あるいはバイアスされてもよい。

(もっと読む)

命令制御装置、命令制御方法および演算回路

【課題】不要な命令プリフェッチ要求などの発生を抑止し、プロセッサの性能低下を防止することを課題とする。

【解決手段】開示する命令制御装置は、メインメモリに記憶されるデータのうち利用頻度の高いデータを記憶するL1キャッシュメモリから受信した命令フェッチデータを保存する命令バッファに空きがあるか否かを判定する。続いて、命令制御装置は、命令バッファに空きがあると判定された場合に、L1キャッシュメモリ内のMIBに少なくとも2エントリ以上の空きがあるか否かを判定する。そして、命令制御装置は、L1キャッシュメモリ内に少なくとも2エントリ以上の空きがあると判定された場合に、L1キャッシュラインのラインサイズに従ったアドレス境界で命令プリフェッチ要求をL1キャッシュメモリに出力する。

(もっと読む)

デジタル信号プロセッサ

【課題】性能および有用性を増進させるデジタル信号プロセッサを提供する。

【解決手段】可変長命令セットを利用するための通話を処理するデジタル信号回路において、DSPは3つのデータバスの組を含み、その上でデータはレジスタバンク120と3つのデータメモリ102,103,104と交換されることができる。レジスタバンク120は、少なくとも二つのプロセスユニット128,130によりアクセス可能なレジスタを有して使用され得る。命令フェッチユニット156は、命令メモリ152中に格納される可変長の命令を受信することを含むことができる。この命令メモリ152は3つのデータメモリ102,103,104の組から離されている。

(もっと読む)

マイクロプロセッサ及びマイクロプロセッサの制御方法

【課題】

ノンブロッキング・ロード機能を備えたマイクロプロセッサであっても、非整列ロード命令が発行された場合、若しくはキャッシュアクセスにおいてキャッシュミスがあると、パイプラインストールが発生する。

【解決手段】

ロード・ストア・ユニット22は、ロード先レジスタのロード前の値を格納するTopレジスタ103と、命令デコード部13より発行されたロード命令が、非整列ロード命令であるか否かを判定する非整列命令判定部104と、Topレジスタ103に保持されたデータを格納可能な退避レジスタ106とを備えており、非整列命令判定部104が非整列ロード命令と判定した場合に、Topレジスタ103の格納データを退避レジスタ106に格納し、Topレジスタ103を命令デコード部13が発行する後続命令に使用可能とする。

(もっと読む)

キャッシュライン境界を横切る命令におけるキャッシュミスの処理

プロセッサーのフェッチセクションは命令を取得するための命令キャッシュといくつかのステージのパイプラインを備える。命令は、キャッシュライン境界を横切ってもよい。パイプラインステージは2つのアドレスを処理し完全な境界を横切る命令を回復する。そのような処理の期間に、命令の第2の部分がキャッシュに存在しないなら、第1のラインに関するフェッチは無効とされ再循環される。この第1のパスに対して、そのデータのいずれかをプロセッサーの後段のステージに渡すことなく、命令の第2の部分のためのアドレスの処理は、より高いレベルのメモリからキャッシュに命令データをロードするためのプリフェッチ要求として取扱われる。第1のラインアドレスが再びフェッチステージを通過すると、第2のラインアドレスが通常の順番で続き、命令の両方の部分は、キャッシュからフェッチすることができ、通常の方法で結合することができる。  (もっと読む)

(もっと読む)

非整列メモリアクセス予測

命令実行パイプラインにおいて、メモリアクセスの不整合が予測される。該予測に基づいて、追加のマイクロ操作は該メモリアクセス命令の実効アドレス生成に先立って該パイプラインにおいて生成される。該追加のマイクロ操作は、所定のアドレス境界を横切る範囲に入る該メモリにアクセスする。該パイプラインにおける該不整合の予測および該マイクロ操作の早期生成により、追加のマイクロ操作を生成して追跡するために十分な数のパイプライン制御資源が利用可能であることが保証され、実効アドレス生成時にそれら資源が利用できない場合にパイプラインフラッシュが回避される。不整合予測は、フラッグ、二重モードカウンタ、局所的プレディクタ、大域的プレディクタおよび組合せられたプレディクタのような既知の条件付ブランチ予測技術を使用することができる。不整合プレディクタは、メモリアクセス命令フラッグまたは不整合命令タイプによって使用可能にされてもよいし、あるいはバイアスされてもよい。 (もっと読む)

コンピュータシステム

【課題】 依存性によるデータ・エラーの発生を回避し、複数の命令を平行処理的にアウト・オブ・オーダで実行可能にする。

【解決手段】 命令フェッチ・ユニットと、命令をアウト・オブ・オーダで実行するための実行ユニットとを含み、実行ユニットが、レジスタファイル(250)と、複数の機能ユニット(260,262)と、レジスタファイルから複数の機能ユニットへデータを転送する第1バス(254,225)と、複数の機能ユニットからレジスタファイルへデータを転送する第2バス(275,276)と、命令ウインドウ内の命令のすべてに関して、アウト・オブ・オーダでメモリシステムにロード要求を行い、命令ウインドウ内の命令のすべてに関してイン・オーダでストア要求を行うよう適応させたロードストア・ユニット(205)とを含むようにしたものである。

(もっと読む)

コンピュータシステム

【課題】依存性によるデータ・エラーの発生を回避し、複数の命令を平行処理的にアウト・オブ・オーダで実行可能にする。

【解決手段】 命令フェッチ・ユニットと、命令をアウト・オブ・オーダで実行するための実行ユニットとを含み、実行ユニットが、レジスタファイル(250)と、複数の機能ユニット(260,262)と、レジスタファイルから複数の機能ユニットへデータを転送する第1バス(254,225)と、複数の機能ユニットからレジスタファイルへデータを転送する第2バス(270,275,276)と、命令ウインドウ内の命令のすべてに関して、アウト・オブ・オーダでメモリシステムにロード要求を行い、命令ウインドウ内の命令のすべてに関してイン・オーダでストア要求を行うよう適応させたロードストア・ユニット(205)とを含むようにしたものである。

(もっと読む)

1 - 8 / 8

[ Back to top ]