Fターム[5B013EE00]の内容

先行制御 (1,991) | 誤動作対策 (103)

Fターム[5B013EE00]の下位に属するFターム

Fターム[5B013EE00]に分類される特許

1 - 5 / 5

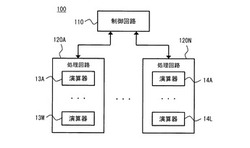

演算処理装置及び演算器同時実行制御方法

【課題】異なるプロセッサ間で同時に演算器が起動する電圧変動最悪パターンを改善すること。

【解決手段】本発明にかかる演算処理装置100は、同時に実行可能な複数の演算器を有する複数の処理回路120A〜120Nと、各処理回路で実行中の演算器の総数を集計する制御回路110と、を備え、複数の処理回路120A〜120Nのそれぞれは、制御回路110が集計した集計結果に応じて自己が有する演算器のうち未実行の演算器を実行するか否かを決定する。

(もっと読む)

演算処理装置及び演算処理方法

【課題】レジスタからの読み出しデータにおける誤り検出時に、プログラム実行動作を停止することなく、継続して実行可能である演算処理装置を提供する。

【解決手段】演算処理装置は、レジスタから読み出したデータのエラーを検出し訂正する訂正制御部と、命令の実行要求に応じてキャッシュ領域又はノンキャッシュ領域にアクセスするとともに、実行要求された一の命令がノンキャッシュ領域にアクセスするロード命令であることを通知するキャッシュ制御部と、一の命令がノンキャッシュ領域にアクセスするロード命令であることがキャッシュ制御部により通知されると、一の命令をキャッシュ制御部に実行させる間、他の命令の実行を待たせることにより、ノンキャッシュ領域にアクセスするロード命令の実行中にエラーが検出されないようにする命令実行制御部とを含む。

(もっと読む)

時間的に分離した冗長プロセッサの実行を使用しての周辺機器への読み書き

【課題】時間的に分離した冗長プロセッサの実行を使用して周辺機器への読み書きを高安全に提供する。

【解決手段】第1のプロセッサにより周辺機器からデータを読み取りレジスタにコピーし、時間的に分離した第2のプロセッサによる前記周辺機器からの読み取り試行を前記レジスタに迂回させレジスタから前記データを読み取ることにより、読み取りデータが同じであることが保証される。実施形態を、自動車、銀行金融、航空宇宙、防衛、インターネット決済等に関連する安全が関連する用途に利用することができる。

(もっと読む)

多重化実行に対してスケーラブルなパイプラインプロセッサシステム

【課題】パイプラインプロセッサシステムにおいて、多重化コストを削減する。

【解決手段】多重化実行が可能な複数のパイプラインプロセッサ1a〜1eと、前記複数のパイプラインプロセッサの多重化度を適応的に変更する制御部3と、を備えていることを特徴とする多重化実行に対してスケーラブルなパイプラインプロセッサシステム。

(もっと読む)

プロセッサを段階的減速動作モードに移行させる発行ユニット

【課題】プロセッサのライブロック状態の処理効率を向上する。

【解決手段】プロセッサを段階的に減速作動モードに移行させる発行ユニットを提供する。該減速作動モードは、プロセッサ内の発行ユニットに対する減速操作の複数のステージを含み、段階的スキームに従って命令の発行が減速される。このプロセッサの段階的減速によってライブロック状態からのプロセッサの解放を可能にする。さらに、減速が段階的に行われるので、プロセッサは、さまざまな程度のライブロック状態をフレキシブルに回避することができる。例示的実施形態のメカニズムは、軽度のライブロック状態は小さなパフォーマンスへの影響で処理し、もっと重度のライブロック状態の場合だけプロセッサのパフォーマンスへの影響を増加させることにより、ライブロック状態の厳しさに基いてプロセッサの全体的パフォーマンスに影響させる。

(もっと読む)

1 - 5 / 5

[ Back to top ]