Fターム[5B017CA02]の内容

Fターム[5B017CA02]に分類される特許

1 - 20 / 34

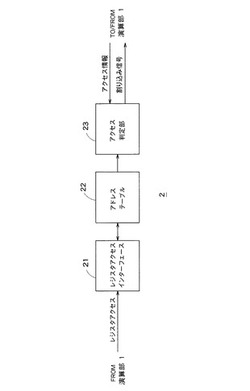

情報処理装置およびマルチコアシステム

【課題】アドレス空間を適切に保護することが可能な情報処理装置およびマルチコアシステムに関する。

【解決手段】実施形態によれば、情報処理装置は、演算部と、アドレス保護部とを備える。アドレス保護部は、前記演算部からアドレス保護情報を受信するレジスタアクセスインターフェースと、前記受信したアドレス保護情報を記憶するアドレステーブルと、前記アドレス保護情報に基づいて、前記演算部が指定したアドレスにアクセス可能か否かを判定し、アクセス不可である場合、割り込み信号を前記演算部に出力するアクセス判定部と、を有する。

(もっと読む)

プログラム実行装置及び情報保管装置及び情報処理方法及びコンピュータプログラム

【課題】OS状態情報が破壊された場合にもOSが復元されるようにする。

【解決手段】クライアント装置100は、OS状態情報をサーバ装置200に送信し、サーバ装置200にOS状態情報を保管させ、OS機能103の実行が再開される再開タイミングに先立ち、サーバ装置200に送信されたOS状態情報をサーバ装置200から受信し、再開タイミングに、サーバ装置200から受信されたOS状態情報を用いてOS機能103の状態を復元することができるため、OS状態情報が破壊された場合にも確実にOS機能103を復元することができる。

(もっと読む)

セキュア計算システム、セキュア計算方法およびセキュア計算用プログラム

【課題】マルチコアプロセッサを用いて計算処理を実行する際、プロセッサごとの動作を制御する特別なセキュリティ回路を備えていない場合であっても、セキュアに計算処理を実行できるセキュア計算システムを提供する。

【解決手段】一のコア80は、他のコア90からのアクセスが可能な状態で情報を記憶する他コアアクセス可能記憶手段81と、自コアからのみアクセスが可能な状態で情報を記憶する自コア内アクセス可能記憶手段82とを備える。復号手段83は、他のコアから受信した暗号化データを復号鍵を用いて復号した平文データを作成し、その平文データを平文データ記憶手段87に記憶させる。平文データ計算手段84は、平文データ記憶手段87に記憶された平文データに対して指定された計算処理を行い、その計算処理による計算結果を結果データ記憶手段86に記憶させる。

(もっと読む)

車載ネットワークシステム

【課題】各車載制御装置の処理負荷を抑えつつ車載ネットワークのセキュリティを向上させることのできる手法を提供する。

【解決手段】本発明に係る車載ネットワークシステムにおいて、車載制御装置が保持しているデータに対して読取要求または書込要求を発行する通信装置は、あらかじめ認証装置による認証許可を受ける。

(もっと読む)

ダイレクトメモリアクセス制御装置、ダイレクトメモリアクセス制御システム、プログラム、画像処理装置および複合機

【課題】、DMA実行中の転送元および転送領域へのメモリアクセスによる誤動作継続防止を目的とする。

【解決手段】同一のシステムバスを用いて、DMAおよびメモリアクセスの転送制御を行うDMAコントローラであって、DMAにおける転送元のアドレス範囲、およびDMAにおける転送先のアドレス範囲が格納される各レジスタ22〜25と、メモリアクセスにおけるデータ転送を行うためのアドレスが、システムバス上に指定されると、指定されたアドレスが、DMAの転送元のアドレス範囲内、もしくはDMAの転送先のアドレス範囲内のアドレスである場合、メモリアクセスにおけるデータは、不正アクセスである旨の不正アクセス警告信号を出力する不正アクセス検出回路1と、を有することを特徴とする。

(もっと読む)

安全性に関連したおよび安全性に関連していないソフトウェア・コンポーネントを1つのハードウェア・プラットフォーム上で実行する方法

本発明は、安全性に関連したおよび安全性に関連していないソフトウェア・コンポーネント(SAFET、STANT)を1つのハードウェア・プラットフォーム上で実行するための方法に関し、その際ハードウェア・プラットフォームは少なくとも1つの演算処理ユニット(CPU)および少なくとも1つのメモリ(SPE)を含み、その際少なくとも1つの安全性に関連していないソフトウェア・コンポーネント(STANT)が少なくとも1つの安全性に関連したソフトウェア・コンポーネント(SAFET)と共にこの1つの演算処理ユニット(CPU)上で実行され、その際ハードウェア・プラットフォームが監視コンポーネント(監視モジュール)(MOD)を備え、またはこれと接続されており、その際この監視コンポーネント(MOD)がハードウェア・プラットフォームの少なくとも1つの演算処理ユニット(CPU)とは無関係に働く。本発明によると、ハードウェア・プラットフォームはハードウェア・プラットフォームが書込み保護メカニズムを介して少なくとも1つのメモリ(SPE)の少なくとも1つの部分(SPE1、SPE2)を備えており、その際安全性に関連したソフトウェア・コンポーネント(SAFET)が全面的な書込みアクセスを特定の領域(SPE1〜SPE4)または全体のメモリ(SPE)に対して持っており、安全性に関連したソフトウェア・コンポーネント(SAFET)が安全性に関連していない機能のために備えられているメモリ領域から分離されているメモリの特定の領域上で、アクセス権を持ち、その際安全性に関連したソフトウェア・コンポーネント(SAFET)が安全性に関連していないソフトウェア・コンポーネント(STANT)の実行前に、安全性に関連していない機能(STANT)のアクセスに対して、安全性に関連した機能(SAFET)の少なくとも1つのメモリ領域(SPE1、SPE2)のメモリにメモリ保護を行い、その結果、安全性に関連していないソフトウェア・コンポーネント(STANT)は、メモリ(SPE)の制限された領域(SPE3、SPE4、SPE5)内でのみ書込みアクセス権を持ち、特に安全性に関連したコンポーネントのために切り離されたメモリ(SPE)の領域(SPE1、SPE2)へのアクセス権を持たず、その際安全性に関連していないコンポーネント(STANT)からの復帰後に、メモリ保護が再度停止され、その際、監視コンポーネント(MOD)が安全性関連機能をその決められたとおりの手順で監視する。 (もっと読む)

情報処理装置

【課題】悪意のある外部モジュールからのアクセスから重要なキャッシュデータを保護できるようにする。

【解決手段】オペレーティングシステムにキャッシュ機構を備えた情報処理装置であって、キャッシュバッファを前記オペレーティングシステムの管理外のメモリ領域から割り当てる割当手段を備え、オペレーティングシステムの管理外のメモリ領域の割り当てを、システムの起動引数を用いて通知する通知手段をさらに備えるようにして、悪意のある外部モジュールからのキャッシュデータを使った情報流出を防ぐことができるようにする。

(もっと読む)

データプロセッサ

【課題】データプロセッサにおいて、CPUからの転送条件の設定に従ったデータ転送制御に際し、信頼性の高い記憶保護を行う。

【解決手段】データプロセッサ(10)において、データの転送制御を行う転送制御装置(105)は中央処理装置(101)の転送制御を行うメモリ管理部(115)で記憶保護に利用される識別情報を保持する。前記転送制御装置は前記中央処理装置の設定にしたがって転送用のアドレスを生成するとき、転送用のアドレスに対応した識別情報と転送条件等設定時の中央処理装置の識別情報との一致を条件に転送開始を開始する。

(もっと読む)

データ処理制御方法、情報処理装置、及びデータ処理制御システム

【課題】2次記憶装置への書込み禁止により機密データの漏洩・紛失を防止し、機密データのサーバへの自動集約を図るシステムを提供する。

【解決手段】ファイルシステム203の下位に2次記憶装置書込み制御ドライバ108を配置し、2次記憶装置109への書込みに対して、メモリ110を1次キャッシュ、ネットワーク103先のキャッシュサーバ102上のキャッシュデータファイルを2次キャッシュとして書込みをリダイレクトする。これにより、2次記憶装置への書込みは行われず、差分データがキャッシュサーバ上に保存され、機密データのサーバへの自動集約が実現できる。

(もっと読む)

オペレーティングシステムとメモリ保護方法

【課題】CPU等の負担なしに効果的に必要な保護レベルの設定と、汎用性の向上とソフトウェア開発の効率化を提供する。

【解決手段】MMUを有するCPUに搭載可能にされるオペレーティングシステムである。第1物理アドレスに対応した第1論理アドレス空間を割り当てる第1TLBを作成して第1保護レベルとする。上記第1物理アドレスを含んでそれよりも大きな第2物理アドレスに対応した第2論理アドレス空間を割り当てる第2TLBを作成して第2保護レベルとする。タスクの生成時に、そのタスクに指定された保護レベルに対応したTLBに対応した論理アドレス空間をアクセスする。タスクの切り替え時に、切り替わったタスクの保護レベルに対応したTLBに切り替えて当該論理アドレス空間をアクセスする。実行中のタスクに指定された保護レベルに対応した論理アドレス空間に違反したメモリアクセスを検出してメモリアクセス違反処理を行う。

(もっと読む)

キャッシュメモリ制御装置及び方法

【課題】キャッシュラインへのアクセスを許可されていないプロセスに対して秘匿性を確保しつつ、キャッシュラインに記憶された情報を複数のプロセス間で共有することができるキャッシュメモリ制御装置を提供する。

【解決手段】キャッシュメモリ制御装置100は、キャッシュメモリ管理部1を備え、キャッシュメモリ処理部1が、データのキャッシュを行うキャッシュメモリのキャッシュラインごとに、キャッシュラインへの書き込みに応じて、1つ以上のプロセスに対して該キャッシュラインに記憶されているデータへのアクセスの可否を識別する所有者情報を対応付けて記憶し、実行中のプロセスがキャッシュラインにアクセスすると、キャッシュメモリ管理部に記憶されている所有者情報に基づいて、実行中のプロセスに対してアクセスを許可する。

(もっと読む)

画像を直接レンダリングしてセキュアなメモリ領域で対応するユーザ入力と相関付ける方法およびシステム

【課題】キーボード、ポインティングデバイス等を介して入力するデータをマルウエアに曝さないようにする。

【解決手段】アプリケーションおよびビデオフレームバッファを、保護されたメモリ領域に割り当て、ビデオフレームバッファのランダムな位置に画像をレンダリングして、ポインティングデバイスからのユーザ入力を、レンダリングされたキーボード画像へ相関付ける方法およびシステムを開示する。キーボード画像は、ユーザ入力に続いてランダムに再配置されてよく、セキュアなユーザ画像の上にレンダリングされてよい。承認画像は、保護されたメモリ領域から、ビデオフレームバッファのランダムな位置にレンダリングされてよく、承認画像に相関付けられていないユーザ入力に応じてランダムに再配置されてよい。

(もっと読む)

セキュリティを実現する装置、および方法

【課題】セキュアな実装を要するソフトウェアの開発者内部でも更にアクセス権を細分化する場合においても、そのキャッシュやプロセッサの汎用性を維持すること。

【解決手段】主記憶メモリ2上に確保されるセキュア領域21は開発者のデバッグ権限に応じて細分化された複数の領域211〜213が確保される。キャッシュではセキュアタグ1144として、開発者のデバッグ権限を示す「De」ビットを設け、集積回路1上のプログラムのデバッグをしている開発者の認証結果1511に応じた値を反映させる。この値に応じてデバッガからキャッシュへのアクセスを制限することで、細分化されたセキュア領域を判別する識別子をキャッシュのタグとして実装することが不要となる。

(もっと読む)

光学的情報読取装置

【課題】セキュリティ性を向上させ得る光学的情報読取装置を提供する。

【解決手段】各導通部51〜56および締結状態検知回路24により、筐体11に締結される各ねじ41〜46の締結状態を検出するとともに、主制御回路21により、検出される各ねじ41〜46の取り外し順序が判定用順序に一致するか否かについて判定される。この判定用順序は、ステップS101の処理により異なる順序に変更されるか、開封用情報コードが読み取られることに応じてステップS107の処理により開封用順序に変更される。そして、各ねじ41〜46の取り外し順序が判定用順序に一致しないとの判定、すなわち、筐体11の不正開封であるとの判定に応じて、メモリ23の読取情報が消去される。

(もっと読む)

プロセッサ、メモリ、コンピュータシステムおよび認証方法

【課題】低コストで、コンピュータへの不正アクセス等の不正行為を防止することのできるプロセッサを提供する。

【解決手段】演算手段と一体に形成され、第1メモリ認証用情報および第2メモリ認証用情報を保持するプロセッサ側メモリ認証用情報保持手段と、第1メモリから取得した第1メモリ認証用情報と、プロセッサ側メモリ認証用情報保持手段が保持する第1メモリ認証用情報とを比較して第1メモリを認証し、さらに第2メモリから取得した第2メモリ認証用情報と、プロセッサ側メモリ認証用情報保持手段が保持する第2メモリ認証用情報とを比較して第2メモリを認証するメモリ認証手段と、メモリ認証手段による認証結果に基づいて、第1メモリおよび第2メモリへのアクセスを制御するアクセス制御手段とを備えた。

(もっと読む)

セキュアなアプリケーション実行方法および装置

コンピュータシステム内のセキュアなアプリケーションおよびデータの整合性を実現する技術が提供される。一実施形態では、アプリケーションおよびデータを格納および実行可能な1以上のセキュアなエンクレーブを構築する。 (もっと読む)

ハードウェア・ベースの強制アクセス制御

【課題】 ハードウェア・ベースの強制アクセス制御の方法及び機構を提供する。

【解決手段】 ハードウェア・ベースの、データに対する命令のアクセス制御を行うためのハードウェア機構が提供される。これらのハードウェア機構は、プロセッサによって処理される命令に命令アクセス・ポリシー・ラベルを付随させ、プロセッサによって処理されるデータにオペランド・アクセス・ポリシー・ラベルを付随させる。命令アクセス・ポリシー・ラベルは命令と共に、プロセッサの1つ又は複数のハードウェア機能ユニットを介して伝えられる。オペランド・アクセス・ポリシー・ラベルはデータと共に、プロセッサの1つ又は複数のハードウェア機能ユニットを介して伝えられる。プロセッサの1つ又は複数のハードウェア機能ユニットに関連付けられた1つ又は複数のハードウェア実装ポリシー・エンジンが、命令アクセス・ポリシー・ラベル及びオペランド・アクセス・ポリシー・ラベルに基づいてデータへの命令によるアクセスを制御するのに用いられる。

(もっと読む)

情報処理装置

【課題】プロセッサからの不正なアドレスへのキャッシュアクセスを遮断する機構を、キャッシュアクセスにかかる時間に対するオーバーヘッドを少なく実現する。

【解決手段】本発明は、アクセスが許可されるアドレス範囲が異なる複数のアプリケーション群100、101からキャッシュメモリ120へのアクセスを制御し、不正アドレスへのアクセスを遮断するキャッシュメモリである。各アプリケーション群にそれぞれIDを付け、キャッシュメモリのタグフィールドを拡張し、キャッシュフィルを行う際にこのIDを記録しておく。ヒット判定の際に拡張タグフィールドとアクセス元のアプリケーション群のIDを比較することでアクセス制御を行う。

(もっと読む)

情報処理装置

【課題】

本発明は、集積回路装置内の未使用機能への不正アクセスの防止及び割り込み処理を行う最適な処理部へのルーティング制御が可能な情報処理装置を提供する。

【解決手段】

固有のメモリマップに従って割当られる複数の機能手段、各機能手段に対応し、該当する機能手段へのアクセス時の入力アドレスを各機能手段に共通のメモリマップのアドレスに変換する複数のインタフェース手段を有し、該インタフェース手段は、入力アドレスに対応する共通のメモリマップのアドレス及びそのアクセス可否を示す可否情報とを対応付けたアドレス変換情報を記憶し、該アドレス変換情報に基づき入力アドレスを共通のメモリマップのアドレスに変換するアドレス変換手段を具備し、該アドレス変換手段は、入力アドレスのアドレス変換時に、該アドレス変換の実施可否を判定し、該判定が実施否の時は、不正アクセスと判断して、その対応処理を行う不正アクセス処理手段を具備する。

(もっと読む)

シンクライアントシステム

【課題】 一時的にサーバとの通信が切断した場合でも操作の続行を可能にすると共に、通信による操作の待ち時間を発生しにくくする。

【解決手段】 クライアント端末としての携帯端末10とサーバ50とが通信網40を介して通信を行う。サーバ50は、少なくともセキュリティに配慮が必要なセキュアデータ702を記憶する記憶装置70を有する。携帯端末10は、データを一時的に記憶する一時記憶装置30と、一時記憶装置30内に設けられたキャッシュメモリ302と、キャシュメモリ302に対するデータの読込み・書込み処理とサーバ50に対するデータの読込み・書込み処理とを行う読込み・書込み手段202を含み、セキュアデータ301を扱うためのセキュアアプリ201を動作させて、読込み・書込み手段202によりサーバ50の記憶装置70に記憶されているセキュアデータ702を通信網40を介して読込んでキャッシュメモリ302に一旦保存する情報処理装置20とを有する。

(もっと読む)

1 - 20 / 34

[ Back to top ]