Fターム[5B017CA13]の内容

記憶装置の機密保護 (34,210) | 対象 (9,481) | 半導体記憶装置・素子 (381) | 1チップマイコン (58)

Fターム[5B017CA13]に分類される特許

1 - 20 / 58

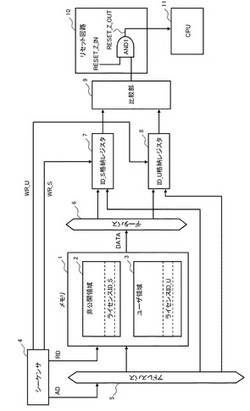

マイクロコンピュータ

【課題】ライセンス認証を正確に実施することが可能なマイクロコンピュータを提供することである。

【解決手段】本発明にかかるマイクロコンピュータは、メモリ1、ID_S格納レジスタ7、ID_U格納レジスタ8、比較部9、およびプロセッサ11を備える。メモリ1のユーザ領域3は、ユーザのアクセスが許可されている領域であり、ユーザプログラムおよびユーザ固有の識別情報であるライセンスID_Uが格納されている。メモリ1の非公開領域2は、ユーザのアクセスが禁止されている領域であり、ライセンスID_Uに対応するライセンスID_Sが格納されている。ID_S格納レジスタ7、ID_U格納レジスタ8にはそれぞれ、メモリ1に格納されているライセンスID_S、ID_Uが格納される。プロセッサ11は、比較部9においてライセンスID_SとライセンスID_Uとが同一であると判断された場合にユーザプログラムを実行する。

(もっと読む)

情報処理装置

【課題】 搭載するメモリ数を少なくしてコスト削減を図る。

【解決手段】 プログラム用フラッシュメモリ2は、特殊コマンドによってのみアクセス可能な特殊領域であるセキュリティエリアを備えた不揮発性メモリである。制御部1は、上記セキュリティエリアに対して機器固有情報を記憶する。上記機器固有情報としては、装置上で実行されるプログラム、ネットワーク通信をするときに使用するMACアドレス、制御基板に搭載している回路の補正値、プリンタコントローラに搭載しているヘッド駆動I/Fの補正値がある。さらに、セキュリティエリアに記憶した特性値に基いてプログラム用フラッシュメモリに読み書きを行う制御を行う。

(もっと読む)

情報処理装置、電子回路装置、データ消去方法

【課題】第三者のIC開封によるリバースエンジニアリングに対し高セキュリティを保ちつつ、必要に応じてユーザ自身が十分な解析できる電子回路装置が求められていた。

【解決手段】本発明の電子回路装置は、データを記憶する主記憶手段と、クロック周波数の変化を検出する第1検出手段と、検出された変化を計数する第1計数手段と、外部より設定される所定の値を記憶する第1記憶手段と、第1計数手段で計数された値と第1記憶手段に記憶されている値とに基づいて前記主記憶手段のデータを消去することを指示する消去信号を出力する出力手段と、を備える。本構成によれば、ICパッケージが開封される時に生じる変化をクロック周波数の変化から検出し、また、データ消去に関する基準値をユーザ自身が予め設定できるため、ユーザは使用用途に基づいてデータ消去タイミングの選択することが可能となる。

(もっと読む)

リーダライタ装置

【課題】RFIDタグのデータの不正な改竄を検出できるリーダライタ装置を得る。

【解決手段】RFIDタグ6は、固有ID部7にタグ固有情報を、記憶部8にHash値を記憶しており、リーダライタ装置1の制御部2は、送受信部3とアンテナ部4を介して、RFIDタグ6との間でデータの書込み、読取りを行うようになっており、データの書込み時には、RFIDタグ6からタグ固有情報を読取り、この読み取ったタグ固有情報と書込むべきデータを組み合わせてHash値を算出し、データをHash値とともにRFIDタグ6に書込み、データの読取り時には、RFIDタグからデータ及びHash値並びにタグ固有情報を読取り、この読み取ったタグ固有情報とデータを組み合わせてHash値を算出し、読み取ったHash値とを比較することにより、データの改竄を検出するようにしている。

(もっと読む)

電子機器

【課題】電子機器の耐タンパー性を確保する。

【解決手段】暗号処理装置110aは、金属ケース111内に電子回路基板112を収納して構成される。開封検知スイッチ113は、製造番号毎に異なった位置で、電子回路基板112に実装されている。ある製造番号の1台の特定の暗号処理装置110aの金属ケース111が破壊されて当該暗号処理装置110aの開封検知スイッチ113の位置が特定されたとしても、他の製造番号の暗号処理装置110aの開封検知スイッチ113の位置は特定できず、他の製造番号の暗号処理装置110aのセキュリティ及びタンパー性能を確保することができる。

(もっと読む)

誤書き込み防止回路および半導体装置

【課題】 書き込み時間の増加を抑制しつつ、保護対象のモジュールに対する誤書き込みを防止する。

【解決手段】 誤書き込み防止回路は、バスに出力されたアドレスおよびデータの少なくとも一方の一部の値を取得し、取得した値を用いて比較コードを生成する比較コード生成部と、バスに接続された保護対象のモジュールに書き込まれるデータに対応する期待値と比較コードとを比較する比較部と、比較部の比較結果に基づいて、モジュールに対する書き込みを許可するか否かを決定する書き込み制御部とを有している。

(もっと読む)

半導体装置

【課題】耐タンパ性を有する、可変論理機能を実現するための記憶回路を有する半導体装置を提供する。

【解決手段】制御回路24は、記憶回路23の次の読出しアドレスを先に記憶回路23から読出した制御フィールドの情報または外部イベント入力に基づいて自律的に制御することが可能である。正規デコーダ28は、制御回路24から出力されるアドレスをデコードし、デコード結果に基づいて、データフィールドの少なくとも1つの正規メモリセルと、制御フィールドの少なくとも1つのメモリセルを選択する。冗長制御回路51は、イネーブル信号が活性化された場合に限り、制御回路24から出力されるアドレスと、所定の正規メモリセルのアドレスとが一致したときに、正規デコーダ28による選択を禁止し、データフィールドの少なくとも1つの冗長メモリセルと制御フィールドの少なくとも1つの冗長メモリセルを選択する。

(もっと読む)

プロセッサ、バスインターフェース装置、およびコンピュータシステム

【課題】外部バスからプロセッサ内部のレジスタやローカルメモリの読み出しや改変が可能であった。そのため、暗号鍵などの機密データが読み出されたり、開発したソフトウェアがコピーされてしまう可能性があった。

【解決手段】外部と接続するバスを持つメディアプロセッサにおいて、外部バスに接続された他のデバイスからのアクセスは全て許可される。そのため、プロセッサ内部の機密事項を保護するために、メディアプロセッサのバスインターフェース部分にTLBを設け、そのTLBはプロセッサ内部からのみ書き換えることができる。このTLBは外部からアクセスされたアドレスが、アクセスできるかを判定する。TLB内にアクセス許可が記述されていればメディアプロセッサ内部へアクセスを発生し、そうでなければリクエストを破棄する。

(もっと読む)

メモリセルアレイを用いたIDチップおよびその生成方法

【課題】認証データ生成用の専用回路が不要で、SRAMのメモリセル構造をそのまま用いて、複製不可能な固有の識別情報を半導体メモリに予め搭載でき、セキュリティの向上を図れるIDチップおよびその生成方法を提供する。

【解決手段】本IDチップは、メモリセルアレイを構成する個々のメモリセルの閾値電圧のバラツキにより、メモリセルアレイに生成されたランダムなデータを固有の識別情報として用いた構成とされる。このメモリセルは、“0” または“1”の初期データが書き込まれた後に、両ビット線を同時に“Low”または“High”としてデータを生成する。そして、生成されたデータを用いて同一チップか否かを判別する。チップの判別は、メモリセルアレイのデータのハミング距離を測定し、ハミング距離が所定閾値以内の場合に同一チップと判別する。

(もっと読む)

マイクロプロセッサ

【課題】セキュリティビットをオンにしてフラッシュROMを書き換え禁止にする手法はフラッシュROMの再書き込みができず、解除キーが入力されたときに書き換えを許可する手法は、解除キー入力の専用端子が必要になり、端子数が増加する。本発明は端子数が増加せず、かつ再書き込みができるマイクロプロセッサを提供することを目的とする。

【解決手段】リセット信号がアクティブになったときに解除キーを入力する端子を入力端子に設定し、この端子に印加されるデータと解除キーを比較し、リセット信号がインアクティブに変化したときにこの比較結果を保存して、この保存した信号でデバッグ部の動作の許可、禁止を制御した。解除キー入力端子をユーザが使用する汎用端子と兼用できる。

(もっと読む)

半導体装置

【課題】簡易な構成で、対タンパ性を有する半導体装置を提供する。

【解決手段】ユーザ入力部13は、ユーザから認証コードの入力を受付ける。CPU3は、入力された認証コードに基づいて、ユーザのアクセスが正当か否かを判定し、正当な場合にイネーブル信号を活性化する。正規ロウデコーダ9は、CPU3によって指定されたロウアドレスをデコードし、デコード結果に基づいて、いずれかの正規メモリセルの行を選択する。冗長ロウデコーダ14は、イネーブル信号が活性化された場合には限り、指定されたロウアドレスと、所定の正規メモリセルのロウアドレスとが一致したときに、正規ロウデコーダ9による選択を禁止し、いずれかの冗長メモリセル行を選択する。

(もっと読む)

メモリのセキュア領域および非セキュア領域へのセキュアモードページテーブルデータの格納

シングルチップマイクロコンピュータ

【課題】ランダムアクセスによってリード・ライト可能な不揮発性記憶装置を、プログラム/データ兼用のメモリとして搭載した場合のセキュリティの向上を図るための技術を提供する。

【解決手段】予め設定されたプログラムに基づく演算処理を可能とするCPU(103)と、上記CPUによるランダムアクセスによってリード・ライト可能な不揮発性記憶装置(101)と、を含むシングルチップマイクロコンピュータ(100)である。上記不揮発性記憶装置は、記憶領域として上記プログラムが格納される不揮発保持領域とデータを格納可能な不揮発性保持無効化領域とを含む。リセット状態を示すリセット信号により、上記記憶領域のうち上記不揮発性保持無効化領域に対してライト動作を行うことで、上記不揮発性保持無効化領域のデータを消去する。

(もっと読む)

電子制御装置

【課題】EEPROM30内に記憶されたデータが誤って書き換えられるおそれがあること。

【解決手段】EEPROM30は、データの書き込みや消去に用いる電圧を生成する手段を備えず、代わりに、この高電圧が印加される高電圧端子HVTを備える。高電圧端子HVTは、テストポイントTPに接続されている。そして、製品出荷に先立ち、テストポイントTPに高電圧を印加しつつ、EEPROM30にデータを書き込んだ後、テストポイントTPへの電圧印加を停止する。これにより、高電圧端子HVTには、データの書き込みや消去のための高電圧が印加されない構成となる。

(もっと読む)

情報処理装置、プログラム、および情報処理システム

【課題】アプリケーションマネージャの仕様を変更することなく、アプリケーションによるセキュアチップへの不正なアクセスを防止することが可能な情報処理装置、プログラム、および情報処理システムを提供する。

【解決手段】ICチップにアクセスするためのアクセス権限情報を有するアプリケーションから、前記ICチップへのアクセス要求を受け付ける受付部と、前記受付部が受け付けた前記アクセス要求に含まれる前記アクセス権限情報に基づいて、前記アプリケーションの認証を行うための認証情報を外部サーバから取得する取得部と、前記取得部が取得した前記認証情報に基づいて、前記アプリケーションを認証する認証部と、前記認証部による認証結果に基づいて、前記アプリケーションによる前記ICチップへのアクセスを制御する制御部とを備える情報処理装置が提供される。

(もっと読む)

マイクロコンピュータ

【課題】汎用レジスタの使用効率を最適化することが可能なマイクロコンピュータを提供すること。

【解決手段】制御部13は、命令コードのデコード結果に応じて、命令の実行を制御する。GRAレジスタ32は、複数の汎用レジスタのそれぞれに対するアクセス属性を記憶する。モード記憶部31は、CPUの動作を制御するためのモードを記憶する。そして、レジスタアクセス許可判定回路33は、制御部13から汎用レジスタに対してアクセス要求がある場合に、GRAレジスタ32に記憶されるアクセス属性およびモード記憶部31に記憶されるモードに応じて、当該汎用レジスタに対するアクセスを許可するか否かを判定する。したがって、モードに対応して使用される汎用レジスタの本数を変更することができ、汎用レジスタの使用効率を最適化することが可能となる。

(もっと読む)

システムLSI

【課題】機密性の高い処理に用いる命令コードやデータを隠蔽することができるシステムLSIを実現する。

【解決手段】本発明のシステムLSIは、機密性の高い処理を行うプロセッサ21と、プロセッサ21が接続されるオンチップバス12と、プロセッサ21が処理した機密性の高いデータを記憶する作業メモリ22と、オンチップバス12と作業メモリ22の間に接続され、オンチップバス12と作業メモリ22とのデータ転送がプロセッサ21により制御されるメモリインターフェース回路23を有する。

(もっと読む)

ICチップ、データ読出し方法、データ読出しプログラム及び記録媒体等

【課題】効率よく、かつ迅速に記憶領域に記憶されたデータの正当性を確認することができるICチップ、データ読出し方法、データ読出しプログラム及び記録媒体等を提供する。

【解決手段】CPUは、EEPROM等に記憶された検証値12aを含むデータA12等が複数集合したデータ群11に対して、データ群11についての検証値11aを生成し、記憶する。そして、データ群11の何れかのデータが読み出される際に、データ群11についての検証値を新たに生成し、前記記憶されたデータ群検証値11aと比較することにより、データ群11の正当性について検証する。

(もっと読む)

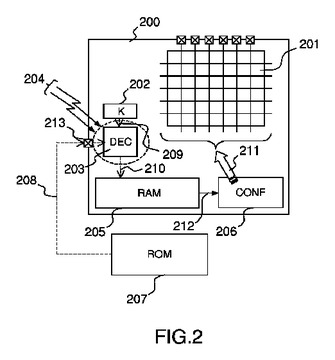

プログラマブル論理回路の設定ファイルの解読を保護する方法およびそれを実施する論理回路

本発明の主題はプログラマブル論理回路(100、200)を保護する方法であり、プログラマブル論理回路(100、200)のプログラマブル資源の構成に使用されるデータファイルは、暗号化された(112)後に不揮発性メモリ(107、207)に格納され、回路(103、203)内蔵の暗号解読モジュールはプログラマブル論理回路(100、200)に格納された秘密鍵(102、202)を使用することにより設定用データファイルを解読する役目を担い、暗号解読モジュールは、少なくとも1つの対抗技術を実施することにより暗号解読動作中に鍵を取得することを目標とする攻撃に対し保護されることを特徴とする。

本発明の別の主題は、特許請求範囲の請求項1〜4のいずれか一項に記載の方法を使用することにより暗号解読動作中の覗き見および/または故障利用攻撃に対し保護されるFPGAタイプのプログラマブル論理回路である。  (もっと読む)

(もっと読む)

電子制御装置

【課題】内部回路への不正アクセスを物理的に防止して、セキュリティを向上させることができる電子制御機器を提供すること。

【解決手段】プリンタに搭載した電子制御装置10に、内部回路11のパルス出力ポート16からHパルスを印加し、インターフェース12と接続部13に電圧を印加して内部回路11へのアクセスを禁止する電子回路15を結線部14に設ける。電子制御装置10は、例えば、プリンタ製造工程において、パルス出力ポート16からLパルスを出力し、接続部13に接続した外部装置が内部回路11へアクセスすることを許容する。一方、電子制御装置10は、プリンタ出荷後において、パルス出力ポート16からHパルスを出力し、接続部13に接続した外部装置が内部回路11へアクセスすることを禁止する。

(もっと読む)

1 - 20 / 58

[ Back to top ]