Fターム[5B018GA04]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | 誤動作防止、障害防止、データ消失防止 (1,341)

Fターム[5B018GA04]に分類される特許

1 - 20 / 1,341

メモリシステム及びそれのブロック複写方法

半導体記憶装置

メモリコントローラ

メモリアクセス制御装置および方法

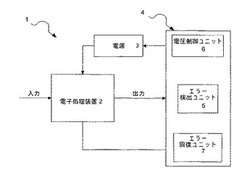

電圧制御

【課題】電子処理装置への電源電圧を最も効率の良い電力点で動作し、処理装置の出力の正確性を犠牲にすることなく、発生するエラーを修正することが可能な電圧制御方法を提供する。

【解決手段】プロセッサ又はメモリ要素を有する電子処理装置2への電源電圧を制御し電子処理装置の出力を受信する装置であって、当該装置は、電子処理装置の出力におけるエラーを検出するエラー検出手段5と、電子処理装置の出力において検出されたエラーの分析に基づいて、電子処理装置への電源電圧を適応的に変化させる手段6とを備える。装置は更に、電子処理装置の出力における検出されたエラーを修正する手段7を備える。

(もっと読む)

メモリモジュールおよび半導体記憶装置

【課題】電流の集中や発熱の集中を低減することができるメモリモジュールおよび半導体記憶装置の提供を図る。

【解決手段】複数のメモリチップ1A〜1Dが積層されたメモリモジュール10であって、前記各メモリチップは、複数のブロックに分割されたメモリセル部block0〜block3と、入力アドレス信号を処理して、動作させるブロックを選択するアドレススクランブル回路11A〜11Dと、を有する。

(もっと読む)

ウェアレベル制御ロジックを含むメモリシステム

【課題】不揮発性メモリのバッファ領域のウェアレベルを緩和するメモリシステムが提供される。

【解決手段】本発明によるメモリシステムは使用者領域とバッファ領域を有する不揮発性メモリと、前記不揮発性メモリのウェアレベル情報に基づいて、前記使用者領域の一部ブロックを前記バッファ領域に転換する動作を管理するためのウェアレベル制御ロジックと、を含む。前記ウェアレベル情報は前記使用者領域のプログラム−消去サイクル情報、ECCエラー率情報、又は消去ループ回数情報であり得る。本発明によると、バッファ領域のP/Eサイクル耐久性(endurance)を増加するか、或いはECCエラー率や消去ループ回数の増加率を減らすことによって、メモリシステムの性能を向上させ得る。

(もっと読む)

不揮発性キャッシュメモリ、不揮発性キャッシュメモリの処理方法、コンピュータシステム

【課題】不揮発性メモリをキャッシュメモリとして使用する場合に、電力遮断状態での保持されているデータの信頼性を向上させる。

【解決手段】キャッシュデータの記憶に不揮発性メモリを用いる。この場合に、電力供給遮断の準備として、待機状態データを生成して不揮発性メモリ部上に記憶する待機準備処理を行う。また電力供給再開の際に、待機状態データを用いて不揮発性メモリ部に記憶されたキャッシュデータの復帰処理を行う。

(もっと読む)

不揮発性メモリの正常性情報を取得して使用するためのシステム及び方法

【課題】不揮発性メモリ(「NVM」)の正常性情報を取得して使用するためのシステム及び方法を提供する。

【解決手段】正常性情報は、NVMの一部で検出されたエラー数、又は不揮発性メモリの一部から読み取りを行うために又はこのメモリの一部をプログラムするために必要な時間量などの、NVM装置の一部の性能及び信頼性に関連する様々な情報を含むことができる。動作中、ホスト装置上にアドレス固有の正常性情報を受動的に記憶し、コマンドの一部としてメモリコントローラに提供することができる。メモリコントローラは、このコマンドから正常性情報を抽出し、この情報を使用してアクセス要求を実行することができる。アクセス要求の完了後、メモリコントローラは正常性情報を更新し、この情報をホスト装置へ返送することができる。

(もっと読む)

ICチップ、ICチップにおける処理方法、ICチップ用処理プログラム、及びICカード等

【課題】適切な保護機能によってデータを保護することにより、データの保護機能による処理時間の短縮を図るICチップ、ICチップにおける処理方法、ICチップ用処理プログラム、及びICカード等を提供する。

【解決手段】CPU6は、「カードOSによる非更新領域の保護機能」と、「トランザクションによる更新領域の保護機能」とを備え、「トランザクションによる更新領域の保護機能」は、更新前の更新領域が属するページの全ての領域を更新領域として、当該ページに記憶される全てのデータを前記バックアップ領域に書き込み、当該ページに非更新領域が存在しないものとしてカードOSに通知して、「カードOSによる非更新領域の保護機能」を機能させない。

(もっと読む)

メモリー管理方法およびフィスカルプリンター

【課題】 信頼性を確保しつつ、冗長性の確保のためのコストを低減する。

【解決手段】 複数のメモリーに対してそれぞれ同一のフィスカル情報を順次書き込み、フィスカル情報の記録量が所定値に達した場合、複数のメモリーのうちの一つに記録された情報を消去し、情報を消去した前記メモリーのうちの一つに対してフィスカル情報の書き込みを続行する。

(もっと読む)

計算機及びデータ退避方法

【課題】低コストに且つ安全にシステムを停止できる計算機を提供する。

【解決手段】データを記憶する不揮発メモリと、不揮発メモリへのデータの退避を制御する制御プロセッサと、外部電源の障害時に当該計算機に電力を供給するバッテリと、を備えた計算機であって、制御プロセッサは、バッテリに蓄えられた充電量を確認し、確認された充電量に基づいて、外部電源の障害時にバッテリによって不揮発メモリに退避可能なデータ量を算出し、不揮発メモリに退避すべきデータのうち、退避可能なデータ量を除いたデータ量のデータを、予め不揮発メモリに退避する。

(もっと読む)

回路装置、回路装置のデータ保護方法及びフィスカルプリンター

【課題】複数の回路ブロック毎にバックアップ用バッテリーを配置した回路装置において、バックアップから正しく復帰できるようにする。

【解決手段】分割された回路ブロックを複数備えた回路装置であって、前記各回路ブロックには、各回路ブロックに個別のバックアップ用バッテリーと、前記バックアップ用バッテリーの電圧が予め設定されたバックアップ下限電圧まで低下したことを検出する電圧監視手段と、いずれかの回路ブロックの前記電圧監視手段における電圧低下検出時に、他の全ての回路ブロックについても前記電圧監視手段が電圧低下を検出した時と同じ状態に移行させる電圧低下連携手段と、前記回路ブロックに含まれる揮発性メモリーに蓄積されたデータを不揮発性メモリーに退避させるデータ退避手段とを備え、前記いずれかの回路ブロックの前記電圧監視手段の電圧低下の検出時に、前記データ退避手段が作動する。

(もっと読む)

電子制御装置

【課題】メモリ使用量を抑えることができる高信頼なメモリを備えた電子制御装置を提供する。

【解決手段】本発明に係る電子制御装置は、データ誤りを検出した第1記憶領域とは異なる第2記憶領域に、誤り訂正後のデータを保存し、第2記憶領域上のデータを制御処理のために用いるとともに、第1記憶領域上のデータも制御処理のために継続して用いる。

(もっと読む)

メモリの寿命を縮める動作を遅延させるシステム、方法、及びコンピュータプログラム製品

【課題】メモリの寿命を縮める動作を遅延させるシステム、方法、及びコンピュータプログラム製品を提供する。

【解決手段】メモリの寿命を縮める動作を遅延させるシステム500は、複数のストレージデバイス530、540を含むストレージシステム503が含まれている。コマンドの少なくとも一部は、寿命を縮めるコマンドであり、少なくとも一つのモジュール又はブロック531、532、533、541、542、543への悪影響を有する。使用中に、装置510は、そのような寿命を縮めるコマンドに拠らず、ストレージデバイス530、540の寿命を延ばすように働く。使用時に、メモリの寿命に関連する少なくとも一つの特徴が、特定される。このために、メモリの寿命を縮める少なくとも一つの動作が、当該特徴に基づいて遅延される。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体メモリの情報書き換え方法

【課題】不揮発性半導体メモリの書き換え時に、適切なパルス電圧および適切なパルス幅を備える信号を印加可能な不揮発性半導体記憶装置を提供することである。

【解決手段】本発明にかかる不揮発性半導体記憶装置は、記録されている情報を所定のパルス電圧および所定のパルス幅を備える信号を印加することで書き換え可能な不揮発性半導体メモリ11と、不揮発性半導体メモリ11の書き換えを制御する書き換え制御部12と、を備える。書き換え制御部12は、不揮発性半導体メモリの総書き換え回数に基づき仮のパルス電圧および仮のパルス幅の少なくとも一つを決定する。更に、決定された仮のパルス電圧および仮のパルス幅の少なくとも一つを不揮発性半導体メモリ11の温度に基づいて補正することで、書き換え時に不揮発性半導体メモリ11に印加する信号のパルス電圧およびパルス幅の少なくとも一つを決定する。

(もっと読む)

電子機器

【課題】

内蔵SRAM及び外部SRAMにそれぞれ別の設定情報を保存する場合でバックアップ電源が不足したときの異常動作を低減する。

【解決手段】

バックアップ電池(107)は、内蔵SRAM(103)及び外部SRAM(104〜106)にデータ保持のための電圧を供給する。内蔵SRAM(103)及び外部SRAM(104〜106)は一方から他方に又は相互に依存する設定情報を記憶する。システムコントローラ(102)は内蔵SRAM(103)の保持データに不正を検出すると、内蔵SRAM(103)の設定情報を消去し、内蔵SRAM103)の設定情報に依存する設定情報を記憶する外部SRAM(104〜106)の設定情報も消去する。

(もっと読む)

プログラム、情報処理システム、情報処理装置、および情報処理方法

【課題】他のデータに対するアクセスにより生じるエラーから特定のデータを保護できるプログラム、情報処理システム、情報処理装置、および情報処理方法を提供する。

【解決手段】例示的な実施の形態は、コンピュータで実行される、1つのメモリセルに複数ビットを記憶可能な半導体記憶手段に対してデータを書き込むためのプログラムを提供する。プログラムは、コンピュータに、第1のデータを記憶するための第1の領域を半導体記憶手段の記憶領域内に割り当てる割当ステップと、第1のデータの書込要求に応答して、第1の領域の境界から所定のサイズを保護領域とし、残りの領域を使用領域として、第1のデータを使用領域のみに書き込む書込ステップとを実行させる。

(もっと読む)

コントローラおよびメモリシステム

【課題】データの消失を効率よく予防すること。

【解決手段】本発明の一つの実施形態によれば、コントローラは、読み出し検査実行部と、検査ブロック設定部と、タイミング決定部とを備えている。読み出し検査実行部は、不揮発性メモリが備える複数のブロックのうちの有効データが格納されているブロックの読み出し検査を実行する。検査ブロック設定部は、不揮発性メモリが備える複数のブロックのうちから少なくとも1つに出来るだけ高い閾値を有する検査パターンデータを書き込んで検査ブロックを設定する。ここで、タイミング決定部は、検査ブロックに書き込まれた検査パターンデータに発生するビット反転数に基づいて読み出し検査実行部による読み出し検査のタイミングを決定する。

(もっと読む)

メモリコントローラ

【課題】半導体メモリを効率的に利用可能なメモリコントローラを提供すること。

【解決手段】実施形態のメモリコントローラ20は、第1インターフェイス21と、第2インターフェイス23と、制御部24とを備える。第1インターフェイス21は、ホスト10との間で信号を送受信する。第2インターフェイス23は、不揮発性の半導体メモリ30との間で信号を送受信する。制御部24は、第1インターフェイス21で受信した第1コマンドに応答して半導体メモリ30に予備領域を確保し、半導体メモリ30に保持されるデータの更新時には予備領域に更新データを書き込む。予備領域のサイズは、第1コマンドに応じて可変である。

(もっと読む)

1 - 20 / 1,341

[ Back to top ]