Fターム[5B018HA03]の内容

記憶装置の信頼性向上技術 (13,264) | 手段 (2,627) | 多重化 (456) | 記憶内容の多重化 (181)

Fターム[5B018HA03]に分類される特許

1 - 20 / 181

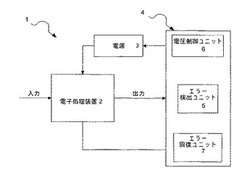

電圧制御

【課題】電子処理装置への電源電圧を最も効率の良い電力点で動作し、処理装置の出力の正確性を犠牲にすることなく、発生するエラーを修正することが可能な電圧制御方法を提供する。

【解決手段】プロセッサ又はメモリ要素を有する電子処理装置2への電源電圧を制御し電子処理装置の出力を受信する装置であって、当該装置は、電子処理装置の出力におけるエラーを検出するエラー検出手段5と、電子処理装置の出力において検出されたエラーの分析に基づいて、電子処理装置への電源電圧を適応的に変化させる手段6とを備える。装置は更に、電子処理装置の出力における検出されたエラーを修正する手段7を備える。

(もっと読む)

電子制御装置

【課題】メモリ使用量を抑えることができる高信頼なメモリを備えた電子制御装置を提供する。

【解決手段】本発明に係る電子制御装置は、データ誤りを検出した第1記憶領域とは異なる第2記憶領域に、誤り訂正後のデータを保存し、第2記憶領域上のデータを制御処理のために用いるとともに、第1記憶領域上のデータも制御処理のために継続して用いる。

(もっと読む)

メモリシステムとその制御方法

【課題】 データを確実且つ高速に書き込むことが可能なメモリシステムとその制御方法を提供する。

【解決手段】 メモリシステムは、第1、第2のディストリクト31a、31bと、制御部21を含んでいる。第1、第2のディストリクト31a、31bは、それぞれメモリセルアレイ32を有する。制御部21は、第1、第2のディストリクト31a、31bへ同時に第1のデータを書き込むための書き込みコマンド及びアドレスを受け、第1、第2のディストリクト31a、31bに同時に第1のデータを書き込む。

(もっと読む)

ICチップ、ICチップにおける処理方法、及びICチップ用処理プログラム

【課題】処理中断によりトランザクションが行われた場合であっても、処理時間制約が厳しい方のインターフェイスを用いた処理を正常に行うことが可能なICチップ、ICチップにおける処理方法、及びICチップ用処理プログラムを提供する。

【解決手段】ICチップは複数のインターフェイスに対応した処理手段と、データを記憶するデータ記憶領域と前記データをバックアップするためのバックアップ領域と、を有する不揮発性メモリと、第1の前記インターフェイスを用いた処理により受信されたデータを前記データ記憶領域に書き込む際に前記データ記憶領域に記憶されているデータを前記バックアップ領域にバックアップし、前記第1の前記インターフェイスを用いた処理が中断された場合には、前記バックアップ領域にバックアップされている前記データを前記記憶領域に書き戻す処理を行う制御手段と、を備える。

(もっと読む)

情報更生装置、メモリ制御システム、情報更生方法およびコンピュータプログラム

【課題】 記憶容量が不足する事態を抑制しながら、メモリにおける情報保持性能の信頼性を高める。

【解決手段】 更生部2を備える。当該更生部2は、メモリから読み出された情報に含まれるビット誤りの数を誤りビット数として前記メモリにおける予め定められたメモリ領域毎に計数する機能を備えている。また、更生部2は、その誤りビット数が予め定められた閾値以上である前記メモリ領域には、当該メモリ領域とは別のメモリ領域に事前に書き込まれていたバックアップ情報を上書きする機能を備えている。

(もっと読む)

メモリコントローラ及び不揮発性記憶装置

【課題】不揮発性メモリにおいて第1の誤り訂正符号の訂正能力を超えるエラーが発生した場合でも、格納したデータを正しく読み出すことが可能で、かつ、小さいサイズの書き込みが効率的な不揮発性記憶装置、及びメモリコントローラを提供する。

【解決手段】不揮発性記憶装置は、データを記憶する不揮発性メモリと、不揮発性メモリの制御を行うメモリコントローラとを備え、メモリコントローラは、データと同一ページに格納する第1の誤り訂正符号とは別に、第2の誤り訂正符号をも格納する。所定のサイズよりも小さい書き込みにおいては、前記第2の誤り訂正符号を付与せず、データと同一ページに格納する第1の誤り訂正符号を、異なるページに二重化して格納する。データの読み出し時にはデータに付与された第1及び/または第2の誤り訂正符号を用いてエラー訂正を行う。同一論理アドレスに対して、いずれの論理ブロックに有効なデータが格納されているかを管理するための有効データ管理テーブルを備えている

(もっと読む)

携帯可能電子装置、ICカード、及び携帯可能電子装置の制御方法

【課題】 より安定して動作する携帯可能電子装置、ICカード、及び携帯可能電子装置の制御方法を提供する。

【解決手段】 一実施形態に係る携帯可能電子装置は、データを記憶する第1のメモリと、復元アドレスと復元データとを対応付けてメモリ保障データとして記憶する第2のメモリと、外部機器から送信された書込みコマンドを受信する受信部と、前記書込みコマンドからアドレス及び書込みデータを取得し、前記アドレスと、前記書込みデータのデータサイズと、に基づいて前記第1のメモリ上の領域を特定し、特定された前記領域のデータを復元データとして前記第2のメモリに記憶し、前記アドレスを復元アドレスとして前記第2のメモリに記憶する制御部と、特定された前記第1のメモリ上の領域に前記書込みデータを書込む書込み処理部と、を具備する。

(もっと読む)

コンピュータ、その制御方法及びプログラム

【課題】MBRとバックアップセクタデータを検証し、正常にリードできない又は不正であるときに、自動的に復旧し起動処理を実行する。

【解決手段】シャットダウンを検知した場合に、MBRとバックアップMBRのリードを行い、MBRのデータとバックアップMBRのデータとが同一でないときにMBRをバックアップMBRにコピーするか、バックアップMBRが正常にリードできない又は不正であるときにMBRをバックアップMBRにコピーするかする。コンピュータの電源をオンした場合に、バックアップMBRが正常にリードできない又は不正であるときにMBRをバックアップMBRにコピーする。

(もっと読む)

半導体装置

【課題】データの信頼性の向上を低コストで実現可能な半導体装置を提供する。

【解決手段】例えば、相補メモリを備えた半導体装置において、書き込み時に、(N+1)ビットの正極(Posi)データに対してパリティービットを生成し、(N+1)ビットの負極(Nega)データに対してパリティービットを生成する。読み出し時には、正極側および負極側のそれぞれに対してパリティーチェックを行うと共に、正極データと負極データを各ビット番号毎に比較する。ここで、正極データと負極データが同一データとなっているビット番号が存在した場合、正極側のパリティーチェック結果が異常であれば正極データの当該ビット番号を誤データとして特定でき、逆に負極側のパリティーチェック結果が異常であれば負極データの当該ビット番号を誤データとして特定できる。

(もっと読む)

記録媒体、光伝送モジュール、データ保存方法及びメモリ管理装置

【課題】不揮発メモリへ書き込み中に電源等が断たれた場合であっても、より最新のデータ情報を利用可能な記録媒体を提供する。

【解決手段】データ保存方法は、書込み要求されたデータと揮発性ユーザデータ領域のアドレスのデータとを比較し、データの変更があるか否かを判定するデータ変更判定ステップ(S11)と、データ変更判定ステップにおいて肯定的な判定の場合に、揮発性ユーザデータ領域の対応するアドレスに書込みを行う揮発性領域書込みステップ(S12)と、パリティビットを生成し、変更の内容を第1不揮発性バッファ領域にデータ毎に保存すると共に、保存先を示すアドレスを逐次変更する第1変更内容保存ステップ(S13,S14)と、第1不揮発性バッファ領域へ保存量が所定量に達した場合に、揮発性ユーザデータ領域のデータを第2不揮発性ユーザデータ領域にデータ毎に複製保存する第1複製保存ステップ(S16)と、を備える。

(もっと読む)

RAM値保証装置およびRAM値保証プログラム

【課題】RAMの記憶容量を抑制しながらRAMの記憶値を保証できるようにしたRAM値保証装置およびRAM値保証プログラムを提供する。

【解決手段】CPUは、OSによりプログラムカウンタ6の示すアドレスを監視し、非保証プログラム領域9から保証プログラム領域10にプログラムカウンタ6のアドレスが遷移することを確認すると、保証RAM領域12のデータとバックアップRAM領域13のデータとを比較し、当該データが異なっているときには保証RAM領域12のデータをバックアップRAM領域13のデータで更新する。CPU8はOSによりプログラムカウンタ6の示すアドレスを監視し、更新許可領域10aから更新許可領域10bにプログラムカウンタ6のアドレスが遷移することを確認すると、その遷移直前にRAM_A群バックアップ13aの更新を許可し、RAM_A群バックアップ13aのデータをRAM_A群12aのデータで更新し、更新処理後にRAM_A群バックアップ13aの更新を禁止する。

(もっと読む)

制御装置、記憶装置、制御方法

【課題】不揮発性メモリのデータ信頼性向上と読出アクセス時間の高速化及び安定化

【解決手段】不揮発性メモリに記憶されたデータについて、近い将来リフレッシュが必要となるか否か、つまりリフレッシュ機会が近接しているか否かを推測する。この推測にはアクセス時のビットエラー数などを記憶した評価用情報を用いる。そしてリフレッシュ機会が近接していると判定されるデータについて、そのデータをオリジナルデータとして、オリジナルデータと同一のクローンデータを、不揮発性メモリ内に生成する。その場合、アクセス実行の際にオリジナルデータとクローンデータのいずれか一方がアクセス対象となるように、管理情報を更新する。

(もっと読む)

エラー訂正装置、エラー訂正方法及びエラー訂正プログラム

【課題】半導体メモリに記憶したデータにソフトエラーが発生した場合に、ソフトエラーを修正して正しいデータを得ることを目的とする。

【解決手段】補正データ格納用メモリ9には、少なくとも格納時点においては同一のデータであった補正データであって、複数のビットからなる補正データが、3つ以上の奇数個の領域に格納されている。多数決処理部12は、補正データ格納用メモリ9の各領域に格納された補正データの間で各ビットの値について多数決をとり、多数決データを生成するとともに、各領域に格納された補正データの間で値が異なるビットを示す差異データを生成する。妥当データ復元処理部15は、多数決データが妥当条件を満たす妥当データになるように、差異データが示すビットの値を変更して妥当データを生成する。

(もっと読む)

メモリデバイスにおける読み出し不可状態を解決するための装置及び方法

【課題】ブートエラーを正すための装置及び方法を提供する。

【解決手段】装置100は、不揮発性のメモリデバイス120を有し、そのメモリデバイス120は、第1のアドレスを持つ所定のブロックに、ブートローダーを格納している。装置100は、さらに、電源投入時に、所定のブロックからブートローダーを読み出すメインコントローラー110を有している。装置100は、また、メインコントローラー110の最初のブートシーケンスを監視するとともに、所定のブロックが、読み出し不可エラー状態に陥ったことを判定するように構成された監視モジュール130を含んでいる。監視モジュール130が、所定ブロックは読み出し不可エラー状態に陥ったと判定したとき、メインコントローラー110は、バックアップブロックからバックアップブートローダーを取得する。

(もっと読む)

情報処理装置、メモリ管理方法、およびメモリ管理プログラム

【課題】記憶領域の冗長化およびシステムの安定化の両立を図ることが可能な情報処理装置、メモリ管理方法、およびメモリ管理プログラムを提供する。

【解決手段】情報処理装置201は、データを記憶するための記憶装置103を用いる。情報処理装置201は、記憶装置103よりも高速にアクセス可能なメモリ102と、メモリ102において複数の記憶領域を論理的に設け、記憶領域に他の記憶領域を冗長記憶領域として割り当て、冗長記憶領域にデータのコピーを格納することが可能なメモリ管理部151とを備える。メモリ管理部151は、メモリ102の使用率が所定の閾値を超えた場合には、冗長記憶領域の割り当てられた1または複数の記憶領域について、メモリ102の使用率が所定の閾値以下になるまで、各冗長記憶領域を段階的に未使用領域とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】リードディスターブを効率良く回避するための技術を提供する。

【解決手段】不揮発性半導体記憶装置(1)は、不揮発性記憶部(11)と、上記不揮発性記憶部の消去単位とされるブロック毎のデータを、当該ブロックとは異なるブロックに書き直すためのリフレッシュ処理を制御可能なコントローラ(12)とを含む。上記コントローラは、上記不揮発性記憶部に、第1領域とそれとは異なる第2領域とを設定し、上記第1領域のデータについてのリフレッシュ頻度が、上記第2領域のデータについてのリフレッシュ頻度に比べて高くなるように、リフレッシュトリガが発生される毎に上記第1領域及び上記第2領域についてのリフレッシュ処理を実行する。これにより、リードアクセスが繰り返される場合のリードディスターブを効率良く回避することができる。

(もっと読む)

メモリシステム

【課題】データ記憶の信頼性を容易に高めることができるメモリシステムを提供する。

【解決手段】実施形態のメモリシステムは、揮発性の第1の記憶部を介してホスト装置と不揮発性の第2の記憶部との間のデータ転送を行うコントローラを備えている。前記コントローラは、前記第2の記憶部に記憶されたデータの格納位置を含む管理情報を前記第1および第2の記憶部で更新しながら前記管理情報に基づいてデータ管理を行う。前記コントローラは、最新状態の管理情報と、当該管理情報の前記第2の記憶部での保存位置を示すポインタと、前記ポインタの書込みが成功したか否かを示すログとを、前記ポインタを多重化して前記第2の記憶部に記憶させる。前記コントローラは、起動時に前記ポインタが所望数だけ多重化されていなければ、前記ポインタおよび/または前記ログに基づいて、前記ポインタの多重化をリカバリ処理する。

(もっと読む)

半導体ディスク装置

【課題】複数の半導体ディスク3a、3bによりデータを記録する半導体ディスク装置1において、高信頼性を維持し、処理量およびオーバーヘッドを少なくする。

【解決手段】複数の半導体ディスク3a、3bによりミラーリング構成を成し、一の半導体ディスク3aの任意のアドレスにてセクタエラーを検出したときに、他の半導体ディスク3bから当該アドレスのデータを読み出して、前記一の半導体ディスク3aの前記アドレスに上書きするとともに、バックグラウンドにて一の半導体ディスク3aまたは3bの全アドレスのセクタエラーを検出しセクタエラーが検出されたときは他の半導体ディスク3bまたは3aから当該アドレスのデータを読み出して前記一の半導体ディスク3aまたは3bの前記アドレスに上書きするベリファイ動作を全ての半導体ディスクについて行うようにした。

(もっと読む)

データ記憶の方法及びシステム

【課題】マルチレベルセル(MLC)メモリモジュールを含む耐クラッシュメモリ(CPM)システムを提供する。

【解決手段】プロセッサ112がMLCメモリモジュール114と通信可能に結合されており、プロセッサは、第1のメモリ部分116において、第1のデジタル値を、第1のメモリ部分の各データ記憶セルの第1のレベルに書き込むことと、第1のデジタル値と同じである第2のデジタル値を各データ記憶セルの第2のレベルに書き込むことと、を行うようにプログラムされており、プロセッサは、第1のメモリ部分の各データ記憶セルの各レベルからデジタル値を読み出して、各データ記憶セルに単一のデジタルセル値を決定するようにプログラムされている。

(もっと読む)

データ修復装置

【課題】同一のデータが書き込まれた全ての領域に破壊された部分が存在する場合においても、破壊されたデータを修復すること。

【解決手段】CPU1は、全ての領域R0〜RNの同一オフセットアドレスのワードデータを1ワード分だけフラッシュROM6から読み出し、ワードデータが同じならば次の1ワード分のワードデータを読み出し、ワードデータが1個でも異なるならば、全ての領域R0〜RNのワードデータをマージすることでワードデータを再構築する。

(もっと読む)

1 - 20 / 181

[ Back to top ]