Fターム[5B018HA11]の内容

記憶装置の信頼性向上技術 (13,264) | 手段 (2,627) | 冗長符号 (791)

Fターム[5B018HA11]の下位に属するFターム

Fターム[5B018HA11]に分類される特許

1 - 20 / 56

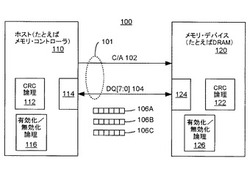

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置を提供する。

【解決手段】メモリ・システム100は、ホスト110とメモリ・デバイス120との間でデータを転送するためにデータ・フレームを使用する。いくつかの場合には、システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。いくつかの実施形態では、データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

携帯可能電子装置およびICカード

【課題】プログラムコードの自己診断が特定のコマンド処理時間に影響を与えることを避けるための分散処理、および、本装置がほとんど非活性化〜(再)活性化されない利用シーンにおける、プログラムコード自己診断の定期実施を可能とする携帯可能電子装置およびICカードを提供する。

【解決手段】ROMに格納されたプログラムコードを自己診断する自己診断機能を持つICカードにおいて、プログラムコードの自己診断を1つのコマンド処理内で全て実行するのではなく、複数のコマンド処理に分けて分散実行する。

(もっと読む)

NORフラッシュメモリの読み取り方法

【課題】NORフラッシュメモリの読み取り方法を提供する。

【解決手段】

本発明は、NORフラッシュメモリの読み取り方法を提供し、組込み式Linuxオペレーションシステムで使用され、巡回冗長検査値を照合し、カウンタに予め設けられた繰り返し読み取り回数の閾値により、ジャーナリングファイルシステムデータの繰り返し読み取りを継続するか否かを決定する。

(もっと読む)

データの安全な書き込み

【課題】データを、相対的に迅速に各込まれるようにすることを目的とする。

【解決手段】例えば、スマート・カードのようなデータ・プロセッサは、ファイルを管理するためのコントローラを具備し、複数のレコードが逐次記憶されることができる。コントローラは、レコードがファイルに正しく書き込まれたか調べる。コントローラは、正しく書き込まれた最後のレコードに続くレコードを、ユーザ関連ソフトウェアが読み取るのを防止する。

(もっと読む)

情報処理装置及びその作動方法

【課題】モジュールと本体側コネクタ間の接続不良に起因してモジュールが動作不良と判断されてしまうおそれがある。

【解決手段】サーバー100は、複数の接点を介してメモリ装置10が接続され、複数の接点を介してメモリ装置10から複数ビットのデータが入力するコネクタ20と、コネクタ20を介して入力する複数ビットのデータに含まれるビットにエラーが生じているか否かを判断するビットエラー検出部41と、ビットエラー検出部41によりエラーが検出されたビットに対応する接点を含む第1配線と、ビットエラー検出部41によりエラーが検出されなかったビットに対応する接点を含む第2配線と、に対してテスト波形を入力し、このテスト波形に応じて第1及び第2配線夫々にて生じる反射波のレベル差を評価することで第1配線の状態を判定する接続確認回路50と、を備える。

(もっと読む)

プログラム実行装置、プログラム生成装置、プログラム正否判定方法、および、プログラム加工方法

【課題】製造コストの削減や小型軽量化を図ると共に、スループットの低下を回避しつつ、オブジェクトプログラムを実行するタイミングでの誤り検出が可能となる。

【解決手段】プログラム実行装置120は、オブジェクトプログラムを実行する命令実行部220と、オブジェクトプログラムを一時的に保持するキャッシュメモリ222と、命令実行部によるオブジェクトプログラムのフェッチ要求を契機に、オブジェクトプログラムを読み込み、キャッシュメモリに保持させるプログラム読込部224と、読み込まれたオブジェクトプログラムに対し、順次、チェックコード導出式を計算し、ブロック単位でチェックコードを生成し、オブジェクトプログラムに予め挿入されているチェックコードと比較してオブジェクトプログラムの正否をブロック単位で判定するチェックコード判定部226とを備える。

(もっと読む)

制御装置及びこれを備えた電子機器、認証処理装置

【課題】 制御データの安定性を担保して、安定的な動作制御の実現を可能にした制御装置を提供する。

【解決手段】 設定レジスタ13は、ドライバ4,5に対して行われる制御内容に対応したオリジナル制御データ7AをROM7から取得し、設定済制御データとして登録する。誤り検出検査符号作成回路15は、設定済制御データに基づき所定の規則に従って設定済誤り検出検査符号を作成する。比較回路16は、ノイズ検出回路14において設定レジスタ13の電源用電圧が所定の許可条件を逸脱する変動をした場合には、オリジナル制御データ7Aに基づいて前記所定の規則に従って作成されたオリジナル誤り検出検査符号7BをROM7から読み出し、前記設定済誤り検出検査符号との比較を行う。設定レジスタ13は、前記両符号に齟齬が存在すればオリジナル制御データ7Aを改めてROM7から取得して設定済制御データとして再登録する。

(もっと読む)

誤り検出器、誤り検出器を有する半導体装置、誤り検出器を有する半導体装置を用いた情報処理装置及び誤り検出方法

【課題】メモリーなどの記憶装置に記憶したデータの誤り検出の負荷を低減すること。

【解決手段】第1のラッチと、第2のラッチと、データ比較回路と、を有し、ホストインターフェイスを介してホスト部より送信された制御コマンドを受信し、前記制御コマンドが第1のコマンドである場合は、前記第1のコマンドに付随するデータを順次前記第1のラッチに保持すると共に、データ記憶部に記憶されているデータを読み出し順次前記第2のラッチに保持し、前記データ比較回路により前記第1のラッチに保持されたデータと前記第2のラッチに保持されたデータとの比較を行うことを特徴とする誤り検出器を提供する。

(もっと読む)

記憶装置

【課題】バーストエラーに対する耐性の高い記憶装置を提供する。

【解決手段】本発明に係る記憶装置は、記憶するデータのパリティを計算する際に、バーストエラー長さの想定値をあらかじめ取得しておき、互いにその想定値以上離れた複数の記憶領域から読み出したデータを用いてそのデータのパリティを計算する。

(もっと読む)

コントローラ

【課題】プログラマブルロジックデバイスにおけるコンフィギュレーションデータのエラーを確実に検出すること。

【解決手段】 論理モジュールを構築する複数のコンフィギュレーションデータのCRCエラーを検出するCRCチェッカを備えたプログラマブルロジックデバイスを有し、プロセス制御における制御対象を制御するコントローラにおいて、定期的に前記複数のコンフィギュレーションデータの擬似エラーを生成してエラー検出状態を作り出し、前記CRCチェッカが前記擬似エラー以外のエラーを検出すると前記論理モジュールのリセット要求信号を出力するとともに前記プログラマブルロジックデバイスへのアクセスを停止する演算制御手段と、前記演算制御手段と前記プログラマブルロジックデバイスとのアクセスが停止すると前記論理モジュールのリセット要求信号を出力する第1のウォッチドッグタイマを、備えることを特徴とする。

(もっと読む)

バッテリーパック、及びデータフラッシュの動作の制御方法

【課題】データフラッシュの動作の制御方法とその機能を持つバッテリーパックを提供する。

【解決手段】本発明の一実施形態によるデータフラッシュの動作の制御方法は、2個のデータフラッシュの記録、コピー及び削除を、該当データフラッシュの特定領域に保存されている状態フラッグによって行うことによって、一つのデータフラッシュが満たされる場合、他のデータフラッシュに一部のデータをコピーするか、またはデータフラッシュを削除する途中で、リセットが発生する場合に発生するデータフラッシュ故障を防止できる。

(もっと読む)

誤り検出技術に基づくメモリ書き込みタイミングの調節

【解決手段】

誤り検出機能の結果に基づきメモリデバイスにおける書き込みタイミングを調節するための方法、システム及びコンピュータプログラム製品が提供される。例えば方法は、誤り検出機能の結果に基づきデータバス上の信号と書き込みクロック信号との間の書き込みタイミング窓を決定することを含むことができる。方法はまた、書き込みタイミング窓に基づきデータバス上の信号と書き込みクロック信号との間の位相差を調節することを含むことができる。メモリデバイスは、調節された位相差に基づきデータバス上の信号を回復することができる。

(もっと読む)

データ送信方法、システム及びサーバ

【課題】リカバリ処理等のためのデータ送信が中断された場合に、データ送信にかかる時間を従来よりも短縮する。

【解決手段】サーバは、複数のデータブロックの各々に固有な第1固有情報を生成して記憶した後に、各データブロックを順次、情報処理装置へ送信する。情報処理装置は、サーバから送信された各データブロックを順次受信する。情報処理装置は、サーバがデータブロックの送信を中断した場合には、サーバからデータブロックの送信再開指示を受けた後に、サーバから第1固有情報を取得し、受信済みのデータブロックの各々に固有な第2固有情報を生成し、データブロックを受信した順に、第1固有情報と第2固有情報とを比較し、第1固有情報と第2固有情報とが一致しないデータブロックの送信をサーバに要求する。

(もっと読む)

不揮発性記憶装置および不揮発性メモリコントローラ

【課題】全消去検出回路の出力と書き込みマークの有無に基づいて書き込み状態を制御回路によって判定することによって、正確に書き込み途中の電源遮断等の異常を検出することのできる信頼性の高い不揮発性記憶装置及びその書き込み判定方法を提供する。

【解決手段】不揮発性メモリから書き込み単位のデータを読み出す際に、全消去検出部によって読み出しデータが消去済みであるかどうかを判定すると共に、デスクランブル処理部によりデスクランブルされさらに誤り検出訂正部によって誤り訂正を行った後のデータの書き込み済みフラグ領域がフラグ書き込み済みであるかどうかを判別し、スクランブルパターン発生部によって生成される前記書き込み済みフラグ領域に対応するスクランブルパターンが、前記所定のビットパターンを消去済みの状態とは異なる状態にスクランブルする。

(もっと読む)

NAND型フラッシュメモリ保守装置及びNAND型フラッシュメモリ保守プログラム及びNAND型フラッシュメモリ保守方法

【課題】NAND型フラッシュメモリを備えた機器において、専用ハードウェアを追加することなく、エラーの起こりにくいNAND型フラッシュメモリを提供する。

【解決手段】読込回数管理部23はNAND型フラッシュメモリ装置130のブロックに含まれるいずれかのページが読み出されるたびに読出回数を各ブロック毎にカウントし、所定のブロックに書き込む。書込回数管理部24は、いずれかのブロックのいずれかのページにデータが書き込まれるたびに書き込み回数をカウントし、書き込み回数を所定のブロックに書き込む。診断部28は、読込回数管理部23によりカウントされた読出回数に基づいて、保守対象ブロックを選択する。保守部29は書込回数管理部24によりカウントされた書込回数に基づいて保守対象ブロックのすべてのデータを書き込む書込先ブロックを選択し、書込先ブロックに保守対象ブロックのデータを書き込む。

(もっと読む)

EEPROMのデータエラーチェック方法、及び制御ユニット

【課題】EEPROM内の記憶領域に書き込まれた各種データの正当性の判断に要する検査時間を短縮する。

【解決手段】検査装置3からEEPROM22についてのCRCエラーチェック要求をMCU21に送信する第1ステップと、前記CRCエラーチェック要求に従って、MCU21がEEPROM22内の記憶領域に書き込まれているデータを各アドレス毎に読み出す第2ステップと、MCU21がEEPROMから読み出した各アドレス毎のデータに基づいて各アドレス毎にCRCコードを算出し、当該算出した各CRCコードを検査装置3に送信する第3ステップと、検査装置3が、MCU21から送信されてきたCRCコードが予め定められた値に一致するか否かにより、EEPROM22内の各記憶領域に書き込まれているデータの正当性を判断する第4ステップとを備える。

(もっと読む)

データ処理装置、データ処理方法、及びデータ処理プログラム

【課題】データ書込み中のデータに誤りが発生する現象をできる限り救済することができるデータ処理方法等を提供する。

【解決手段】CPU201は、相変化メモリ202及びフラッシュメモリ203に記憶されるデータに対して管理番号、及び、前記入力されるデータの存在を示す符号としての「データあり」を付与し、第一のデータに関する情報として、管理エリア1(301)に記憶し、「データあり」が付与された場合に、前記データと同一のデータを、相変化メモリ202に、データの正当性を示す検証値と共に記憶し、前記第一の記憶手段によって前記データが記憶された場合に、フラッシュメモリ203に当該データと同一のデータを記憶し、フラッシュメモリ203に当該データと同一のデータが記憶された場合に、新たな前記データに関する情報として、前記第一のデータに関する情報に示される管理番号と同一の管理番号、及び、終了フラグNを付与し、第二のデータに関する情報として記憶する。

(もっと読む)

電子制御装置及びマイクロコンピュータ

【課題】データの誤りを検出する機能を備えた電子制御装置及びマイクロコンピュータにおいて、データに誤りが生じた際の誤動作や異常動作を、処理負荷を増大させることなく抑制する。

【解決手段】電子制御装置におけるマイクロコンピュータ100では、予め定められた固定データを記憶するメモリ17が設けられ、RAM112から読み出されたデータについてデコーダ14によって誤りが検出された場合は、RAM112から読み出されたデータに代え、メモリ17が記憶する固定データが読み出されて演算に使用される。固定データについて、例えば正常値として扱われるよう定義付けしておくことで、RAM112から読み出されたデータに誤りが生じていた場合でもマイクロコンピュータ100及び電子制御装置が正常に動作するようになる。

(もっと読む)

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されたエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するシステム、方法および装置を提供する。

【解決手段】メモリ・システムは、ホストとメモリ・デバイスとの間でデータを転送するためにデータ・フレームを使用する。システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

メモリ装置、メモリ管理方法、およびプログラム

【課題】書き換えの効率化と使用率の向上を図ることができ、また、停電時等の書き込み中や消去中のシステムダウン時においても正常な記憶状態に復帰することが可能なメモリ装置、メモリ管理方法、およびプログラムを提供する。

【解決手段】CPU13は、ブロックサイズの整数分の1かつページサイズの整数倍のトランスレーションユニット単位(TU単位)で論物変換を行って、NANDフラッシュメモリ11のアクセス管理を行い、ブロックの内容のうち、使用中の物理TUだけ全てを別の未使用の物理TUがあるブロックにコピーし、元のブロックを消去することにより、元のブロックに含まれていた無効の物理TUの数だけ、新たに未使用の物理TUを増やす操作制御を行う。

(もっと読む)

1 - 20 / 56

[ Back to top ]