Fターム[5B018HA40]の内容

記憶装置の信頼性向上技術 (13,264) | 手段 (2,627) | その他 (39)

Fターム[5B018HA40]に分類される特許

1 - 20 / 39

記憶装置

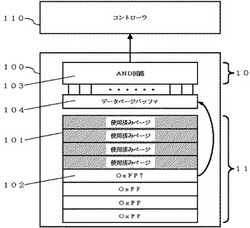

【課題】データページの読み込み時間の短縮を可能にするメモリシステムを提供する。

【解決手段】記憶装置は、所定の数のビットからなるデータページ102を複数有する不揮発性メモリ100と、ビットの状態出力を要求するコントローラ110とを有し、不揮発性メモリ100は、ビットの状態出力の要求を受けた際に、ビットの論理値を検査する論理回路103を有し、ビットが全て書き込み可または書き込み不可を示す論理値をコントローラに出力する。

(もっと読む)

記憶装置、記憶装置の制御方法およびコントローラ

【課題】容量の小さなバックアップ電源を使用して電源断時の不揮発化処理を可能とする。

【解決手段】電源断が発生する前の通常時に、少なくとも1つの消去済みフリーブロックが予備のブロックとして常に確保されているように不揮発性メモリに消去済みフリーブロックを作成し、電源断が発生した場合、予備のブロックを使用して不揮発化が完了していないデータおよび該データに関する論物変換情報を不揮発性メモリに書き込む不揮発化処理を実行する。

(もっと読む)

メモリシステム

【課題】高品質なメモリシステムを提供する。

【解決手段】メモリシステム1は、データ保持可能な不揮発性の半導体記憶部2と、半導体記憶部2の温度を計測する温度計測部9a、9bと、半導体記憶部2の温度を変化させる温度可変部8と、ホスト機器11から受信したデータを半導体記憶部2に転送する転送部、温度計測部9a、9bからの温度情報を記憶する温度記憶部、及び温度記憶部に記憶された温度情報に基づいて、温度可変部8を制御する温度制御部を具備する制御回路5と、を具備する。

(もっと読む)

データ記憶装置

【課題】フラッシュメモリなどのEEPROMにおいて、データ変化を防止する専用の記憶容量を設けなくても、データ変化及びデータ消失の抑制を可能とし、かつ、それに必要な処理能力を抑制することが可能な技術を提供することを目的とする。

【解決手段】監視記録装置56は、CPU1と、フラッシュメモリ2と、RAM3と、CPU1の使用率を計数する使用率計数部16とを備える。CPU1は、フラッシュメモリ2から記憶データを読み出してRAM3に記憶した後、再びRAM3からフラッシュメモリ2の元アドレスに書き戻す上書き処理を行う。CPU1は、この上書き処理を、使用率計数部16で計数された使用率が所定のしきい値よりも低い場合に実行する。上書き処理は他の処理によるフラッシュメモリ2への読み書きが禁止される排他処理とともに実行され、CPU1は、上書き処理を他の処理と時分割で実行する。

(もっと読む)

不揮発性メモリ装置

【課題】信頼性を向上させることができる不揮発性メモリ装置の提供。

【解決手段】メモリセルアレイの選択されたページからデータを読み出すか、或いはメモリセルアレイの選択されたページへ書き込むように構成されたページバッファ回路と、選択されたページに割り当てられたシードに基づいて、ページバッファ回路へ伝送されるか、或いはページバッファ回路から伝送されるデータをランダム化及びデランダム化するように構成されたランダム化及びデランダム化回路と、を有し、選択されたページは複数のセグメントで構成され、ランダム化及びデランダム化回路は、選択されたページに割り当てられたシードに基づいて選択されたページのアクセス要請されたセグメントの各々に対するランダムシークェンスを生成するように構成され、シードにしたがって反復的に生成されたランダムシークェンスに基づいて各アクセス要請されたセグメントのデータをランダム化及びデランダム化するように構成される。

(もっと読む)

記録装置及びその動作の制御方法

【課題】記録装置が省電力モードからの復帰する時に、SDRAMに関する不要な初期化処理を省略して高速な復帰処理を行うことである。

【解決手段】動作状態から停止状態に遷移する際、SDRAMをセルフリフレッシュ動作させるかどうかの情報をフラグに保持する。停止状態からの復帰時にフラグを参照し、停止状態においてSDRAMがセルフリフレッシュ動作を行っていた場合は初期化処理を省略する。

(もっと読む)

画像処理装置及び画像記録装置

【課題】 第1演算部と挿脱可能な外部メモリに接続される第2演算部とを備え、外部メモリの不具合を検出してユーザに通知することができる画像処理装置を提供する。

【解決手段】 プリンタ装置1の画像処理装置2は、メインCPU5と、サブCPU6と、外部メモリ11を挿脱可能なメモリスロット10とを備え、メモリスロット10は、外部メモリ11のSPD領域11bにアクセス可能な端子10bを有し、該端子10bはメインCPU5に接続されている。そして、メインCPU5は、サブCPU6の起動に先立ち、端子10bを介してSPD領域11bにアクセスし、外部メモリ11のエラーチェックを行うように構成されている。

(もっと読む)

メモリシステム

【課題】プログラムディスターブ、リードディスターブの影響やデータリテンションの劣化の影響を除去して信頼性を向上することが可能なメモリシステムを提供する。

【解決手段】複数のメモリセルを含む複数のブロックを有するメモリセルアレイと、前記メモリセルの読み出しレベルを変更可能な電圧生成部と、を有する不揮発性半導体記憶装置と、前記不揮発性半導体記憶装置の書き込み、読み出し、消去を制御する制御部とを具備し、前記制御部は、前記不揮発性半導体記憶装置の使用開始時と時間経過後とで読み出しレベルを変える。

(もっと読む)

電子機器制御装置及びそれを備えたテレビジョン受信装置

【課題】メモリへのデータ書き込み中に電源遮断が発生したか否かを確認できる電子機器制御装置を提供する。

【解決手段】電子機器制御装置20の書き換え可能な不揮発性メモリ19には、通常データ領域191と、書き込み開始データ領域192と、書き込み終了データ領域193と、書き込み中断データ領域194と、が備えられる。電子機器制御装置20の制御手段18は、起動時に、書き込み開始データ領域192及び書き込み終了データ領域193から読み出した2つのデータに基づいて、保存すべきデータの通常データ領域191への書き込み処理中に処理が中断されたことを示す書き込み中断データを書き込むか否かを判断する処理を行うと共に、前記書き込み中断データを書き込むと判断した場合に書き込み中断データ領域194に前記書き込み中断データを書き込む処理を行う。

(もっと読む)

メモリ装置

【課題】数十年以上の単位で記録データを長期的に安定に保存でき、しかも保存データを確実に読み出し可能なメモリ装置を提供する。

【解決手段】第1回路200は、データ記録回路210と、第2回路300からの読み出しまたは書き込み指示を受けて、アドレス信号に応じてデータ記録回路に対するデータの書き込みおよび読み出し制御を行う書き込み読み出し制御回路230と、を含み、第2回路300は、第1回路とのデータ転送制御を行うデータ転送制御回路310と、データ転送制御回路の作業用メモリ320と、を含み、データ転送制御回路310は、第1回路200のデータ記録回路210への書き込みデータを、いったん作業用メモリ320に蓄積し、蓄積したデータを順次に第1回路側の書き込み読み出し制御回路230に転送する。

(もっと読む)

記憶装置、その制御方法及びその記憶装置を備える電子装置

【課題】データバッファ上の全てのデータを、短い時間でフラッシュメモリに書き込むことが可能な記憶装置、その制御方法及びその記憶装置を用いた電子装置を提供する。

【解決手段】ホストから書き込み要求された書き込みデータを、フラッシュメモリに消去動作させることなく、フラッシュメモリに全て書き込めるか判断する書き込み判断部と、書き込み判断部により書き込めると判断された場合に、フラッシュメモリに書き込みデータを書き込む前に一時的に書き込みデータを記憶するデータバッファに、ホストから書き込み要求された書き込みデータを受信させるデータ受信制御部と、を備える。

(もっと読む)

携帯端末装置のメモリ制御方法、携帯端末装置及びプログラム

【課題】落下に起因する電源断による不揮発性メモリの記憶データの異常発生を防止し、携帯端末装置の動作の不具合を未然に防ぐと共に、消費電力を低減する。

【解決手段】CPU101は、不揮発性メモリ102のプログラム処理又はイレーズ処理の一定時間前の時点よりプログラム処理又はイレーズ処理の終了までの期間中、加速度センサ104の電源をオンに制御する。また、CPU101は、プログラム処理又はイレーズ処理の間、加速度センサ104の計測値に基づいて、下方向の加速度を算出し、その下方向の加速度の値から落下状態であるか否かを判定する。CPU101は、落下状態であると判定した時は、プログラム処理又はイレーズ処理を実施することなく加速度算出と落下判定を繰り返し、落下状態でないと判定した時は、プログラム処理又はイレーズ処理を実施する。

(もっと読む)

データ消失復帰装置

【課題】消失したデータを修復することができる小規模な回路規模のデータ消失復帰装置を提供する。

【解決手段】消失検知回路部35から制御ロジック回路部31にエラー信号が入力されると制御ロジック回路部31はウェイクアップする。この後、制御ロジック回路部31は外部メモリ2に記憶されたメモリデータを読み出す。そして、制御ロジック回路部31は、読み出したメモリデータを用いて予め決められた演算式に従ってエラー検出用データを生成し、生成したエラー検出用データと外部メモリ2から読み出したメモリデータをデータ保持レジスタ34に記憶する。そして、メモリデータがデータ保持レジスタ34に記憶されたことにより、消失検知回路部35からエラー信号が入力されなくなると、制御ロジック回路部31はスリープ状態に戻る。

(もっと読む)

記憶装置及び記憶装置の制御方法

【課題】搭載した回路基板上の記憶装置の接合部における損傷を確実に推定することにより、記憶装置の信頼性を確保する。

【解決手段】半導体メモリ50が搭載された複数個の半導体メモリパッケージがプリント基板に接合部を介して実装された記憶装置100であって、記憶装置100の状態に関する物理量を計測するセンサ部10と、物理量から接合部の損傷を推定するための損傷推定用モデルベースを蓄積したデータベース20と、損傷推定用モデルベース20を利用して、物理量から接合部の損傷の推定値を演算する損傷推定部30と、前記推定値に応じて、前記接合部を介して実装されている前記半導体メモリパッケージに搭載された前記半導体メモリへの電子データの書き込み、読み取り、消去を選択的に制御する制御部40とを備える。

(もっと読む)

電子機器及びプログラム

【課題】簡単且つ適切に、データ揮発を抑えることができるようにする。

【解決手段】ナビゲーション装置は、メモリカードに記憶されている地図データに基づき地図表示や経路案内等の処理を実現する。また、メモリカード内のデータについては、読出回数が多くなると揮発する確率が上がるため、読出回数の多いデータについては、RAMに保持し、メモリカードからの読出回数を減らす。また、ナビゲーション装置は、メモリカードに記録されているデータ書込日時からの経過時間を算出し、経過時間が閾値T1を越える度(S330でYes)、メモリカード内のデータ全体をリフレッシュする(S340)。但し、初回に限っては、経過時間が閾値T1よりも短い閾値T2を超えた時点で(S325でYes)、リフレッシュする。そして、リフレッシュ後には、メモリカードに、現在日時の情報を、データ書込日時として記録する(S350)。

(もっと読む)

データ放送システム、データ放送方法及びプログラム

【課題】受信機のNVRAM(不揮発性メモリ)の寿命になるまでの期間を延ばすデータ放送システム及びデータ放送方法を提供する。

【解決手段】放送局は映像等の情報メッセージからなる番組情報や、NVRAM格納モジュール、イベントメッセージを含むデータ放送を放送する。受信機は、NVRAM格納モジュールの基づいて、イベントメッセージの受信記録を、受信機の不揮発性メモリの複数のブロックに分散して格納する分散格納手段を有する。

(もっと読む)

電子装置及び揮発性メモリの待機電圧制御方法

【課題】揮発性メモリを搭載する電子装置であって、揮発性メモリの待機時のリーク電力を削減することができるようにした電子装置を提供する。

【解決手段】揮発性メモリ1が待機時から通常動作時に復帰したときは、誤り検出/訂正部8は、揮発性メモリ1を対象として誤りを検出し、誤り検出結果を全体制御部9に送り、全体制御部9は誤り検出結果を保存する。揮発性メモリ1が通常動作時から待機時に移行したときは、全体制御部9は、保存する誤り検出結果から前回待機時に誤りが発生したか否かを判断し、電源電圧供給部4を制御し、前回待機時に揮発性メモリ1に誤りが発生したときは、揮発性メモリ1に前回待機時よりも所定電圧値だけ高い待機電圧VDD3を供給させ、前回待機時に揮発性メモリ1に誤りが発生しなかったときは、揮発性メモリ1に前回待機時よりも所定電圧値だけ低い待機電圧VDD3を供給させる。

(もっと読む)

メモリシステム

【課題】NAND型フラッシュメモリに対する誤書き込みの発生を抑制する。

【解決手段】メモリシステムは、複数のページからなるメモリブロックを有するNAND型フラッシュメモリ11と、フラッシュメモリへのデータの書き込みを制御し、データを疑似乱数化するスクランブル回路26を有するコントローラと、を具備し、スクランブル回路は、セグメント単位で初期値を発生させる初期値発生回路36と、ページアドレス単位で初期値をNビットシフトさせる初期値シフト回路38と、Nビットシフトされた初期値を使用してM系列による擬似乱数列を発生させる疑似乱数発生回路39と、疑似乱数列をデータに加算する乱数加算回路33と、を有する。

(もっと読む)

メモリシステム

【課題】ランダマイズ解除処理による性能低下を改善する。

【解決手段】メモリシステムは、ランダマイズされたランダマイズデータが書き込まれる半導体メモリと、ランダマイズデータの読み出し時、ランダマイズデータのランダマイズを解除しながらバッファにランダマイズ解除後データを格納する第1のモードとランダマイズデータをバッファに格納する第2のモードとを読み出しの用途に応じて切り替えるMPUとを具備する。

(もっと読む)

半導体装置およびそれを備えた印刷記録材収容体、並びに制御装置

【課題】1つの接続確認用の端子で複数種類の接続確認を可能として、構成の簡易化を図ることを目的とする。

【解決手段】半導体装置10であって、内部回路20と接続端子とを備えている。接続端子としては、電源端子VT、リセット端子RT、クロック端子CT、データ端子DT、接続確認入力端子CIT、接地端子GTを備えている。各端子に接続される電子部品群は、第1段部S1と第2段部S2を備える。第1段部S1は、PNP型の第1のトランジスタQ1と2つの抵抗器R1,R2とから構成される。第1のトランジスタQ1は、電源端子からの給電開始時に、第2段部S2により所定時間だけターンオフされる。

(もっと読む)

1 - 20 / 39

[ Back to top ]