Fターム[5B018KA11]の内容

記憶装置の信頼性向上技術 (13,264) | エラー処理 (1,086) | 障害回復 (704)

Fターム[5B018KA11]の下位に属するFターム

再試行(リトライ) (52)

正常メモリへの置換 (91)

障害領域の非選択 (78)

ビット列単位の切替え (7)

アドレス単位の切替え (30)

領域単位の切替え (112)

訂正データの再書込み (86)

正常データの再ロード(転送) (181)

初期化 (49)

Fターム[5B018KA11]に分類される特許

1 - 18 / 18

記憶装置及び記憶装置の制御方法

【課題】データの不揮発性メモリ書き込みが中断されてしまっても、次回立上げでは不揮発性メモリのフォーマット不正を発生させずに立ち上げることができる記憶装置及び記憶装置の制御方法を提供すること。

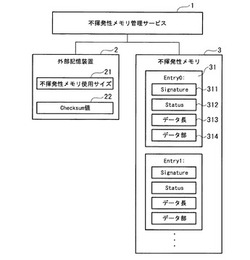

【解決手段】本発明の記憶装置は、不揮発性メモリ管理サービス1(制御機構)と、外部記憶装置2と、不揮発性メモリ3と、を備える。外部記憶装置2は、不揮発性メモリ使用サイズを格納する不揮発性メモリ使用サイズ21と、チェックサムを格納するChecksum値22と、を備える。不揮発性メモリ3は、複数のEntry 31(エントリ)を備える。複数のEntry 31の各々は、当該Entry が有効か否かを示すSignature 311と、Status312と、データ長313と、データ部314と、の各項目を備える。中断からの再開時には、チェックサムの再検証により、不揮発性メモリ3の障害か否かを判断する。

(もっと読む)

半導体記憶装置および制御方法

【課題】モニターセルを用いると情報を記録するメモリセルの量が減少する。

【解決手段】半導体記憶装置は、複数のメモリチップと、複数のパラメータ記憶部と、誤り訂正符号化部と、パラメータ処理部とを備える。メモリチップは、蓄えられた電荷量に応じた情報を記憶する。パラメータ記憶部は、対応するメモリチップに対する情報の書き込みまたは読み込みに用いる信号の電気的特性を定めるパラメータを記憶する。誤り訂正符号化部は、規定数以内のメモリチップに記憶された情報の誤りを訂正可能な第1訂正符号を生成する。パラメータ処理部は、規定数以内の個数のメモリチップに対するパラメータを変更し、変更したパラメータをパラメータ記憶部に書き込む。

(もっと読む)

メモリー制御装置およびプログラム並びにメモリー制御方法

【課題】論理物理変換テーブルに何らかの異常が生じてもデータアクセスを可能とする。

【解決手段】フラッシュメモリーの各物理ブロックの先頭に設けられた管理データ領域にインデックス情報(論理アドレス)を記録しておき、ホスト側から論理アドレスの指定を伴ってコマンドを受信した場合に論理アドレスを論理物理変換テーブルを参照して物理アドレスに変換し(S120)、物理アドレスが示す物理ブロックの管理データ領域からインデックス情報を読み出して論理物理変換テーブルが正常か否かを判定し(S130,S140)、正常でない場合には各物理ブロックの管理データ領域からインデックス情報を読み出して論理物理変換テーブルを修復すると共に(S150)、論理アドレスを修復した論理物理変換テーブルを参照して物理アドレスに変換し物理アドレスが示す物理ブロックにアクセスしてコマンドに応じた処理を実行する(S120〜S160)。

(もっと読む)

バッファメモリ装置、及び、バッファリング方法

【課題】バッファメモリを用いた装置において、ソフトエラーの発生によって使用されなくなったバッファメモリの領域を再度使用することを目的とする。

【解決手段】バッファ内の領域にデータを記憶し、当該バッファ内の領域からデータを読み出すバッファメモリ装置は、データを前記バッファ内の空き領域に書き込み、前記バッファ内の領域からのデータの読み出しに成功した場合は、当該領域を空き領域とし、読み出しに失敗した場合は、当該領域を廃棄領域とし、データが書き込まれてから所定の時間が経過した廃棄領域を検出し、検出した廃棄領域を空き領域とする。

(もっと読む)

情報処理装置及びプロセッサ並びに情報処理方法

【課題】情報処理装置について、装置構成を複雑化させることなく、動作の高速化と高信頼性を実現する。

【解決手段】本発明の一例である情報処理装置1は、プロセッサ2と、プロセッサ2に使用される不揮発性メモリ3と、プロセッサ2から不揮発性メモリ3への書き込みが発生した場合に、書き込み位置の重複回数を抑えるために当該書き込み位置がずれるように書き込みアドレスを発生させるアドレス発生手段16と、書き込みの新しさを表わす順序情報19を発生させる順序発生手段17と、アドレス発生手段16によって発生された書き込みアドレスに対して、順序発生手段17によって発生された順序情報19を対応付けて、書き込み情報21を記憶する書き込み制御手段18とを具備する。

(もっと読む)

メモリカード記録装置

【課題】記録途中にメモリカードを強制的に取り出された場合に発生する書き込み情報の欠陥を、時間経過があっても、修復前にファイルを記録されても修復できるメモリカード記録装置を、安価に提供することである。

【解決手段】本発明は、メモリカードへの書き込みと同時に、該メモリカードの情報記録単位毎のデータの上書き禁止を示す情報を記録するファイル配置テーブルを有し、該メモリカード内の書き込み済みデータの上書きを防止し、書き込みエラー発生以降は、補助記憶装置に残りの書き込みコマンド又は残りの書き込みデータなどの修復情報をメモリカードの個体識別情報とセットで保存する手段を有することを主要な特徴とする。

(もっと読む)

メモリシステム及びメモリアクセス方法

【課題】ランダムアクセス可能な不揮発性メモリにおける不良メモリセルを救済し、かつアクセス時間を低減する。

【解決手段】書き込みデータの冗長化符号処理を行う冗長化符号回路1と、前記冗長化符号処理されたデータの各ビットの値を反転するインバータ回路3と、選択信号に基づいて、前記冗長化符号処理されたデータ及び前記各ビットの値が反転されたデータのいずれか一方を選択するセレクタ4と、前記選択されたデータを記憶するメモリ7と、前記メモリから読み出されるデータと、前記選択されたデータとを比較し、比較結果を示す比較結果信号を出力する比較器5と、前記比較結果に基づいて前記選択信号を生成し出力する書き込み制御回路6と、前記メモリから読み出されるデータを冗長化復号処理して出力する冗長化復号回路2と、を備える。

(もっと読む)

カウントデータ記録装置、および、カウントデータ記録方法

【課題】本発明は、カウントデータ記録装置を提供する。

【解決手段】本発明は、記憶部と、データ書込部と、データ読出部と、データ修復部と、を有し、記憶部は、識別子で特定されるカウント記憶部と、カウント記憶部と関連付けされた極性情報データ記憶部とを備え、データ書込部は、循環的にカウント値を書き込むカウント書込部と、極性情報データ記憶部が記憶するデータの内容を反転させる極性情報データ反転部と、を備え、データ修復部は、カウント値の大きさで、識別子を並べるカウントソート部と、並べた識別子の順に沿って隣接するカウント値間の差分値を算出するカウント差分算出部と、識別子の並び方、差分値の並び方、および、極性情報データの並び方、に基づいて、カウント値の破損を検出して当該破損を修復する修復処理実行部と、を備える、カウントデータ記録装置である。

(もっと読む)

情報処理システムにおける接続装置の制御方法、制御プログラム及び情報処理装置

【課題】複数の共有記憶装置の格納情報が非対称になることを効果的に防止することを目的とする。

【解決手段】第1の接続装置に第1の共有記憶装置との接続を解除させ、第2の接続装置に第2の共有記憶装置との接続を解除させ、第1の接続装置とは異なる交換された他の第1の接続装置に第1の共有記憶装置と接続させ第2の接続装置に第2の共有記憶装置と接続させる。

(もっと読む)

メモリシステム

【課題】データ書き込み中にプログラムエラーが発生した場合でも確実に管理情報の復元が可能なメモリシステムを提供すること。

【解決手段】前ログの「ログ書き込み(1)」後、データ書き込みを行なっている時にプログラムエラーが発生した場合に(データ書き込みエラー)、データ再書き込み処理に対応する前ログを取得することなく、再度、データ書き込みを行なう。そして、データ書き込みを終えた後に、後ログを取ることなく、替わりにスナップショットを取得して処理を終了する。

(もっと読む)

メモリシステムおよび瞬断判定方法

【課題】メモリシステムの起動時に、前回終了時に瞬断が発生したか否かを速やかに判定することができるメモリシステムを提供する。

【解決手段】揮発性の第1の記憶部と、不揮発性の第2の記憶部と、データ転送とデータ管理を行うコントローラと、を備え、第2の記憶部は、起動時に必要な固定情報と固定情報の消去回数を示す消去回数識別情報が格納される固定情報格納領域が複数に多重化された固定領域を有し、コントローラは、固定情報の更新時に、固定情報格納領域それぞれ対して、消去回数識別情報の退避処理、固定情報格納領域の消去処理、新たな固定情報の書込み処理、退避した消去回数識別情報の更新および新たな固定情報が書込まれた固定情報格納領域への保存処理を行い、起動時に、多重化された複数の固定情報格納領域間の消去回数識別情報が一致しない場合には、固定情報の更新時に瞬断が発生したと判定する。

(もっと読む)

データ記憶装置及びその方法

【課題】不揮発性メモリに記憶されているデータに対して確実にアクセスし得るようにすると共に、使い勝手を格段と向上させ得るようにする。

【解決手段】制御部2は、フラッシュメモリ6に記憶させる複数種類のデータに対してデータ種別を示すための種別ヘッダHD1、HD2及びHD3を付加するようにしたことにより、PSRAM5におけるデータ種別/アドレス対応テーブルTBL1が破損又は消滅してしまった場合であっても、フラッシュメモリ6のデータ記憶ブロックBK0、BK1、BK2、……に記憶され続けている複数種類のデータのそれぞれのデータ種別を把握することができ、かくしてデータ種別/アドレス対応テーブルTBL1を再構築することができる。

(もっと読む)

システム環境復元方法

【課題】複数の情報処理装置を対象に、特別な環境を用意することなく容易にシステム環境の復元を行なうことができるシステム環境復元方法を提供する。

【解決手段】上記課題を解決するために、イメージファイル107を取得するイメージファイル取得手段101と、イメージファイル107を記憶装置109に書き込むイメージファイル書込み手段102と、自装置の装置特定情報を取得する装置特定情報取得手段103と、個別設定情報一覧108から個別設定情報を取得する個別設定情報取得手段104と、個別設定情報を復元したシステム環境に適用する個別設定情報設定手段105と、を備える。

(もっと読む)

情報制御装置およびメモリエラー復旧制御方法

【課題】情報制御装置全体の電源をOFFにすることなく、ソフトエラーの復旧が可能なメモリエラー復旧制御方法を提供する。

【解決手段】メモリ制御部7により内蔵のメモリ4への読み書き動作を制御する情報制御装置1内に、メモリ4への電源導通路9上に電源供給のON/OFFを切り替えるゲート回路3を備え、メモリ制御部7がソフトエラーを検出した際に、ゲート回路3をあらかじめ定めた一定時間の間OFFにし、メモリ4への電源供給をその間遮断して、メモリ4のソフトエラーを復旧させる。なお、上位装置20と接続している場合は、ソフトエラーを検出した旨を上位装置20に通知し、上位装置20から電源供給一時停止指令を受信した際に、メモリ4への電源供給を前記一定時間の間遮断する。ゲート回路3にさらにアドレスデコード回路を備え、メモリ4内のソフトエラー発生アドレスのみに対し電源供給を前記一定時間の間OFFにするようにしても良い。

(もっと読む)

プログラマブルデバイスに対するソフトエラーロケーションおよび感度検出

【課題】プログラマブルデバイスの構成メモリにおけるエラーを検出する方法を提供すること。

【解決手段】プログラマブルデバイスの構成メモリにおけるエラーを検出する方法であって、該構成メモリから構成メモリデータを読み取ることと、該構成メモリデータにおいてエラーが発生したか否かを判断することと、エラーが発生したという判断に応答して、エラーである該構成データに対応する感度データを読み取ることと、該エラーを無視することができるか否かを判断するために該感度データを解析することと、該エラーを無視することができない場合、修復アクティビティを開始することと、該エラーを無視することができる場合、該修復アクティビティを開始しないことによって該エラーを無視することとを包含する、方法。

(もっと読む)

データ書込制御装置

【課題】 各々異なるデータを格納する異なる記憶部にデータ格納不能が発生しても、速やかにデータ格納可能状態に復帰させることができるようにする。

【解決手段】 EEPROM5はIICバス3を介して機器動作上の重要データの読み書き可能なメモリである。RFIDモジュール7はEEPROM5と同じIICバス3を介してそれ以外のデータが書込まれるメモリである。CPU1はEEPROM5及びRFIDモジュール7に対してIICバス3を介してデータを選択的に書込制御する。また、CPU1は書込先のEEPROM5及びRFIDモジュール7について書込終了情報が得られないとき、RFIDモジュール7への駆動電源V2を瞬断制御する。

(もっと読む)

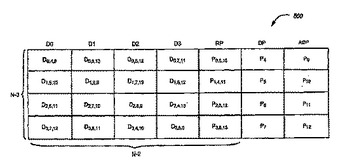

ストレージアレイにおける三重故障からの効率的な復旧を可能にする三重パリティ技術

アレイ内の3つの記憶装置の同時故障からの効率的復旧を可能にするように構成された、ストレージアレイの対角パリティ、及び反対角パリティの計算オーバヘッドを低減する三重パリティ(TP)技術。対角パリティは、アレイの全データディスク、及び行パリティディスクにわたって規定される幾つかの対角パリティ集合に沿って計算される。1つを除く全ての対角パリティ集合について、対角パリティが、対角パリティディスクに格納される。同様に、反対角パリティは、アレイの全データディスク、及び行パリティディスクにわたって規定される幾つかの反対角パリティ集合に沿って計算される。1つを除く全ての反対角パリティ集合について、反対角パリティが、反対角パリティディスクに格納される。TP技術は、均一なストライプの深さと、最適な量のパリティ情報を提供する。  (もっと読む)

(もっと読む)

ホットスワップ機能付きメモリシステム及びその障害メモリモジュールの交換方法

【課題】 シリアル伝送方式のメモリシステムで、システムを停止させずに障害メモリモジュールの交換を可能にする。

【解決手段】 開示されるホットスワップ機能付きメモリシステムでは、順次直列に接続されたメモリモジュール28,29,30を備えたシリアル伝送方式のメモリシステムにおいて、メモリコントローラ25が、メモリモジュール列の一端を一方の入出力部に接続され、常時はリード信号線26Aとライト信号線26Bを介して各メモリモジュールにアクセスしてデータのリード/ライトを行い、メモリモジュールの障害時、障害メモリとその前段のメモリモジュールとを切り離し、障害メモリモジュールの次段以降のメモリモジュールと末端に接続された予備メモリモジュール31とを、リード信号線26Bとライト信号線27Bとを介して順次直列に他方の入出力部に接続してアクセスすることで、障害メモリモジュールを挿抜可能な状態にする制御を行う。

(もっと読む)

1 - 18 / 18

[ Back to top ]