Fターム[5B018LA06]の内容

記憶装置の信頼性向上技術 (13,264) | 電源 (239) | 瞬断対策 (49)

Fターム[5B018LA06]に分類される特許

1 - 20 / 49

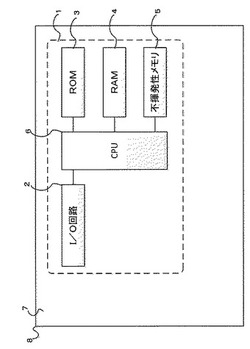

ICチップ、ICチップにおける処理方法、ICチップ用処理プログラム、及びICカード等

【課題】適切な保護機能によってデータを保護することにより、データの保護機能による処理時間の短縮を図るICチップ、ICチップにおける処理方法、ICチップ用処理プログラム、及びICカード等を提供する。

【解決手段】CPU6は、「カードOSによる非更新領域の保護機能」と、「トランザクションによる更新領域の保護機能」とを備え、「トランザクションによる更新領域の保護機能」は、更新前の更新領域が属するページの全ての領域を更新領域として、当該ページに記憶される全てのデータを前記バックアップ領域に書き込み、当該ページに非更新領域が存在しないものとしてカードOSに通知して、「カードOSによる非更新領域の保護機能」を機能させない。

(もっと読む)

メモリシステム

【課題】不正な電源断やデータ破壊を簡便かつ確実に検出することが可能なメモリシステムを提供する。

【解決手段】実施形態のメモリシステムは、揮発性の第1の記憶部と、不揮発性の第2の記憶部と、データ管理部と、復元制御部と、を備える。前記データ管理部は、前記第1の記憶部に記憶されている前記管理テーブルの更新前後の差分情報である差分ログを並列書き込み処理によって多重化して前記第2の記憶部に記憶させた後、書き込み単位分の所定データを最終書き込み単位分データとして多重化して前記第2の記憶部に記憶させる。前記復元制御部は、前記第2の記憶部に記憶された差分ログおよび前記最終書き込み単位分データのデータ記憶状態に基づいて、前記差分ログを前記第2の記憶部に記憶させる際に不正電源断が発生したか、または前記第2の記憶部でデータ破壊が発生したかの状態判断をシステム起動時に行う。

(もっと読む)

メモリシステム

【課題】 小容量の不揮発性メモリを効率的に利用することで異常電源断からの復元が可能なメモリシステムを提供する。

【解決手段】 実施形態に係るメモリシステムは、揮発性メモリを持つ。前記揮発性半導体メモリには、第1の不揮発性メモリが接続される。前記揮発性半導体メモリには、第2の不揮発性メモリが接続される。前記揮発性メモリに最新管理情報を記憶し、前記第1の不揮発性メモリに旧管理情報を記憶し、および前記第2の不揮発性メモリに前記最新管理情報と前記旧管理情報の差分データを記憶するメモリコントローラが設けられる。

(もっと読む)

不揮発性メモリの電源瞬断対応回路

【課題】小型・低コストのメリットを阻害することのない、マイコンと共通の電源電圧で動作する不揮発性メモリの電源瞬断対応回路であって、電源瞬断があっても確実なデータ保証が可能な不揮発性メモリの電源瞬断対応回路を提供する。

【解決手段】マイコン100のパワーオンリセット電圧VPORより上にある不揮発性メモリ94の動作保証電圧範囲VDD_MIN〜VDD_MAXにおいて、瞬断による電源電圧VDDの低下を検出し、瞬断検出信号を出力する瞬断発生検出回路40と、瞬断検出信号により、不揮発性メモリ94の書換え情報設定レジスタ94aにある書換え情報を該不揮発性メモリ94の外部で保持する書換え情報保持手段(ラッチレジスタ41)と、瞬断検出信号を保持する瞬断検出信号保持手段(瞬断検出フラグ42)とを有してなる電源瞬断対応回路とする。

(もっと読む)

ディスク装置

【課題】電源遮断時に電源を供給できるキャパシタCsを備え、揮発性メモリ15を経由して不揮発性メモリ14にデータを格納し電源遮断時に揮発性メモリ15に格納されたデータを不揮発性メモリ14に格納できるディスク装置1において、キャパシタCsの容量を精度よく測定し、確実にキャパシタCsの寿命を判定できるようにする。

【解決手段】キャパシタCsの負荷となる測定用負荷21と、キャパシタCsへの電源入力側と電源出力側にそれぞれ備えるスイッチSW1とスイッチSW2と、キャパシタCsと測定用負荷21との間に備えスイッチSW1とSW2のオンオフと背反してオンオフするスイッチSW3とを備え、所定の時に、スイッチSW3をオンとしキャパシタCsが所定の電圧Va以下となるまでの放電時間Taを測定し、当該放電時間Taに基づいてキャパシタCsの容量を推定できるようにした。

(もっと読む)

不揮発性記憶装置および不揮発性メモリコントローラ

【課題】多値メモリセルによって構成される不揮発性メモリを使用したメモリーカードに対してデータを書き込む際に、電源遮断が発生した場合、書き込み先のページとメモリセルを共有する、既にデータが書き込み済みのページのデータが破壊される可能性がある。このことが、メモリーカードのデータ信頼性を低下させる要因となっている。

【解決手段】外部からの書き込みコマンドの発行毎に、多値メモリセルによって構成される不揮発性メモリにおけるデータの書き込み先物理アドレスを決定し、書き込み先物理アドレスが第nページでありかつ対応する第1〜(n−1)ページに既書き込みのデータが存在する場合に、前記既書き込みデータを不揮発で記憶可能なバックアップ領域にコピーする。

(もっと読む)

コンテンツ再生装置

【課題】記憶部に対する履歴情報の書込み回数を低減するとともに、例えば突然の電源遮断の発生や時間計測回路の計時誤差が補正された場合でも、正確な履歴情報を記憶部に記憶させることの可能なコンテンツ再生装置を提供する。

【解決手段】表示部11又は音声出力部15にコンテンツ情報が再生される毎に該コンテンツ情報の履歴情報をそれぞれ記憶する不揮発性記憶部13a及び揮発性記憶部16aと、揮発性記憶部16aに記憶された複数の履歴情報を所定のタイミングで記憶部12に記憶させるとともに、記憶部12に記憶された履歴情報より新たに記憶された履歴情報が不揮発性記憶部13aに存在する場合に、該新たに記憶された履歴情報を不揮発性記憶部13aから取得して記憶部12に記憶させる制御部16とを備えた。

(もっと読む)

呼制御装置、方法及びプログラム

【課題】メインメモリ上で更新された呼制御アプリケーション及び呼制御情報を不揮発性メモリに保存できるようにする。

【解決手段】本発明の呼制御装置は、揮発性メモリ上にRAMディスク領域部を生成しておき、不揮発性メモリに格納される呼制御アプリケーション及び呼制御情報を揮発性メモリにローディングして呼処理を行い、不揮発性メモリに対する書き込み情報をRAMディスク領域に格納する呼制御装置で、RAMディスク領域の書き込み情報から、呼処理により揮発性メモリにローディングされた呼制御アプリケーション、呼制御情報を格納する不揮発性メモリの領域に対する書き込み情報を検知する更新検知処理手段と、更新検知処理手段の検知に基づいてRAMディスク領域の書き込み情報のうち呼制御アプリケーション、呼制御情報の領域に対する書き込み情報の不揮発性メモリへの書き込みを行う書き込み処理手段を備える。

(もっと読む)

不揮発性メモリを用いた記憶装置

【課題】バッファメモリのライトデータを、複数の不揮発性メモリデバイスを並列にアクセスして書き込む記憶装置に関し、電源遮断時のデータ消失を防止する。

【解決手段】複数の書き込み可能な不揮発性メモリデバイス(3−1〜3−16)を並列にアクセスするメモリコントローラ(2)が、電源遮断時に、特定の不揮発性メモリデバイス(3−A)のみを書き込み対象にし、バッファメモリ(18−1)から、不揮発性メモリデバイス(3−A)に書き込むデータを、書き込み済みでないライトデータに絞り込むことで、書き込み時に消費する電力を、抑えることが可能になる。

(もっと読む)

売上データ処理装置及びプログラム

【課題】売上データ処理装置において、主電源遮断時のデータのバックアップに使用される補助電源の消耗を低減させる。

【解決手段】本発明に係るECRによれば、CPU10は、他に実行すべき処理のない空き時間にハイバネーション用メモリ14に記憶されているデータの消去処理を実行し、AC電源31からの電源供給が遮断された際に、補助電源からの給電によりハイバネーション用メモリ14に記憶されている未消去の残存データの消去処理を実行しメインメモリ13に記憶されているデータをハイバネーション用メモリ14に退避させる。

(もっと読む)

車両制御装置

【課題】制御上の不都合を招くことない車両制御装置を提供すること。

【解決手段】本発明に係わる車両制御装置1は、通信規格を介して接続される複数の電子制御装置2、3と、複数の電子制御装置2、3に電源を遮断可能に供給する遮断供給手段5と、複数の電子制御装置2、3の内一の電子制御装置2に電源を投入する電源投入手段4とを備えるとともに、一の電子制御装置2に電源投入手段4により電源が投入された場合に、一の電子制御装置2の制御に基づいて遮断供給手段5が複数の電子制御装置2、3に電源を供給し、一の電子制御装置2への電源投入手段4による電源の投入が終了された場合に、一の電子制御装置2が他の電子制御装置3に終了処理開始通知を送信することを特徴とする。

(もっと読む)

メモリシステム

【課題】電源の異常遮断等からの復帰後にログが破壊されている可能性を排除して、管理情報の信頼性を高めることができるメモリシステムを提供すること。

【解決手段】管理情報復元部155はNANDメモリ12中の前ログ220Aや後ログ220Bを参照して、瞬断が発生したか否かを判定する。前ログ220Aまたは後ログ220Bが存在する場合には瞬断が発生したと分かり、その場合は、瞬断の発生したタイミングを判定し、復元に用いる前ログ220Aまたは後ログ220Bを選択した後、これらのログをスナップショット210に反映させて管理情報の復元を行なう。その後、NANDメモリ212内の全ての追記用ブロックに対してリカバリ処理を行い、さらに、スナップショット210を取り直して、過去のスナップショットとログを開放する。

(もっと読む)

メモリシステムおよび瞬断判定方法

【課題】メモリシステムの起動時に、前回終了時に瞬断が発生したか否かを速やかに判定することができるメモリシステムを提供する。

【解決手段】揮発性の第1の記憶部と、不揮発性の第2の記憶部と、データ転送とデータ管理を行うコントローラと、を備え、第2の記憶部は、起動時に必要な固定情報と固定情報の消去回数を示す消去回数識別情報が格納される固定情報格納領域が複数に多重化された固定領域を有し、コントローラは、固定情報の更新時に、固定情報格納領域それぞれ対して、消去回数識別情報の退避処理、固定情報格納領域の消去処理、新たな固定情報の書込み処理、退避した消去回数識別情報の更新および新たな固定情報が書込まれた固定情報格納領域への保存処理を行い、起動時に、多重化された複数の固定情報格納領域間の消去回数識別情報が一致しない場合には、固定情報の更新時に瞬断が発生したと判定する。

(もっと読む)

メモリシステム

【課題】多値メモリを使用したNAND型フラッシュメモリを有するメモリシステムで、上位ページに書込み中に瞬断などが発生した場合に、既に書込まれたデータを破壊から守ることができるメモリシステムを提供する。

【解決手段】揮発性の第1の記憶部と、多値データを記憶可能な複数のメモリセルからなり、複数のページを有するメモリセルが複数配列して構成される不揮発性の第2の記憶部と、第1の記憶部を介してホスト装置と第2の記憶部との間のデータ転送を行うコントローラと、を備え、コントローラは、第2の記憶部にデータを追記的に書込む前に、データを書込むページと同じメモリセルの下位のページにデータが書込まれている場合に、該下位のページのデータをバックアップする退避処理部155と、下位のページのデータが破壊された場合に、バックアップされたデータを用いて破壊されたデータを復元する破壊情報復元処理部156と、を有する。

(もっと読む)

情報処理装置およびデータ復旧方法

【課題】不揮発性主記憶部を備えたコンピュータにおいて、電池のような追加の電源を用いることなく、不意の電源断後の電源復旧時に不揮発性主記憶部に格納されたデータの状態を復元することができる情報処理装置およびデータ復旧方法を提供する。

【解決手段】バックアップ部110が不揮発性主記憶部120への書込みアクセスを検出した場合不揮発性主記憶部120から元データを読取り、バックアップデータを不揮発性バックアップメモリ130に書込んだ後不揮発性主記憶部120のアドレスにデータを書込み、コミット部140は一連の書込みアクセスごとに、シーケンス番号記憶部に記憶されたシーケンス番号を変更し、ロールバック部150はロールバック指示時に、シーケンス番号記憶部に記憶されたシーケンス番号と、データの有効を示す完全性検証用データとを含むバックアップデータを用いて、元データを不揮発性主記憶部120に書込む。

(もっと読む)

メモリシステム

【課題】ホスト装置の電源供給能力に応じて最適な動作を行う。

【解決手段】消費電流及びアクセス性能に応じた複数の動作モードを有するメモリシステム1であって、動作モードの遷移履歴を格納する不揮発性メモリ11と、不揮発性メモリ11との間で、同一動作モードにて一定量のデータをアクセスするごとに前記遷移履歴に当該動作モードを追加し、かつ前記遷移履歴を用いて現在の動作モードを決定するコントローラ12とを含む。

(もっと読む)

車両用電子制御装置

【課題】イグニッションスイッチのオン・オフ情報を送受信する通信に異常が生じても、フラッシュメモリに対するデータの書き込み中に電源供給が遮断されてしまうことを回避できるようにする。

【解決手段】ECMには、イグニッションスイッチのオン・オフ信号が入力され、イグニッションスイッチがオフされてからセルフシャットオフ時間が経過したときに、自身への電源供給をオフすると同時に、VELコントローラへの電源供給をオフする。前記VELコントローラは、前記ECMから前記イグニッションスイッチのオフ情報を入力すると、フラッシュメモリに対するバックアップデータの書き込みを行う。ここで、前記オフ情報の受信において通信異常があった場合には、実際のオフタイミングよりも大きく遅れてオフ情報を受け取った可能性があるので、フラッシュメモリへのデータの書き込みをキャンセルする。

(もっと読む)

メモリシステム

【課題】フラッシュメモリの寿命を拡大させるメモリシステムを提供する。

【解決手段】ホストHSTよりコントローラCTLを介してフラッシュメモリFMに対して書き込み命令がなされた場合に、CTLは、当該書き込みデータをRAMに格納し(S101)、当該書き込みデータがオールゼロ(ALL 00h)か否かをオールゼロ判定部ALL0Jを用いて判定する(S104)。当該書き込みデータがオールゼロであった場合、CTLは、当該書き込み命令に伴う論理アドレスに対応したFMのブロックに対して消去コマンドを発生する(S105)。これによって、オールゼロの書き込み命令がなされたFMのブロックを消去状態(オールイチ(ALL FFh))に保てるため、このブロックを、不良ブロックの救済用や、オールゼロ以外の書き込み用で使用することができる。

(もっと読む)

情報処理装置及びプログラム

【課題】電源オフ時に揮発メモリから不揮発メモリへより多くのデータを退避させることのできる情報処理装置を提供する。

【解決手段】電源電圧が、瞬断判別閾値以下のとき瞬断検知信号PSを出力する瞬断検知回路40を設ける。プロセッサ11は、瞬断検知信号PSを検知したとき、システムメモリ14から不揮発メモリ16へのデータ退避を開始し、瞬断検知信号が出力されてから所定時間の経過後にも瞬断検知信号が出力されている場合は、データ退避を継続すると共に、装置のシャットダウン処理を行なう。

(もっと読む)

ストレージ装置及びストレージ装置におけるデータの管理方法

【課題】本発明の課題は、不意の電源遮断時であっても、揮発性キャッシュメモリに保持されているデータの消失を防止することである。

【解決手段】本発明は、揮発性及び不揮発性メモリで構成されたキャッシュメモリを含むストレージ装置であって、揮発性キャッシュメモリには、ホスト装置からの書き込み要求に従うデータ及びディスクドライブからステージングされたデータをキャッシュする一方、不揮発性キャッシュメモリには、ディスクドライブからステージングされたデータのみをキャッシュするように構成されたストレージ装置である。不意の電源遮断時には、ストレージ装置は、揮発性キャッシュメモリにキャッシュされているダーティデータ及びその他の情報を不揮発性キャッシュメモリに直ちにバックアップする。

(もっと読む)

1 - 20 / 49

[ Back to top ]