Fターム[5B018MA24]の内容

記憶装置の信頼性向上技術 (13,264) | 対象 (1,668) | ICカード、メモリカード (351)

Fターム[5B018MA24]に分類される特許

1 - 20 / 351

メモリシステム及びそれのブロック複写方法

メモリアクセス制御装置および方法

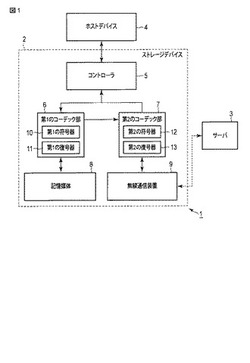

ストレージデバイス及び誤り訂正方法

【課題】ストレージデバイスにおいて、記憶媒体の記憶容量の低下を抑制しつつ、誤り訂正能力を向上させる。

【解決手段】実施形態に係るストレージデバイス2は、第1の符号器10と、記憶媒体8と、第2の符号器12と、無線通信部9とを含む。第1の符号器10は、書き込みデータの少なくとも一部に対応する第1の情報部と、第1の情報部の訂正に用いられる第1の冗長部とを含む第1の符号語を生成する。記憶媒体8は、第1の符号語を記憶する。第2の符号器12は、第1の符号語又は第1の情報部に対応する第2の情報部の訂正に用いられる第2の冗長部を生成する。無線通信部9は、第2の冗長部を、外部の記憶装置3へ無線通信する。

(もっと読む)

不揮発性メモリにおける書き込み欠陥からのデータ保護

【課題】メモリ装置の書き込み欠陥からデータを保護するための方法及びシステムを提供する。

【解決手段】この方法は、データアイテムのセットにわたる冗長情報を計算し、データアイテムを、メモリに記憶するために送信することを含む。冗長情報は、データアイテムがメモリに首尾良く書き込まれるまでの間のみ保持され、次いで、破棄される。データアイテムは、それをメモリに書き込むのに欠陥が生じたとき、冗長情報を使用して回復される。

(もっと読む)

ICチップ、ICチップにおける処理方法、ICチップ用処理プログラム、及びICカード等

【課題】適切な保護機能によってデータを保護することにより、データの保護機能による処理時間の短縮を図るICチップ、ICチップにおける処理方法、ICチップ用処理プログラム、及びICカード等を提供する。

【解決手段】CPU6は、「カードOSによる非更新領域の保護機能」と、「トランザクションによる更新領域の保護機能」とを備え、「トランザクションによる更新領域の保護機能」は、更新前の更新領域が属するページの全ての領域を更新領域として、当該ページに記憶される全てのデータを前記バックアップ領域に書き込み、当該ページに非更新領域が存在しないものとしてカードOSに通知して、「カードOSによる非更新領域の保護機能」を機能させない。

(もっと読む)

メモリコントローラ、記憶装置

【課題】読み出し動作の高速化及び信頼性の向上に有利なメモリコントローラ、記憶装置を提供する。

【解決手段】実施形態によれば、メモリコントローラ2は、外部インタフェイス1と、第1のECC生成部3aと、メモリ7a〜7eに対する書き込み及び読み出しを制御するアクセス部4と、読み出しデータのエラーを訂正する第1のECC訂正部3bと、これらを制御する制御部6とを具備する。前記制御部6は、メモリからデータを読み出す際に、第1の読み出し単位でデータを読み出し、前記第1の読み出し単位で読み出したデータにエラーが発生した場合に、前記第1の読み出し単位よりも読み出しサイズが小さい第2の読み出し単位に切り替えてデータを読み出し、前記第2の読み出し単位で読み出したデータに対して、前記第1のECC訂正部により前記第1のECC符号を利用してエラー訂正を行うように制御を行う。

(もっと読む)

車両用装置

【課題】データを正常にバックアップできないためにNAND型フラッシュメモリをリセットした場合であってもソフトの起動が遅れてしまうことがない車両用装置を提供する。

【解決手段】リセットシーケンサ3は、データのバックアップが正常に終了しなかったときは、起動要因を待機することなくCPU5を起動してSDカード7を「idle」状態から「tran」状態に移行させることにより、データのバックアップが正常に終了した次のアクセサリオン時にはすでにSDカード7を「tran」状態となっているようにする。これにより、アクセサリオン時にCPU5によるSDカード7に対するアクセスが直ちに可能となり、ソフトの起動が遅くなってしまうことを防止できる。

(もっと読む)

メモリの寿命を縮める動作を遅延させるシステム、方法、及びコンピュータプログラム製品

【課題】メモリの寿命を縮める動作を遅延させるシステム、方法、及びコンピュータプログラム製品を提供する。

【解決手段】メモリの寿命を縮める動作を遅延させるシステム500は、複数のストレージデバイス530、540を含むストレージシステム503が含まれている。コマンドの少なくとも一部は、寿命を縮めるコマンドであり、少なくとも一つのモジュール又はブロック531、532、533、541、542、543への悪影響を有する。使用中に、装置510は、そのような寿命を縮めるコマンドに拠らず、ストレージデバイス530、540の寿命を延ばすように働く。使用時に、メモリの寿命に関連する少なくとも一つの特徴が、特定される。このために、メモリの寿命を縮める少なくとも一つの動作が、当該特徴に基づいて遅延される。

(もっと読む)

メモリ装置

【課題】、復号効率のよいメモリカード3を提供する。

【解決手段】メモリカード3は、複数のメモリセル13Dと、HB読み出し電圧とSB読み出し電圧とを、メモリセル13Dに印加する制御を行うCPUコア11と、閾値電圧をもとにLLRテーブルから取得したLLRに基づき軟判定復号を行うECC部1と、を具備し、第1のLLRテーブル20Aから取得したLLRに基づいた復号が失敗した場合に、最高電圧の第1のHB読み出し電圧H07を中心とする閾値電圧分布を測定し、閾値電圧分布の最小頻度電圧VMと第1のHB読み出し電圧H07との差である第1のシフト値ΔV1が「負」の場合には、第2のLLRテーブル20Bから取得したLLRに基づき復号を行い、第1のシフト値ΔV1が「正」の場合には、第3のLLRテーブル20Cから取得したLLRに基づき復号を行う。

(もっと読む)

プログラム、情報処理システム、情報処理装置、および情報処理方法

【課題】他のデータに対するアクセスにより生じるエラーから特定のデータを保護できるプログラム、情報処理システム、情報処理装置、および情報処理方法を提供する。

【解決手段】例示的な実施の形態は、コンピュータで実行される、1つのメモリセルに複数ビットを記憶可能な半導体記憶手段に対してデータを書き込むためのプログラムを提供する。プログラムは、コンピュータに、第1のデータを記憶するための第1の領域を半導体記憶手段の記憶領域内に割り当てる割当ステップと、第1のデータの書込要求に応答して、第1の領域の境界から所定のサイズを保護領域とし、残りの領域を使用領域として、第1のデータを使用領域のみに書き込む書込ステップとを実行させる。

(もっと読む)

記憶装置

【課題】データページの読み込み時間の短縮を可能にするメモリシステムを提供する。

【解決手段】記憶装置は、所定の数のビットからなるデータページ102を複数有する不揮発性メモリ100と、ビットの状態出力を要求するコントローラ110とを有し、不揮発性メモリ100は、ビットの状態出力の要求を受けた際に、ビットの論理値を検査する論理回路103を有し、ビットが全て書き込み可または書き込み不可を示す論理値をコントローラに出力する。

(もっと読む)

メモリシステムとその制御方法

【課題】 データを確実且つ高速に書き込むことが可能なメモリシステムとその制御方法を提供する。

【解決手段】 メモリシステムは、第1、第2のディストリクト31a、31bと、制御部21を含んでいる。第1、第2のディストリクト31a、31bは、それぞれメモリセルアレイ32を有する。制御部21は、第1、第2のディストリクト31a、31bへ同時に第1のデータを書き込むための書き込みコマンド及びアドレスを受け、第1、第2のディストリクト31a、31bに同時に第1のデータを書き込む。

(もっと読む)

メモリコントローラ

【課題】半導体メモリを効率的に利用可能なメモリコントローラを提供すること。

【解決手段】実施形態のメモリコントローラ20は、第1インターフェイス21と、第2インターフェイス23と、制御部24とを備える。第1インターフェイス21は、ホスト10との間で信号を送受信する。第2インターフェイス23は、不揮発性の半導体メモリ30との間で信号を送受信する。制御部24は、第1インターフェイス21で受信した第1コマンドに応答して半導体メモリ30に予備領域を確保し、半導体メモリ30に保持されるデータの更新時には予備領域に更新データを書き込む。予備領域のサイズは、第1コマンドに応じて可変である。

(もっと読む)

メモリ制御装置及びメモリ制御プログラム

【課題】省エネ復帰時間を短縮しながらハングアップすることなく確実に復帰させることを目的とする。

【解決手段】省エネモード中の電源を監視して(100)、閾値以上の電圧が検出された場合には、省エネ復帰から通常復帰に切り換えて、メモリに記憶された展開情報を利用せずに、メモリを初期化して新たに情報を展開して復帰する通常復帰が行われるように制御し(104〜112)、閾値以上の電圧が検出されない場合にはメモリに記憶された展開情報を利用する省エネ復帰が行われるように制御する(104)。

(もっと読む)

情報処理装置および方法、並びに記録媒体

【課題】データの記録方式などが用途に応じて最適になるようにする。

【解決手段】記録媒体に記録されるデータの特性であって、当該データの保持期間を表す寿命値および当該データを読み出したときに発生すると想定されるエラーの割合を表すエラーレートを含む特性に基づいて、前記記録媒体により構成される論理デバイスの記録領域を複数生成するとともに、前記記録領域のそれぞれに適用される記録方式を決定する記録方式決定部と、前記決定された記録方式に基づいて、前記論理デバイスの記録領域のそれぞれを初期化する論理デバイス初期化部とを備える。

(もっと読む)

ICチップ、ICチップにおける処理方法、及びICチップ用処理プログラム

【課題】処理中断によりトランザクションが行われた場合であっても、処理時間制約が厳しい方のインターフェイスを用いた処理を正常に行うことが可能なICチップ、ICチップにおける処理方法、及びICチップ用処理プログラムを提供する。

【解決手段】ICチップは複数のインターフェイスに対応した処理手段と、データを記憶するデータ記憶領域と前記データをバックアップするためのバックアップ領域と、を有する不揮発性メモリと、第1の前記インターフェイスを用いた処理により受信されたデータを前記データ記憶領域に書き込む際に前記データ記憶領域に記憶されているデータを前記バックアップ領域にバックアップし、前記第1の前記インターフェイスを用いた処理が中断された場合には、前記バックアップ領域にバックアップされている前記データを前記記憶領域に書き戻す処理を行う制御手段と、を備える。

(もっと読む)

プラグインカード収容装置

【課題】エラー訂正回路の動作に起因して発生する消費電力の低減を図る。

【解決手段】プラグインカード収容装置は、受信した入力データを格納するメモリと、前記メモリに電気的に接続可能に設けられ、前記メモリから出力された前記入力データのエラーを訂正するエラー訂正回路とを含むプラグインカードと、前記プラグインカードが実装される装置本体と、前記装置本体に実装された前記プラグインカードに備えられる前記メモリのエラー率に基づいて前記プラグインカードの信頼性指標値を算出し、算出した前記信頼性指標値が基準値に近づくように、前記エラー訂正回路を前記メモリに電気的に接続するかどうかを決定するプロセッサとを有する。

(もっと読む)

情報処理装置および方法、並びにプログラム

【課題】より効率的に処理を実行できるようにする。

【解決手段】制御部は、データをnビット単位でアクセスし、記憶部は、mビット単位の管理データを複数個組み合わせてnビットになるように、管理データを記憶し、変換部は、制御部が管理データにアクセスする場合、mビット単位の管理データをnビット単位の管理データに仮想的に変換する。

(もっと読む)

メモリコントローラ、不揮発性記憶装置

【課題】不揮発性メモリにおいて第1の誤り訂正符号の訂正能力を超えるエラーが発生した場合でも、格納したデータを正しく読み出すことが可能で、かつ、小さいサイズの書き込みが効率的な不揮発性記憶装置、及びメモリコントローラを提供する。

【解決手段】不揮発性記憶装置1は、データを記憶する不揮発性メモリ12と、不揮発性メモリ12の制御を行うメモリコントローラ11とを備え、メモリコントローラ11は、データと同一ページに格納する第1の誤り訂正符号とは別に、第2の誤り訂正符号をも格納する。第2の誤り訂正符号の単位となるパリティグループよりもサイズの小さい書き込みにおいては、パリティグループとは別の領域に暫定的な第2の誤り訂正符号を格納する。データの読み出し時にはデータに付与された第1及び/または第2の誤り訂正符号を用いてエラー訂正を行う。

(もっと読む)

メモリコントローラ及び不揮発性記憶装置

【課題】不揮発性メモリにてワード線不良によるバースト誤りが発生した場合も、格納したデータを正しく読み出せる不揮発性記憶装置、及びメモリコントローラを提供する。

【解決手段】不揮発性記憶装置は、データを記憶する不揮発性メモリと、不揮発性メモリの制御を行うメモリコントローラとを備え、不揮発性メモリは、ブロックを複数含み、ブロックは、ページを複数含み、ブロック内には、一つのワード線を共有する2以上のページからなるページの組が少なくとも一つ存在し、メモリコントローラは、データを格納するページであるデータページと、データページの誤り訂正演算のための符号を格納する誤り訂正符号ページとを、夫々一つ以上含む、誤り訂正グループを複数構成し、同一の誤り訂正グループにおける、データページと誤り訂正ページの夫々に対してワード線の異なるページを割り当てる。

(もっと読む)

1 - 20 / 351

[ Back to top ]