Fターム[5B018NA02]の内容

記憶装置の信頼性向上技術 (13,264) | メモリの種類 (2,134) | RAM (515) | DRAM (160)

Fターム[5B018NA02]に分類される特許

1 - 20 / 160

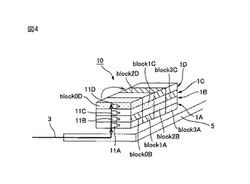

メモリモジュールおよび半導体記憶装置

【課題】電流の集中や発熱の集中を低減することができるメモリモジュールおよび半導体記憶装置の提供を図る。

【解決手段】複数のメモリチップ1A〜1Dが積層されたメモリモジュール10であって、前記各メモリチップは、複数のブロックに分割されたメモリセル部block0〜block3と、入力アドレス信号を処理して、動作させるブロックを選択するアドレススクランブル回路11A〜11Dと、を有する。

(もっと読む)

電圧制御

【課題】電子処理装置への電源電圧を最も効率の良い電力点で動作し、処理装置の出力の正確性を犠牲にすることなく、発生するエラーを修正することが可能な電圧制御方法を提供する。

【解決手段】プロセッサ又はメモリ要素を有する電子処理装置2への電源電圧を制御し電子処理装置の出力を受信する装置であって、当該装置は、電子処理装置の出力におけるエラーを検出するエラー検出手段5と、電子処理装置の出力において検出されたエラーの分析に基づいて、電子処理装置への電源電圧を適応的に変化させる手段6とを備える。装置は更に、電子処理装置の出力における検出されたエラーを修正する手段7を備える。

(もっと読む)

情報処理装置及び記憶部検査方法

【課題】CPUの運用中においても、記憶部の検査のためにCPUによるソフトウェアのデータ処理を一時停止させることがなく、記憶部の異常の有無をチェックすることができる情報処理装置及び記憶部検査方法を提供する。

【解決手段】CPU1とは独立に設置された記憶制御部2は、CPU1から書き込みようの処理データと書き込み先の記憶部3の指定アドレスを受け、検査用データを指定アドレスに書き込み、それを読み出す。記憶制御部2が備えるデータチェック部20は、検査用データと読み出されたデータとを比較し、一致するかどうかを判定する。一致しなければ指定アドレスに異常があると判定し、その旨をCPU1に通知し、一致すれば、記憶制御部は処理データを指定アドレスに書き込む。

(もっと読む)

共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置

【課題】共有されるエラー・ビット・コードをもつ共通フレームにおいてデータおよびデータ・マスク・ビットを転送するためのシステム、方法および装置を提供する。

【解決手段】メモリ・システム100は、ホスト110とメモリ・デバイス120との間でデータを転送するためにデータ・フレームを使用する。いくつかの場合には、システムは(別個のビット・レーンを介してではなく)データ・フレーム内で一つまたは複数のデータ・マスク・ビットも転送してもよい。システムは、データ・ビットおよびデータ・マスク・ビットをカバーするエラー・ビット・チェックサム(巡回冗長符号すなわちCRCのような)を生成してもよい。いくつかの実施形態では、データ・ビット、データ・マスク・ビットおよびチェックサム・ビットは共通フレームにおいて転送される。

(もっと読む)

メモリ制御装置及びメモリ制御プログラム

【課題】省エネ復帰時間を短縮しながらハングアップすることなく確実に復帰させることを目的とする。

【解決手段】省エネモード中の電源を監視して(100)、閾値以上の電圧が検出された場合には、省エネ復帰から通常復帰に切り換えて、メモリに記憶された展開情報を利用せずに、メモリを初期化して新たに情報を展開して復帰する通常復帰が行われるように制御し(104〜112)、閾値以上の電圧が検出されない場合にはメモリに記憶された展開情報を利用する省エネ復帰が行われるように制御する(104)。

(もっと読む)

DRAMをスタックする方法及び装置

【課題】スタックドメモリチップをシグナルインテグリティ等の問題を排除するように構成する。

【解決手段】第1の速度でアクセス可能な複数のセルから構成されるメモリコアを備え、垂直方向にスタックされた複数のDRAM集積回路と、第1の速度よりも大きい速度で、DRAM集積回路とメモリバスとの間でインタフェースを設けるインタフェース集積回路と、メモリスペアリングとを備え、スタックされたDRAM集積回路が(p+q)個のDRAM集積回路を備え、p個のDRAM集積回路が、メモリ集積回路の作業プールとして用いられる複数のDRAM集積回路を備え、q個のDRAM集積回路が、メモリ集積回路のスペアプールとして用いられる複数のDRAM集積回路を備える。

(もっと読む)

メモリ制御装置、画像処理装置、メモリ制御方法、メモリ制御プログラム及び記録媒体

【課題】ダブルレート型メモリの使用領域を有効活用しつつ使用環境に適したメモリアクセスを適切に行う。

【解決手段】複合装置は、メモリコントロール機能部30によって複数のパラメータに基づいてアクセスされるダブルレート型のメモリ13の所定の記憶領域を調整対象メモリ領域として、該調整対象メモリ領域のデータをメモリデータ記憶機能部22へコピーし、所定タイミングに、メモリデータ記憶機能部22のデータを、メモリ13の該調整対象メモリ領域へ書き戻して該調整対象メモリ領域のデータと比較してパラメータを決定して、メモリコントロール機能部30へ該メモリコントロール機能部30がメモリ13へのアクセスに用いるパラメータとして設定する。

(もっと読む)

データ記憶装置及びデータ処理装置及びコンピュータプログラム及びデータ記憶方法

【課題】実装面積を増大させることなく、ソフトエラーの発生を検出し、訂正できるようにする。

【解決手段】演算装置101(演算部)は、所定の演算により、複数の入力データ501に基づいて、誤り検出データ503を算出する。記憶装置102は、複数の入力データ501と、誤り検出データ503を記憶する。データ生成装置104(判定部・訂正部)は、記憶装置102が記憶した複数の入力データと記憶装置102が記憶した誤り検出データとの間に整合性があるか判定し、整合性がない場合、記憶装置102が記憶した複数の入力データと記憶装置102が記憶した誤り検出データとのうちから、誤っているデータを判定し、誤っていると判定したデータについて、正しいデータを算出する。

(もっと読む)

メモリ装置、メモリ制御装置、メモリ制御方法

【課題】ガベージコレクションの発生等に伴う他フラッシュメモリへのデータコピーを、コピーコマンドを使用する場合と同等に高速化する。

【解決手段】共通のデータ線が接続された複数のフラッシュメモリ部についてデータの読出/書込制御を行うように構成されたメモリ装置において、上記複数のフラッシュメモリ部のうち第1のフラッシュメモリ部に読出指示を行って当該第1のフラッシュメモリ部から上記共通のデータ線に読出データを出力させると共に、上記第1のフラッシュメモリ部から上記読出データが出力されるタイミングに応じたタイミングで、上記第1のフラッシュメモリ部とは異なる第2のフラッシュメモリ部に書込指示を行うことで、上記共通のデータ線に得られた上記読出データが上記第2のフラッシュメモリ部に書き込まれるようにする。

(もっと読む)

記憶装置のデータ保護装置

【課題】キャッシュ領域に転送済みのデータが消失することを防止することが可能な記憶装置のデータ保護装置を提供すること。

【解決手段】制御装置10に備わった、データが格納される不揮発性データ記憶領域14と、不揮発性データ記憶領域14に格納されるデータを一時的に保存するキャッシュ領域15とを有する記憶装置13のデータ保護装置であって、入力電源から供給される電源の電圧を所定の電圧に変換する内部電源装置11と、入力電源から供給される電源の電圧を監視し該電圧の低下を検出した時に電圧低下信号を出力する電源監視回路12と、電圧低下信号を受信したときキャッシュ領域15に保存されたデータを不揮発性データ領域14に書き込む書き込み指令を出力する中央演算処理回路16と、前記書き込み指令が出力されたとき、キャッシュ領域15に保存されたデータを不揮発性データ記憶領域14に書き込むようにした記憶装置のデータ保護装置。

(もっと読む)

記録装置及びその動作の制御方法

【課題】記録装置が省電力モードからの復帰する時に、SDRAMに関する不要な初期化処理を省略して高速な復帰処理を行うことである。

【解決手段】動作状態から停止状態に遷移する際、SDRAMをセルフリフレッシュ動作させるかどうかの情報をフラグに保持する。停止状態からの復帰時にフラグを参照し、停止状態においてSDRAMがセルフリフレッシュ動作を行っていた場合は初期化処理を省略する。

(もっと読む)

メモリコントローラ及び情報処理装置

【課題】読み出しデータの3bitエラーを考慮した上で、訂正可能エラーを判別することを可能にするメモリコントローラ及び情報処理装置を提供する。

【解決手段】ECC機能付きメモリモジュールに接続され、メモリモジュールへのアクセスを制御するメモリコントローラにおいて、メモリモジュールから読み出された複数の読み出しデータについて、読み出しデータに対応するECCの符号情報を、メモリモジュールより読み出して、エラービットの有無及びエラービットの位置の検出を行うエラー検出部と、複数の読み出しデータを一時的に格納するバッファと、バッファに格納された複数の読み出しデータに、エラー検出部によって訂正可能エラーが検出されたデータが複数含まれ、かつ、検出されたデータのエラー検出位置が同じ場合に、複数の読み出しデータ全体として訂正可能なエラーを含むと判定する判定部と、を備える。

(もっと読む)

記憶装置、記憶媒体再生方法および記憶媒体再生プログラム

【課題】メモリ素子の情報を正常に読み出すことができる記憶媒体再生装置を提供すること。

【解決手段】電荷量の大小に関連付けて情報を記憶する記憶部110と、第1の閾値と、記憶部110に記憶された電荷量とを比較して、比較結果に基づいて記憶部110から電荷量に関連付けられた情報を読み出す比較部104a〜104cと、読出した情報に誤りが存在するか否かを判断する誤り検出部106と、情報に誤りが存在すると判断した場合に、比較部104a〜104cが情報を読み出す際に用いた第1の閾値と異なる値の第2の閾値を生成する閾値生成部107とを備え、比較部104a〜104cは、情報に誤りが存在すると判断した場合に、閾値生成部107が生成した第2の閾値を第1の閾値として記憶部110から情報読み出すことを特徴とする。

(もっと読む)

メモリアクセス処理システム、制御方法、及びプログラム

【課題】CPUの要求するメモリアクセスを処理すること。

【解決手段】複数のメモリモジュール110のページのうち、過熱状態にあるメモリモジュール110のページを、過熱状態にないメモリモジュール110のページへ移動させるべく、過熱状態にあるメモリモジュール110のページの仮想アドレスと、過熱状態にないメモリモジュール110のページの仮想アドレスとを入れ替えるメモリ管理部150を備える。

(もっと読む)

試験方法,試験プログラム,及び試験装置

【課題】情報処理装置の記憶部に対する試験にかかる時間の短縮又は試験精度の向上を実現する。

【解決手段】同一の基礎パターンを隣り合わせて配設した基礎パターン対を含むテストパターン42を、記憶部4の試験領域40のうちの第1領域40Aに書き込み、書き込まれた前記テストパターン42を前記試験領域40のうちの第2領域40Bに転送し、転送されたテストパターン42を、前記第1領域40Aにおける前記書き込みが行なわれたアドレスから所定のシフト量だけシフトされたアドレスに転送するとともに、前記第1領域40Aあるいは前記第2領域40Bの一方から他方に転送されたテストパターンにおける基礎パターン対の隣り合わせて配設された基礎パターン同士が等しいか否かを比較、判定することにより前記試験領域40に対する書き込み及び読み出しを正しく行なえるか否かを検証する。

(もっと読む)

計算機、消費電力低減方法およびプログラム

【課題】メモリを省電力状態にすることによる省電力効果を最大限に得る。

【解決手段】メモリを備えた計算機であって、メモリを、当該メモリに対するアクセスが可能な通常状態と、当該メモリにおける消費電力が通常状態よりも低減され、当該メモリに対するアクセスが不可能な省電力状態とのいずれかの状態にするメモリ電源制御部と、メモリに対するメモリアクセスエラーを検出する検出部とを有し、メモリ電源制御部は、メモリが省電力状態である場合に、当該メモリに対するメモリアクセスエラーが検出部にて検出されると、当該メモリを通常状態に変更する。

(もっと読む)

メモリ制御装置および画像形成装置

【課題】セルフリフレッシュモード時の消費電流量を低減させる。

【解決手段】データを格納する複数のメモリ2,3と、メモリ2,3を制御する各信号を入出力するメモリコントローラ1と、各信号を接続/切断可能なスイッチ20と、を備え、メモリコントローラ1は、セルフリフレッシュモードへの移行時に、スイッチを切り替えて複数のメモリ2,3を、セルフリフレッシュモード時に電源供給されるメモリ2と、セルフリフレッシュモード時に電源遮断されるメモリ3と、に分け、電源遮断されるメモリ3上における保持が必要なデータを電源供給するメモリ2上に格納する。

(もっと読む)

メモリ・バックアップ中のデータ操作

【課題】電力分離およびバックアップ・システムを開示する。

【解決手段】電源異常状態が検出される時に、一時ストレージをSDRAMにフラッシュする。フラッシュの後に、インターフェースを停止し、電力を、SDRAMサブシステムを除くチップの大半から除去する。SDRAMサブシステムは、データをSDRAMからフラッシュ・メモリにコピーする。その途中で、データを暗号化し、かつ/またはデータ完全性署名を計算することができる。データを復元するために、SDRAMサブシステムは、データをフラッシュ・メモリからSDRAMにコピーする。その途中で、復元されるデータを暗号化解除し、かつ/またはデータ完全性署名をチェックすることができる。

(もっと読む)

メモリ・バックアップのための電力分離

【課題】電力分離およびバックアップ・システムを開示すること。

【解決手段】電源異常状態が検出される時に、一時ストレージをSDRAMにフラッシュする。フラッシュの後に、インターフェースを停止し、電力を、SDRAMサブシステムを除くチップの大半から除去する。SDRAMサブシステムは、データをSDRAMからフラッシュ・メモリにコピーする。その途中で、データを暗号化し、かつ/またはデータ完全性署名を計算することができる。データを復元するために、SDRAMサブシステムは、データをフラッシュ・メモリからSDRAMにコピーする。その途中で、復元されるデータを暗号化解除し、かつ/またはデータ完全性署名をチェックすることができる。

(もっと読む)

サーバ装置、メモリ装置

【課題】レジスタチップを搭載するためのコストを抑えつつ、メモリモジュールとメモリコントローラの間の通信を安定化させることのできる技術を提供する。

【解決手段】本発明に係るサーバ装置は、複数のメモリモジュールに対する命令を格納する共用レジスタを備える。メモリコントローラは、複数のメモリモジュールに対する命令を共用レジスタに格納し、共用レジスタは、メモリコントローラから受け取った命令を複数のメモリモジュールに対して並列出力する。

(もっと読む)

1 - 20 / 160

[ Back to top ]