Fターム[5B018NA04]の内容

記憶装置の信頼性向上技術 (13,264) | メモリの種類 (2,134) | ROM (1,578)

Fターム[5B018NA04]の下位に属するFターム

PROM (1,542)

Fターム[5B018NA04]に分類される特許

1 - 20 / 36

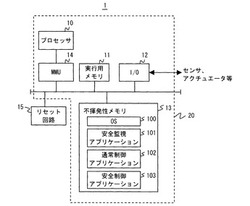

情報処理装置およびメモリ管理装置の動作確認方法

【課題】仮想アドレスを物理アドレスに変換するメモリ管理装置が正常に動作しているか否かを確認可能とする。

【解決手段】情報処理装置1は、メモリ11と、メモリ11の物理アドレス又はそれに対応する仮想アドレスを指定することで、メモリ11の物理アドレスに対してデータの読み出し又は書き込みを行うためのシステムプログラムと、システムプログラムを実行するプロセッサ10と、プロセッサ10からのメモリ11に対する仮想アドレスを指定した読み出し及び書き込みにおいて、仮想アドレスを物理アドレスに変換するメモリ管理装置14を備える。プロセッサ10は、システムプログラムによって、物理アドレスを指定してデータの書き込みを実施した後、その物理アドレスに対応する仮想アドレスを指定してデータの読み出しを実施して、書き込んだデータと、読み出したデータが一致するか否かを判定する。

(もっと読む)

半導体装置及びそのデータ異常判定方法

【課題】記憶手段を有する第1チップと、記憶手段に対してメモリデータの読み出しを指示する指示手段、及び、少なくとも多数決により、読み出された制御用データの信頼性を判定する判定手段を有する第2チップと、を備える半導体装置において、データ信頼性を向上しつつ、第2チップの体格増大を抑制する。

【解決手段】制御用データは、記憶先のアドレスの一部に対応するチェック用データが付加されてなるメモリデータとして、1つの制御用データにつき異なる3つのアドレスに記憶される。1つの制御用データに関する各アドレスにおいて、チェック用データに対応する一部を除く部分は、互いに異なるとともに複数の制御用データで同じとされる。また、3つのメモリデータに関し、制御用データ同士、チェック用データ同士、及び該チェック用データに対応するアドレスの一部同士は、それぞれ同じ或いはミラー反転の関係にある。

(もっと読む)

携帯可能電子装置およびICカード

【課題】プログラムコードの自己診断が特定のコマンド処理時間に影響を与えることを避けるための分散処理、および、本装置がほとんど非活性化〜(再)活性化されない利用シーンにおける、プログラムコード自己診断の定期実施を可能とする携帯可能電子装置およびICカードを提供する。

【解決手段】ROMに格納されたプログラムコードを自己診断する自己診断機能を持つICカードにおいて、プログラムコードの自己診断を1つのコマンド処理内で全て実行するのではなく、複数のコマンド処理に分けて分散実行する。

(もっと読む)

組込制御装置

【課題】DMA装置を停止させることなく、データ整合性を維持しつつ記憶装置のデータ整合性診断を簡易な構成で実施することのできる組込制御装置を提供する。

【解決手段】データ転送装置102が記憶装置103にデータを書き込み、またはデータを読み取っている記憶領域501のアドレスは、データ転送装置102が備えるレジスタに格納されている。演算装置101は、そのレジスタから記憶領域501のアドレスを知ることができるので、これを避けてデータ整合性診断を実施する。

(もっと読む)

電子装置、及び、これを用いた電動パワーステアリング装置

【課題】アドレスバスおよびデータバスの故障を検出する電子装置において、故障検出に係る処理負荷を低減し処理速度を向上する。

【解決手段】電子装置は、CPUとROMとを接続しアドレスを伝送する4つ以上のバスラインからなるアドレスバス21を備える。電子装置は、アドレスバス検査用アドレスAdによって指定されるROM領域13aから値を読み出し、読み出した値から計算した判定値Vjと予め計算されたアドレスバス検査用正解値Vtとを比較し、一致しない場合、アドレスバス21が故障していると判定する。アドレスバス検査用アドレスAdは、4つ以上のバスラインに対応する4ビット以上の値であって、2ビット以上の0の値と2ビット以上の1の値とを有する値を含み、複数のバスライン間の短絡故障を同時に検出可能である。これにより、故障検出に必要な検査用アドレスAdの数を低減することができる。

(もっと読む)

管理装置及び管理システム並びに管理方法

【課題】電池残量を気にすることなく情報閲覧装置を使用することができる管理装置及び管理システム並びに管理方法の提供。

【解決手段】電池で駆動する複数の情報閲覧装置を挿抜可能に保持するスロットを備える管理装置であって、所定の情報閲覧装置が前記スロットに挿入された場合に、前記所定の情報閲覧装置の電池残量に応じて、当該所定の情報閲覧装置に記憶されているデータを、前記スロットに挿入されている他の情報閲覧装置に移動する制御部を備え、前記制御部は、前記所定の情報閲覧装置の電池残量と前記他の情報閲覧装置の電池残量とを比較し、前記他の情報閲覧装置の電池残量が前記所定の情報閲覧装置の電池残量よりも多い場合に、前記データを移動する。

(もっと読む)

車載制御装置

【課題】ROM診断を効率よくかつ制御演算に与える影響を抑えながら実施することのできる車載制御装置を提供する。

【解決手段】本発明に係る車載制御装置は、制御プログラム外の処理が完了するのを待機する待機時間中に、読取専用メモリのうち一部の領域に対してメモリ診断を実施する。

(もっと読む)

制御装置及びこれを備えた電子機器、認証処理装置

【課題】 制御データの安定性を担保して、安定的な動作制御の実現を可能にした制御装置を提供する。

【解決手段】 設定レジスタ13は、ドライバ4,5に対して行われる制御内容に対応したオリジナル制御データ7AをROM7から取得し、設定済制御データとして登録する。誤り検出検査符号作成回路15は、設定済制御データに基づき所定の規則に従って設定済誤り検出検査符号を作成する。比較回路16は、ノイズ検出回路14において設定レジスタ13の電源用電圧が所定の許可条件を逸脱する変動をした場合には、オリジナル制御データ7Aに基づいて前記所定の規則に従って作成されたオリジナル誤り検出検査符号7BをROM7から読み出し、前記設定済誤り検出検査符号との比較を行う。設定レジスタ13は、前記両符号に齟齬が存在すればオリジナル制御データ7Aを改めてROM7から取得して設定済制御データとして再登録する。

(もっと読む)

コントローラ

【課題】プログラマブルロジックデバイスにおけるコンフィギュレーションデータのエラーを確実に検出すること。

【解決手段】 論理モジュールを構築する複数のコンフィギュレーションデータのCRCエラーを検出するCRCチェッカを備えたプログラマブルロジックデバイスを有し、プロセス制御における制御対象を制御するコントローラにおいて、定期的に前記複数のコンフィギュレーションデータの擬似エラーを生成してエラー検出状態を作り出し、前記CRCチェッカが前記擬似エラー以外のエラーを検出すると前記論理モジュールのリセット要求信号を出力するとともに前記プログラマブルロジックデバイスへのアクセスを停止する演算制御手段と、前記演算制御手段と前記プログラマブルロジックデバイスとのアクセスが停止すると前記論理モジュールのリセット要求信号を出力する第1のウォッチドッグタイマを、備えることを特徴とする。

(もっと読む)

電子制御装置

【課題】バックアップ対象となる情報が多いシステムにおいても、データ破壊に対する検出精度が高く、かつ局所的な処理負荷増大を防止した形で、データの損失を抑えた電子制御装置を提供する。

【解決手段】主電源復帰時に、中央演算処理装置10は、揮発性メモリ11が記憶したバックアップデータのSUM値を算出して、このSUM値を主電源遮断時に同様に算出したSUM値と比較し、一致しない場合であっても揮発性メモリ11の固有データと不揮発性メモリ12の固有データとが一致する場合、バックアップデータを初期化せずに保持する。

(もっと読む)

メモリ・デバイス上の故障注入による攻撃を検知する方法、及び対応するメモリ・デバイス

【課題】メモリ・デバイス上の故障注入による攻撃を検知する。

【解決手段】メモリ・デバイスがデータ・ビット及びmパリティ・ビットを備えたブロック(BL)を貯蔵するメモリ・プレーン(PM)のグループ、及び、ブロックの各ビットを読出す手段(ML)及びブロックの読出時に各データ・ビットの読出値及び各パリティ・ビットの読出値に基づきパリティ・チェックをする検証手段を備えた故障注入攻撃検知手段を備え、メモリ・プレーン(PM)はmメモリ・セルの別々のパケット(PQ)を形成するよう前記グループのメモリ・セル間に配置された参照メモリ・セルを備え、各参照メモリ・セルは故障注入攻撃の間に参照値で変更される参照ビットを貯蔵し、mメモリ・セルの各パケットは、異なるパリティに関連するブロックのmビットを貯蔵する。

(もっと読む)

記憶装置、基板、液体容器、データ記憶部に書き込むべきデータをホスト回路から受け付ける方法、ホスト回路に対し電気的に接続可能な記憶装置を含むシステム

【課題】記憶装置において、ホスト回路との通信の信頼性を向上する。

【解決手段】ホスト回路と電気的に接続される記憶装置は、不揮発性のデータ記憶部と、データ受信部と、判定部と、データ送信部とを備える。データ受信部は、ホスト回路からメモリアレイに書き込むべき第1のデータと、第1のデータに基づいて生成された第2のデータを受信する。判定部は、第1のデータと第2のデータとの整合性を判定する。データ送信部は、判定の結果をホスト回路に送信する。

(もっと読む)

電動パワーステアリング装置

【課題】電動パワーステアリング装置を制御する装置が有する記憶装置の不具合を診断する際の時間を短縮すること。

【解決手段】CPU101、ROM102、RAM103は、電動パワーステアリング装置の制御に用いられる。ROM102やRAM103は、電動パワーステアリング装置の制御に使用される情報を格納するとともに、複数のエリアに分割されている。複数のエリアは、電動パワーステアリング装置の制御における所定の処理単位毎に対応している。CPU101は、前記処理単位を実行するタイミングで、複数のエリアのうち、これから実行する処理単位に対応するエリアを診断する。また、CPU101は、前記処理単位を実行するタイミングでないときには、ROM102やRAM103に対する診断を実行しない。

(もっと読む)

ゲートウェイ装置及びそのメモリチェック方法

【課題】ゲートウェイ装置のイニシャル処理におけるメモリ領域であるROMチェック時間を短縮して、正常時にゲートウェイ装置を短時間で立ち上げる。

【解決手段】少なくとも1つのECUが接続する複数の通信ラインに接続し、各ライン間のデータの中継を行うゲートウェイ装置の、動作プログラムが格納されたROMを、データの中継機能部分とその他の部分に分割しておき、ゲートウェイ装置の初回のROMチェック時に、中継機能部分のチェックを行って正常時には直ちにゲートウェイ装置に中継動作を開始させ、中継動作中にその他の部分のチェックを行い、2回目以降は、前回のチェック結果が正常時に、ゲートウェイ装置の起動後にゲートウェイ装置に中継動作を開始させ、中継動作中に中継機能部分のチェックとその他の部分のチェックを行う。

(もっと読む)

マイクロプロセッサ

【課題】マイクロプログラムの読出し時にSEUを生じた場合においても対処できるマイクプロセッサを得る。

【解決手段】マイクロプログラム格納ROM1に格納されるマイクロ命令にパリティを付加する。パリティチェック回路5は、マイクロ命令レジスタ4に格納されたマイクロ命令のパリティチェックを行い、エラー検出時はパリティエラー検出信号を送出する。マイクロ命令実行部6は、パリティチェック回路5からパリティエラー検出信号が送出された場合は、例えば、マイクロプロセッサの実行を停止させる。

(もっと読む)

マイクロコンピュータ及びその検査方法

【課題】ROM内の配線不良に伴うデータ読出遅延を、より確実に検査することが可能なマイクロコンピュータ及びその検査方法を提供する。

【解決手段】マイクロコンピュータ1内のCPU10は、外部のテスタ2から供給されるクロックCLKに同期してROM20からデータDnを順次読み出し、テスタ2にデータDnの正常性と読出速度とを検査させる。また、CPU10は、データDnをデコードして分岐命令が得られた場合、次にデータを読み出すべきアドレスに代えて、前記分岐命令による分岐先アドレスAbからデータを読み出してテスタ2に検査させる。

(もっと読む)

メモリシステムおよび管理情報の保存方法

【課題】電源の異常遮断が起きて多値データの一部が破壊された場合であっても、異常遮断が起きる前の状態に容易に復帰させることができるメモリシステムを得ること。

【解決手段】揮発性の第1の記憶部と、多値データを記憶可能なメモリセルからなる不揮発性の第2の記憶部と、データ転送を行うとともに、第2の記憶部に記憶されたデータの格納位置を含む管理情報を第1の記憶部に取込み、この管理情報を更新しながら第1および第2の記憶部でのデータ管理を行うコントローラと、を備え、第2の記憶部は、第1の記憶部に取り込まれた最新の状態の管理情報を保存し、最新の状態の管理情報は、第1の記憶部の管理情報を保存したスナップショットと、管理情報に変更が生じる前に取得される変更前後の差分情報である前ログと、管理情報に変更が生じた後に取得される変更前後の差分情報である後ログと、を含む。

(もっと読む)

携帯端末の制御方法

【課題】ROMを有さない第1半導体チップに、第2半導体チップのROMから第1半導体チップ用のプログラムを転送した後、長期間、プログラムのベリファイを行なう機会が無いので、プログラムの信頼性が低下する。

【解決手段】電池の装着時など、携帯端末の使用を開始するときに、第2半導体チップのROMから第1半導体チップのRAMにプログラムの転送を行ない、その後、待ち受け状態において、着信の頻度に応じて決定されたベリファイ周期に基づいて、周期的に第1半導体チップのRAMに記憶されたプログラムのベリファイを実行する。

(もっと読む)

携帯可能電子装置および携帯可能電子装置の制御方法

【課題】 ICカードにおける自己診断処理を分散化して自己診断処理の占有時間を分散化することができ、ICカードにおける処理全体を効率化することができる。

【解決手段】 制御プログラムあるいはハードウエア回路などで実現される種々の機能を有するICカードが、ある1つの機能による処理を実行しようとする直前に、当該機能が正常であるか否かを診断する当該機能に対する自己診断処理を行い、その自己診断処理により当該機能が正常であると診断された場合に、当該機能による処理を実行する。

(もっと読む)

電子制御ユニットのメモリチェックシステム

【課題】ECUのリセット処理後再起動の時間を短縮し早期に電装品への制御を開始すると共に、メモリ異常が繰り返し検知された場合であっても電装品の誤動作やECUのリセット処理の反復を防止する。

【解決手段】車両に搭載されたROM15と、所定周期で周期処理を行うCPU13とを備えた電子制御ユニット10を備え、起動時に第1のリセット処理を開始してCPU13は周期処理を実行すると共に、周期処理の空き時間にROMのチェックを行い、メモリチェックで異常を検知した場合には、CPU13が自動的に第2のリセット処理を行い、第2のリセット処理後CPU13の周期処理の開始前に、再びROMのチェックを行い、該メモリチェックによりROM異常を検知した場合には、メモリチェックを繰り返して周期処理を行わないことを特徴とする。

(もっと読む)

1 - 20 / 36

[ Back to top ]