Fターム[5B018NA05]の内容

記憶装置の信頼性向上技術 (13,264) | メモリの種類 (2,134) | ROM (1,578) | PROM (1,542)

Fターム[5B018NA05]の下位に属するFターム

EAROM、EEPROM (1,535)

Fターム[5B018NA05]に分類される特許

1 - 7 / 7

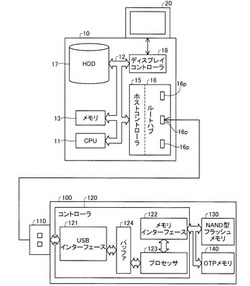

記憶装置、コンピュータ装置、コンピュータの制御方法、およびコンピュータプログラム

【課題】データの保持期間を長くする。

【解決手段】コンピュータシステムは、パーソナルコンピュータなどのホスト10と、ホスト10に接続されるUSBメモリデバイス100とを備える。USBメモリデバイス100は、ユーザ用データを格納するためのNAND型フラッシュメモリ130と、OTPメモリ140とを備える。NAND型フラッシュメモリ130には、ユーザ用データ以外に、ユーザ用データに対応した第1次のエラー訂正用符号であるECC_Aとが格納される。一方、OTPメモリ140には、ECC_Aに対応した第2次のエラー訂正用符号であるECC_Bが格納される。

(もっと読む)

リペア可能な半導体メモリ装置と該半導体メモリ装置のリペアリング方法

【課題】リペア可能な半導体メモリ装置を提供する。

【解決手段】半導体メモリ装置は、第1システムデータを保存する第1ブロックと第1システムデータと同一の第2システムデータを保存する第2ブロックとを有するメモリセルアレイを含む。コントローラは、ホストから出力されたリセット信号に応答して第1システムデータをメモリユニットに出力し、ECC検出ブロックによって発生したフェイル検出信号に基づいて第2システムデータをメモリユニットに伝送する。ECC検出ブロックは、第1システムデータが欠陥データであるか否かを判断する。半導体メモリ装置をリセットする間に第1システムデータで欠陷が発生する時、第1システムデータは、第2システムデータの提供によってリペアされる。

(もっと読む)

携帯時計用不揮発性メモリへのアクセス方法

本発明は、携帯時計の不揮発性メモリをプログラムするアクセス方法に関し、該時計は、基準電源電圧に対応する電位差を定め且つ外部からアクセス可能な2つの電源端子と、予め定められた最大電源電圧をサポートするよう構成された不揮発性メモリ用制御回路とを備え、当該アクセス方法は、時計の電源端子を利用して、a)不揮発性メモリへのアクセスを許可するオープニングキーと、b)不揮発性メモリへのアクセス命令とを不揮発性メモリの制御回路に送信する段階からなり、オープニングキーが予め定められた命令であって、基準電源電圧を変調することにより、予め定められた最大電源電圧を超えないようにして送信されることを特徴とする。  (もっと読む)

(もっと読む)

アクセス装置

【課題】重要データのより確実な保護ができ得るアクセス装置を提供する

【解決手段】メモリアクセス装置10は、論理メモリ空間を管理するファイルシステム装置14と、論理メモリ空間と物理メモリ空間との対応関係を記憶するとともに、当該対応関係に基づいてフラッシュメモリに物理的にアクセスするドライバ装置12と、を備えている。フラッシュメモリは、複数のストリングに物理的に分割されている。ファイルシステム装置12は、メモリ空間をROまたはRWのいずれかに設定された複数のパーティションに分割して管理する。ドライバ装置12は、各ストリングを単一の論理パーティションを対応させることで、一つのストリングに記憶されるデータの書込制限種類を統一させる。

(もっと読む)

情報処理装置

【課題】処理する情報の機密性を保つことができる情報処理装置を提供する。

【解決手段】本発明の情報処理装置であるプリンタ装置1は、PC2から画像データ及びジョブ情報と共にパスワードを受け付けた後、画像データを暗号化して記憶部106に記憶し、ジョブ情報にパスワードを関連づけてジョブ管理テーブルとして管理部104に記憶して処理を待機する。セキュリティプログラムが動作している場合は、主電源110が停止したときに、管理部104へ通電するバックアップ部105の動作を禁止して、管理部104が記憶しているジョブ管理テーブルを消去させる。セキュリティプログラムが動作していない場合には、バックアップ部105により管理部104へ通電して、管理部104に記憶しているジョブ管理テーブルを維持する。

(もっと読む)

フラッシュメモリーのデータ管理方法

【課題】フラッシュメモリーの安定性、データの安全性、耐障害性の性能を向上できるフラッシュメモリーのデータ管理方法を提供する。

【解決手段】本発明のフラッシュメモリー内のデータ管理方法は、メモリブロックの操作過程で、ブロックのステータスフラグを末完了状態に設定し、操作完了後は、ステータスフラグを末完了状態から、完了状態に設定する。この方法を利用して、フラッシュメモリーにデータの書き込んでいるときに、突然の電源切れが発生した場合でも、フラッシュメモリー内にあった元のデータの消失を防ぐことが出来る。また、本発明は、上記のデータ管理方法を採用したフラッシュメモリーにデータを書き込む方法とデータリカバーの方法も提供する。  (もっと読む)

(もっと読む)

誤り訂正回路およびこれを備えた物理量センサ装置

【課題】 基板面積を削減し得る誤り訂正回路を提供する。

【解決手段】 誤り訂正回路部14bでは、隣接するデータビットD0 〜Dn および検査ビットPn,0 〜Pn-1,n に対し、誤り訂正回路30が構成されている。これにより、メモリ回路部から読み出されたトリミングデータのうち、例えば、データビットD1 がデータ化けを起こしていても、「データビットD0 、検査ビットP0,1 およびデータビットD1 の排他的論理和の結果(E0,1 )」および「データビットD1 、検査ビットP1,2 およびデータビットD2 の排他的論理和の結果(E1,2 )」の論理積と、データビットD1 と、の排他的論理和をとるので、データビットD1 は反転、つまりデータビットの誤りを訂正しDout1として出力することができる。したがって、誤り訂正回路部14bの回路配線を簡素化できるとともに回路基板上の配線パターンの引き回しの錯綜を防止するので、基板面積を削減できる。

(もっと読む)

1 - 7 / 7

[ Back to top ]