Fターム[5B018QA14]の内容

記憶装置の信頼性向上技術 (13,264) | 時期 (2,030) | リード動作時 (179)

Fターム[5B018QA14]に分類される特許

1 - 20 / 179

メモリアクセス制御装置および方法

ストレージデバイス及び誤り訂正方法

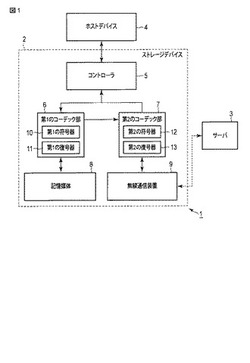

【課題】ストレージデバイスにおいて、記憶媒体の記憶容量の低下を抑制しつつ、誤り訂正能力を向上させる。

【解決手段】実施形態に係るストレージデバイス2は、第1の符号器10と、記憶媒体8と、第2の符号器12と、無線通信部9とを含む。第1の符号器10は、書き込みデータの少なくとも一部に対応する第1の情報部と、第1の情報部の訂正に用いられる第1の冗長部とを含む第1の符号語を生成する。記憶媒体8は、第1の符号語を記憶する。第2の符号器12は、第1の符号語又は第1の情報部に対応する第2の情報部の訂正に用いられる第2の冗長部を生成する。無線通信部9は、第2の冗長部を、外部の記憶装置3へ無線通信する。

(もっと読む)

遠隔装置に搭載される情報処理装置及び情報処理装置の起動方法

【課題】コンピュータプログラムを予め記憶したROMを必要とせず、かつコンピュータプログラムの破損を容易に解消させる、ことを目的とする。

【解決手段】情報処理装置10は、遠隔操作によって動作する遠隔装置に搭載され、コンピュータプログラムを実行するCPU20、及び該コンピュータプログラムを記憶する書き込み可能なRAMを備え、地上局50が備える送受信装置52から送信されるコンピュータプログラムを受信し、受信したコンピュータプログラムをRAMへ転送し、RAMにコンピュータプログラムが記憶されている状態でCPU20を起動させる。

(もっと読む)

メモリ装置

【課題】、復号効率のよいメモリカード3を提供する。

【解決手段】メモリカード3は、複数のメモリセル13Dと、HB読み出し電圧とSB読み出し電圧とを、メモリセル13Dに印加する制御を行うCPUコア11と、閾値電圧をもとにLLRテーブルから取得したLLRに基づき軟判定復号を行うECC部1と、を具備し、第1のLLRテーブル20Aから取得したLLRに基づいた復号が失敗した場合に、最高電圧の第1のHB読み出し電圧H07を中心とする閾値電圧分布を測定し、閾値電圧分布の最小頻度電圧VMと第1のHB読み出し電圧H07との差である第1のシフト値ΔV1が「負」の場合には、第2のLLRテーブル20Bから取得したLLRに基づき復号を行い、第1のシフト値ΔV1が「正」の場合には、第3のLLRテーブル20Cから取得したLLRに基づき復号を行う。

(もっと読む)

記憶装置

【課題】データページの読み込み時間の短縮を可能にするメモリシステムを提供する。

【解決手段】記憶装置は、所定の数のビットからなるデータページ102を複数有する不揮発性メモリ100と、ビットの状態出力を要求するコントローラ110とを有し、不揮発性メモリ100は、ビットの状態出力の要求を受けた際に、ビットの論理値を検査する論理回路103を有し、ビットが全て書き込み可または書き込み不可を示す論理値をコントローラに出力する。

(もっと読む)

情報処理装置および情報処理方法

【課題】複数の半導体メモリをストレージとして用いる場合のトータル的な応答性の向上を図ることのできる情報処理装置を提供する。

【解決手段】この情報処理装置は、複数の半導体メモリそれぞれの物理的特性を評価して、評価結果に見合った用途属性を、少なくとも一部の半導体メモリに割り当てる割当部と、データのライト命令に対して当該データのライト先として最適な用途属性の前記半導体メモリを判定する判定部とを具備する。複数の半導体メモリの物理的特性に個体差がある場合に、その半導体メモリの物理的特性が活かされるようにデータのライト先が判定部にて判定される。これにより、複数の半導体メモリを1つのストレージとして用いた場合のストレージのトータル的な応答性の向上を期待できる。

(もっと読む)

情報処理装置、情報処理方法、及び情報処理プログラム

【課題】よりセキュリティを向上しつつ、正常でないBIOSによる起動を抑止すること。

【解決手段】本発明にかかる情報処理装置9は、BIOS(Basic Input/Output System)910が予め格納されたBIOS記憶部91と、正常なBIOS910のデータと予め任意の値に定められた付加データとを含む合成データの誤り検出符号920を予め格納する符号記憶部92と、BIOS記憶部91に格納されたBIOS910を起動するときに、BIOS910のデータと付加データとを含む合成データの誤り検出符号を生成し、生成した誤り検出符号と符号記憶部92に格納された誤り検出符号920とを比較して、それらの誤り検出符号が一致しなかった場合、BIOS910の起動を抑止する管理部93とを備える。

(もっと読む)

情報更生装置、メモリ制御システム、情報更生方法およびコンピュータプログラム

【課題】 記憶容量が不足する事態を抑制しながら、メモリにおける情報保持性能の信頼性を高める。

【解決手段】 更生部2を備える。当該更生部2は、メモリから読み出された情報に含まれるビット誤りの数を誤りビット数として前記メモリにおける予め定められたメモリ領域毎に計数する機能を備えている。また、更生部2は、その誤りビット数が予め定められた閾値以上である前記メモリ領域には、当該メモリ領域とは別のメモリ領域に事前に書き込まれていたバックアップ情報を上書きする機能を備えている。

(もっと読む)

情報処理装置および方法、並びにプログラム

【課題】より効率的に処理を実行できるようにする。

【解決手段】制御部は、データをnビット単位でアクセスし、記憶部は、mビット単位の管理データを複数個組み合わせてnビットになるように、管理データを記憶し、変換部は、制御部が管理データにアクセスする場合、mビット単位の管理データをnビット単位の管理データに仮想的に変換する。

(もっと読む)

メモリ制御装置

【課題】 冗長化した半導体メモリのデータ記録制御を行う従来のメモリ制御装置は、半導体メモリに格納した符号化データを復号する場合に、半導体メモリの故障情報を利用していないため、宇宙環境での冗長化されたデータの記録再生に係る信頼性を十分に高められなくなっている。

【解決手段】 ハミング符号を用いて複数の半導体メモリに冗長化してデータを記録し、ハミング符号を復号して、データが誤りの場合にはメモリ故障と判定してデータ誤りのある半導体メモリを除いてから多数決処理を行うことにより、冗長化前の正しいデータを再生することができる。

(もっと読む)

半導体記憶装置

【課題】 長期間のデータ保持特性に優れ、読み出し時のデータの誤り検出および訂正を効率よく行うことのできる半導体記憶装置を実現する。

【解決手段】

金属酸化物を用いた可変抵抗素子を情報の記憶に用いる半導体記憶装置1において、当該可変抵抗素子を高抵抗状態に遷移させる場合に印加する書き換え電圧パルスの電圧振幅を、遷移後の高抵抗状態の抵抗値が時間の経過とともに上昇するデータ保持特性となる電圧範囲内に設定する。具体的には、当該電圧振幅を上昇させるに伴って遷移後の高抵抗状態の抵抗値が所定のピーク値に向って上昇する電圧範囲に設定する。そして、ECC回路106によりデータ誤りが検出された場合、本来低抵抗状態であるべきデータが高抵抗状態に変化したとみなして、誤りが検出された全てのメモリセルの可変抵抗素子を低抵抗状態に書き換え、誤りが検出されたビットを訂正する。

(もっと読む)

半導体装置

【課題】データの信頼性の向上を低コストで実現可能な半導体装置を提供する。

【解決手段】例えば、相補メモリを備えた半導体装置において、書き込み時に、(N+1)ビットの正極(Posi)データに対してパリティービットを生成し、(N+1)ビットの負極(Nega)データに対してパリティービットを生成する。読み出し時には、正極側および負極側のそれぞれに対してパリティーチェックを行うと共に、正極データと負極データを各ビット番号毎に比較する。ここで、正極データと負極データが同一データとなっているビット番号が存在した場合、正極側のパリティーチェック結果が異常であれば正極データの当該ビット番号を誤データとして特定でき、逆に負極側のパリティーチェック結果が異常であれば負極データの当該ビット番号を誤データとして特定できる。

(もっと読む)

印刷装置及びその制御方法

【課題】印刷データのリード速度が低下することを抑制すると共に、リードエラーを回復可能な半導体不揮発性記憶素子を搭載した印刷装置及びその制御方法を提供する。

【解決手段】装置全般の制御を司る制御部210は、高い処理スピードが要求される処理動作を実行することを検知する。制御部210は、データを記憶すると共にデータのリード時にリフレッシュする機能を持つ記憶部制御部221を備えた記憶部220からデータをリードする時にリフレッシュ動作を停止させるためのリフレッシュ停止手段を備える。制御部210は、高い処理スピードが要求される処理動作の際にリフレッシュ動作を停止させた場合に、高い処理スピードが要求される処理動作の終了後にリフレッシュ動作を許可するためのリフレッシュ許可手段を備える。

(もっと読む)

RAM値保証装置およびRAM値保証プログラム

【課題】RAMの記憶容量を抑制しながらRAMの記憶値を保証できるようにしたRAM値保証装置およびRAM値保証プログラムを提供する。

【解決手段】CPUは、OSによりプログラムカウンタ6の示すアドレスを監視し、非保証プログラム領域9から保証プログラム領域10にプログラムカウンタ6のアドレスが遷移することを確認すると、保証RAM領域12のデータとバックアップRAM領域13のデータとを比較し、当該データが異なっているときには保証RAM領域12のデータをバックアップRAM領域13のデータで更新する。CPU8はOSによりプログラムカウンタ6の示すアドレスを監視し、更新許可領域10aから更新許可領域10bにプログラムカウンタ6のアドレスが遷移することを確認すると、その遷移直前にRAM_A群バックアップ13aの更新を許可し、RAM_A群バックアップ13aのデータをRAM_A群12aのデータで更新し、更新処理後にRAM_A群バックアップ13aの更新を禁止する。

(もっと読む)

半導体装置及びそのデータ異常判定方法

【課題】記憶手段を有する第1チップと、記憶手段に対してメモリデータの読み出しを指示する指示手段、及び、少なくとも多数決により、読み出された制御用データの信頼性を判定する判定手段を有する第2チップと、を備える半導体装置において、データ信頼性を向上しつつ、第2チップの体格増大を抑制する。

【解決手段】制御用データは、記憶先のアドレスの一部に対応するチェック用データが付加されてなるメモリデータとして、1つの制御用データにつき異なる3つのアドレスに記憶される。1つの制御用データに関する各アドレスにおいて、チェック用データに対応する一部を除く部分は、互いに異なるとともに複数の制御用データで同じとされる。また、3つのメモリデータに関し、制御用データ同士、チェック用データ同士、及び該チェック用データに対応するアドレスの一部同士は、それぞれ同じ或いはミラー反転の関係にある。

(もっと読む)

情報処理システムおよび情報処理システムのバックアップ方法

【課題】複数の情報処理装置のソフトウェア環境を簡単にバックアップすることができる情報処理システムを提供する。

【解決手段】複数の情報処理装置とUSBメモリーと、から成る情報処理システムであって、USBメモリーは情報処理装置を制御する外部OSと、情報処理装置で実行する処理を定義したコマンドファイルを記憶し、各情報処理装置は外部OSを起動する装置起動部と、コマンドファイルに基づく処理を実行するコマンド実行部を備え、コマンドファイルにはバックアップ処理が定義されており、USBメモリーが接続された情報処理装置は、コマンドファイルに基づいて自身のシステム情報をバックアップすると共に、他の情報処理装置にバックアップの実行要求を送信し、他の各情報処理装置はバックアップの実行要求に基づいて自身のシステム情報をバックアップする。

(もっと読む)

メモリシステム

【課題】読み出し動作開始から読み出し動作完了までの処理時間を可及的に低減する。

【解決手段】制御部は、不揮発性メモリに格納されているデータを読み出す際、読み出し電圧管理情報に記録されている読み出し電圧の値を用いて不揮発性メモリからデータを読み出して、誤り検出部が読み出されたデータに誤りを検出したとき、誤り検出部が読み出されたデータに誤りを検出しなくなるまで読み出し電圧を変更して前記不揮発性メモリからデータの再読み出しを行い、誤り検出部が読み出されたデータに誤りを検出しなくなったとき、読み出し電圧管理情報に記録されている読み出し電圧を更新する。

(もっと読む)

誤り訂正回路およびメモリ装置、並びに誤り訂正方法

【課題】高速な誤り訂正を可能とし、誤り訂正回路の規模や消費電力の増大を抑えることができる誤り訂正回路およびメモリ装置、並びに誤り訂正方法を提供する。

【解決手段】冗長化された奇数個の二値情報を電流値で入力する入力手段153と、前記入力手段から入力する前記奇数個の電流値の和を電圧に変換する変換手段151と、前記変換手段が出力する前記電圧が予め設定された第1閾値以上であるか否かに応じて二値情報を出力する第1判定手段152とを備える。

(もっと読む)

メモリコントローラ及び情報処理装置

【課題】読み出しデータの3bitエラーを考慮した上で、訂正可能エラーを判別することを可能にするメモリコントローラ及び情報処理装置を提供する。

【解決手段】ECC機能付きメモリモジュールに接続され、メモリモジュールへのアクセスを制御するメモリコントローラにおいて、メモリモジュールから読み出された複数の読み出しデータについて、読み出しデータに対応するECCの符号情報を、メモリモジュールより読み出して、エラービットの有無及びエラービットの位置の検出を行うエラー検出部と、複数の読み出しデータを一時的に格納するバッファと、バッファに格納された複数の読み出しデータに、エラー検出部によって訂正可能エラーが検出されたデータが複数含まれ、かつ、検出されたデータのエラー検出位置が同じ場合に、複数の読み出しデータ全体として訂正可能なエラーを含むと判定する判定部と、を備える。

(もっと読む)

半導体メモリ装置および復号方法

【課題】復号の処理速度が速いメモリカード3を提供する。

【解決手段】メモリカード3は、1個のメモリセルに記憶する、読み出し単位であるページが異なる3ビットのデータを、8個の閾値電圧分布に基づく確率を用いた反復計算により復号を行うときに、ハードビット読み出しのための7個の基準電圧のそれぞれと、ソフトビット読み出しのための、それぞれの基準電圧よりも低い電圧および高い電圧からなる複数の中間電圧と、からなる7組の電圧セットのうち、読み出すページに属する1ビットデータの読み出しに必要な電圧セットの電圧を選択し、選択した前記電圧セットの電圧を読み出し電圧として前記メモリセルに印加する制御を行うワード線制御部21と、対数尤度比を記憶する対数尤度比テーブル記憶部22と、読み出したデータを対数尤度比を用いてECCフレーム単位で復号をする復号器1と、を有する。

(もっと読む)

1 - 20 / 179

[ Back to top ]