Fターム[5B018RA12]の内容

記憶装置の信頼性向上技術 (13,264) | エラーの種類 (442) | プログラム (42)

Fターム[5B018RA12]に分類される特許

1 - 20 / 42

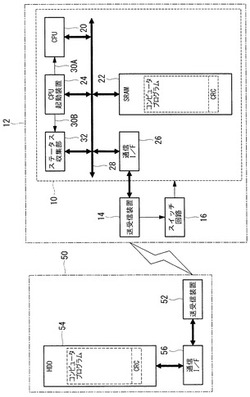

遠隔装置に搭載される情報処理装置及び情報処理装置の起動方法

【課題】コンピュータプログラムを予め記憶したROMを必要とせず、かつコンピュータプログラムの破損を容易に解消させる、ことを目的とする。

【解決手段】情報処理装置10は、遠隔操作によって動作する遠隔装置に搭載され、コンピュータプログラムを実行するCPU20、及び該コンピュータプログラムを記憶する書き込み可能なRAMを備え、地上局50が備える送受信装置52から送信されるコンピュータプログラムを受信し、受信したコンピュータプログラムをRAMへ転送し、RAMにコンピュータプログラムが記憶されている状態でCPU20を起動させる。

(もっと読む)

情報処理装置、情報処理方法、及び情報処理プログラム

【課題】よりセキュリティを向上しつつ、正常でないBIOSによる起動を抑止すること。

【解決手段】本発明にかかる情報処理装置9は、BIOS(Basic Input/Output System)910が予め格納されたBIOS記憶部91と、正常なBIOS910のデータと予め任意の値に定められた付加データとを含む合成データの誤り検出符号920を予め格納する符号記憶部92と、BIOS記憶部91に格納されたBIOS910を起動するときに、BIOS910のデータと付加データとを含む合成データの誤り検出符号を生成し、生成した誤り検出符号と符号記憶部92に格納された誤り検出符号920とを比較して、それらの誤り検出符号が一致しなかった場合、BIOS910の起動を抑止する管理部93とを備える。

(もっと読む)

情報処理装置、画像形成装置およびプログラム

【課題】プログラムの誤動作の発生を抑制する。

【解決手段】動作制御部は、プログラムを実行するCPUと、プログラムを格納するとともにプログラムの実行に伴って発生するデータを格納するメインメモリ512とを有している。メインメモリ512は、読み書き可能であって、電源を供給しなくても、記憶している情報を保持することが可能なMRAM61と、電源を供給しないと、記憶している情報を保持することができないDRAM62とを備えており、MRAM61の一部領域にはプログラム等が格納されるROM領域A1が設けられ、MRAM61の残りの領域およびDRAM62のすべての領域にはデータ等が格納されるRAM領域A2が設けられる。CPUがリセットされると、ROM領域A1の記憶内容をそのままとする一方でRAM領域A2の記憶内容を消去し、ROM領域A1から読み出したプログラムを実行する。

(もっと読む)

情報更生装置、メモリ制御システム、情報更生方法およびコンピュータプログラム

【課題】 記憶容量が不足する事態を抑制しながら、メモリにおける情報保持性能の信頼性を高める。

【解決手段】 更生部2を備える。当該更生部2は、メモリから読み出された情報に含まれるビット誤りの数を誤りビット数として前記メモリにおける予め定められたメモリ領域毎に計数する機能を備えている。また、更生部2は、その誤りビット数が予め定められた閾値以上である前記メモリ領域には、当該メモリ領域とは別のメモリ領域に事前に書き込まれていたバックアップ情報を上書きする機能を備えている。

(もっと読む)

電子機器、制御方法及びプログラム

【課題】BIOSデータがOS起動中に破壊されてしまっても、そのBIOSデータを復元することが可能な電子機器を提供する。

【解決手段】 本実施形態の電子機器(100)は、電源(15)が投入された際に、データを記憶する第1の記憶手段(12)に格納されているBIOSデータを、第1の記憶手段(12)とは異なる第2の記憶手段(13)にコピーし、OSを終了する際に、第1の記憶手段(12)に格納されているBIOSデータと、第2の記憶手段(13)にコピーしたBIOSデータと、を比較し、双方のBIOSデータが異なる場合は、第2の記憶手段(13)にコピーしたBIOSデータを、第1の記憶手段(12)にコピーする。

(もっと読む)

データ修復装置

【課題】同一のデータが書き込まれた全ての領域に破壊された部分が存在する場合においても、破壊されたデータを修復すること。

【解決手段】CPU1は、全ての領域R0〜RNの同一オフセットアドレスのワードデータを1ワード分だけフラッシュROM6から読み出し、ワードデータが同じならば次の1ワード分のワードデータを読み出し、ワードデータが1個でも異なるならば、全ての領域R0〜RNのワードデータをマージすることでワードデータを再構築する。

(もっと読む)

プログラム実行装置、プログラム生成装置、プログラム正否判定方法、および、プログラム加工方法

【課題】製造コストの削減や小型軽量化を図ると共に、スループットの低下を回避しつつ、オブジェクトプログラムを実行するタイミングでの誤り検出が可能となる。

【解決手段】プログラム実行装置120は、オブジェクトプログラムを実行する命令実行部220と、オブジェクトプログラムを一時的に保持するキャッシュメモリ222と、命令実行部によるオブジェクトプログラムのフェッチ要求を契機に、オブジェクトプログラムを読み込み、キャッシュメモリに保持させるプログラム読込部224と、読み込まれたオブジェクトプログラムに対し、順次、チェックコード導出式を計算し、ブロック単位でチェックコードを生成し、オブジェクトプログラムに予め挿入されているチェックコードと比較してオブジェクトプログラムの正否をブロック単位で判定するチェックコード判定部226とを備える。

(もっと読む)

携帯可能電子装置およびICカード

【課題】ハードウェアの誤動作などによるデータの誤書込みや誤読出しを未然に防止することができる携帯可能電子装置およびICカードを提供することである。

【解決手段】実施形態に係る携帯可能電子装置は、揮発性メモリおよび不揮発性メモリを備え、外部から入力される命令を解釈して所定の処理を実行し、その結果を外部へ出力する携帯可能電子装置において、命令を解釈して実行するプログラムのうち一部のプログラムを除く残りのプログラムは前記不揮発性メモリにあらかじめ格納され、かつ、前記一部のプログラムは前記不揮発性メモリの特定領域にあらかじめ格納されており、外部から命令が入力されると、前記不揮発性メモリの特定領域に格納されている一部のプログラムを前記揮発性メモリの特定領域に展開し、当該命令を解釈して実行するプログラムの実行中に前記揮発性メモリの特定領域に格納された一部のプログラムが参照あるいは呼び出される。

(もっと読む)

電子機器およびそのプログラム起動制御方法

【課題】不揮発性メモリからプログラムを読み出して電子機器を起動する場合の信頼性を向上させるプログラム起動制御方法および電子機器を提供する。

【解決手段】電子機器は、表示部12と、操作部13と、起動するための同一の起動用プログラムを格納した複数のNANDフラッシュメモリ102,103とを有し、メモリ102から読み出した第1起動用プログラムのデータ誤りを検出すると(S203;Y)、メモリ103から第2起動用プログラムを読み出し(S204)、第1起動用プログラムを第2起動用プログラムで書き換えるか否かの選択メッセージを表示部12に表示させ(S205)、操作部13を通して書き換えが選択されると(S206;Y,S207;Y)、書き換えを実行する(S208−S211)。

(もっと読む)

情報処理装置および情報処理方法

【課題】動作に重要なプログラムが書き込まれているフラッシュROM上の物理的な記憶領域のデータが不良になっている場合にもプログラムを実行できるようにする。

【解決手段】この情報処理装置は、複数のカラムを一単位とするブロック単位にデータを記憶可能な物理的な記憶領域を有するフラッシュメモリと、前記フラッシュメモリの物理的な記憶領域からデータを読み出し、読み出したデータのエラー箇所を、前記記憶領域の物理的な記憶位置から読み取った第1エラー訂正符号に基づいて第1のエラー訂正を行うことで修復する第1エラー訂正部と、前記第1エラー訂正手段によるエラー訂正の結果、前記エラー箇所が修復できなかった場合、前記フラッシュメモリから読み出した前記データに含まれる第2エラー訂正符号に基づいて第2のエラー訂正を行うことで前記エラー箇所を修復する第2エラー訂正部とを備える。

(もっと読む)

ファームウェア保護装置、そのプログラム

【課題】二重化したファームウェアの両方が破損してしまった場合でもリカバリすることができる。

【解決手段】二重化したファームウェアそれぞれについて、そのプログラム本体であるプログラム部50を、複数のプログラムブロック1〜n(51)に分割して記憶する。また、ヘッダ部40には各プログラムブロック51毎に対応するSUM45を記憶し、このSUM45を用いて各プログラムブロック51毎に破損したか否かをチェックする。二重化したファームウェアの両方が破損してしまった場合でも、一方において破損したプログラムブロック51が、他方においては破損していない場合には、他方のプログラムブロック51を用いてリカバリすることができる。

(もっと読む)

データチェック回路

【課題】適切なタイミングでプログラムデータのチェックを実行しつつ、CPUにチェック処理の以外の処理を実施させることが可能なデータチェック回路を提供する。

【解決手段】メモリにアクセスするためのバスにバスマスタとして接続されるCPUから、メモリに格納されたデータが正しいか否かの検出開始を指示する指示信号が出力されると、バスの占有を調停する調停回路に対してバスの占有を要求するための要求信号を出力する要求信号出力回路と、調停回路が要求信号に基づいてバスの占有を許可する許可信号を出力すると、バスを介してメモリに格納されたデータを取得するデータ取得回路と、データ取得回路が取得した取得データに対し、取得データが正しいか否かを検出するための処理を施すデータ処理回路と、を備えることを特徴とするデータチェック回路。

(もっと読む)

情報処理装置

【課題】不揮発性メモリのアクセス速度や装置への過負荷等といった性能面への影響を低減可能とする。

【解決手段】ブート実行手段320は、各種制御プログラム101i〜103iをロードエリア210にロードし、かつ照合用エリア220に対して制御プログラム101iのイメージ1010iをコピーする。照合復旧・前処理プログラム102iは、制御プログラム101iのイメージと照合用エリア220上の同イメージ1010iを照合する。一致する場合に制御プログラム101iを実行させる。相違がある場合に不揮発性メモリ100上の制御プログラム101iのイメージをロードエリア210に再ロードし、照合用エリア220上にコピーし、制御プログラム101iを実行させる。その後、照合復旧・後処理プログラム103iは、再度照合処理を実行し、一致する場合に照合復旧・前処理プログラム102i+1を実行させる。

(もっと読む)

メモリ制御装置及びメモリ制御プログラム

【課題】本構成を有さない場合に比べ、メモリに対する異常データの書込みに対処することができるメモリ制御装置及びメモリ制御プログラムを提供する。

【解決手段】生成した識別子をIDレジスタ32に設定し、データバス30に出力された合成データに含まれる識別子とIDレジスタ32に設定されている識別子が一致する場合は、比較回路34により出力された、LレベルのWE信号によりNVM20に書込データが書込まれ、記憶される。

(もっと読む)

セキュアメモリインターフェース

【課題】セキュアメモリインターフェースを提供すること。

【解決手段】セキュアメモリインターフェースは、セキュアモードが活性化された場合に、メモリ装置に対する欠陥注入を探知するように読出部、書込部、及びモード選択部を含む。モード選択部は、データプロセッシング部から生成されたメモリアクセス情報を使用してセキュアモードを活性化または非活性化する。従って、データプロセッシング部はメモリ装置に保存されたセキュアデータの量と位置を柔軟に指定することができる。

(もっと読む)

情報処理装置

【課題】情報処理装置においてエラーが生じた場合に、充分なエラー対応を行なうことができるようにする。

【解決手段】メモリ16においてエラーが生じた際に、複数のプロセッサ10のうちの一のプロセッサ10aが一のメモリ16aに格納されたエラー対処プログラム20aを実行し、一のプロセッサ10aがエラー対処プログラム20aを正常に動作させることができない場合に、他のプロセッサ10bが一のメモリ16aとは異なる他のメモリ16bに格納されたエラー対処プログラム20bを実行する。

(もっと読む)

情報処理装置、該装置用のROMイメージ生成装置、および転送装置

【課題】メインプログラムをNAND型フラッシュメモリに格納する情報処理装置において、ブートストラッププログラムをNOR型フラッシュメモリに格納すると、システムのコストが高くなる。

【解決手段】電源投入後、転送装置14は、第1の記憶装置11に格納された、第1の誤り検査符号114付きのブートストラッププログラム111を検出し、誤り検出/訂正処理を施して第2の記憶装置12に転送する。転送が正常に完了した場合、CPU10は、第2の記憶装置12上のブートストラッププログラム111を実行することにより、第2の誤り検査符号115付きのメインプログラム112に誤り検出/訂正処理を施して第3の記憶装置13に転送し、第3の記憶装置13上のメインプログラム112に分岐する。これにより、NOR型フラッシュメモリを使用せずに、システムブートを行える。

(もっと読む)

データの更新方法、メモリシステムおよびメモリデバイス

【課題】メモリデバイスに記憶されるデータを安全に更新できるデータの更新方法を提供する。

【解決手段】ホストデバイス2と接続可能なメモリデバイス1で、メモリ部5とメモリコントローラ6とを有し、メモリ部5が、複数の異なる属性を有するパーティションに分割可能である第1のメモリ部3と、メモリコントローラ6が管理するワークスペース4とからなるメモリデバイス1に記憶されるデータの更新方法であって、パーティションにデータを書き込むための複数の異なる書き込み方法の中から、パーティションの属性に応じて選択された一の書き込み方法を用いて更新処理を行う。

(もっと読む)

携帯端末の制御方法

【課題】ROMを有さない第1半導体チップに、第2半導体チップのROMから第1半導体チップ用のプログラムを転送した後、長期間、プログラムのベリファイを行なう機会が無いので、プログラムの信頼性が低下する。

【解決手段】電池の装着時など、携帯端末の使用を開始するときに、第2半導体チップのROMから第1半導体チップのRAMにプログラムの転送を行ない、その後、待ち受け状態において、着信の頻度に応じて決定されたベリファイ周期に基づいて、周期的に第1半導体チップのRAMに記憶されたプログラムのベリファイを実行する。

(もっと読む)

リカバリー制御装置、制御方法、プログラム及びコンピュータ読み取り可能な記憶媒体

【課題】フラッシュROMの破壊時、対応を待つ間のデッドタイムを短縮する。

【解決手段】フラッシュROM2を論理的に上位ビット領域と下位ビット領域に分割し、同一データとする。ROM2の最上位アドレス信号をスイッチSWで切り替えることで各領域を論理的に入れ換えることができる。CPU1にSWより反転・非反転選択信号BOOT_RESCUEを入力する。主電源ONによりブートが開始され、SWオフではROM2の最上位アドレス信号A21は非反転で、上位ビット領域よりブートが開始される。SWオンではA21が反転されて下位ビット領域よりブートが開始される。CPU1はBOOT_RESCUEが1であれば、通常のシステム起動処理を実行する。BOOT_RESCUEが0であれば、ROM2に問題が発生したのでSWを操作する。この場合は下位ビット領域のデータを上位ビット領域に全てコピーして上位ビット領域を修復する。

(もっと読む)

1 - 20 / 42

[ Back to top ]