Fターム[5B035AA02]の内容

デジタルマーク記録担体 (44,834) | 目的 (6,784) | 高速化 (297)

Fターム[5B035AA02]に分類される特許

201 - 220 / 297

通信媒体、通信媒体処理装置、及び通信媒体処理システム

【課題】通信処理時間の短縮を図ることが可能な通信媒体を提供すること。

【解決手段】通信媒体処理装置からのリードコマンドに対応してリードデータを送信し、また前記通信媒体処理装置からのライトコマンドに対応して送信されるライトデータを記憶する通信媒体は、データを記憶する記憶手段と、前記記憶手段に記憶されたデータを所定データ単位に分割し、この分割により得られる各分割データに対してチェックコードを付与して、チェックコード付き分割データを複数含む送信データを生成する送信データ生成手段と、前記送信データ生成手段により生成された前記送信データを前記通信媒体処理装置に対して送信する通信手段とを備えている。

(もっと読む)

携帯可能電子装置

【課題】データ処理時間の短縮を図ることが可能なICカードを提供することにある。

【解決手段】携帯可能電子装置は、nビット列中の第m1番目のビットにより第1のアクセス条件を示す第1のアクセス情報、及びnビット列中の第m2番目のビットにより第2のアクセス条件を示す第2のアクセス情報を記憶する第1の記憶手段と、nビット列中の第m1番目のビットによりランクm1を有する第1のキー、及びnビット列中の第m1番目と第m2番目のビットによりランクm1とランクm2を有する第2のキーを記憶する第2の記憶手段と、照合又は認証に必要な情報を取得する取得手段と、前記取得手段により取得された照合又は認証に必要な情報に基づき、前記第2のキーの照合又は認証の正常終了が得られることにより、前記第1及び第2のアクセス条件満足を判定し、判定結果に基づき動作を制御する制御手段とを備えている。

(もっと読む)

ICタグ、ICタグシステムおよびそのデータの通信方法

【課題】 近年の大量物流により、リーダ・ライタがICタグを識別処理するスピード、すなわち、R/WとICタグとの間の通信速度を向上させることが重要となってきた。

【解決手段】

本発明に係るICタグは、受信する無線信号に含まれるデータ信号に基づいて検波信号を生成する受信回路と、送信データを送信する送信回路と、を備え、検波信号に基づいて生成された基準クロックに同期して動作するICタグであって、送信回路は、検波信号に同期して送信データの送信を行う、ことを特徴とする。

(もっと読む)

半導体記憶装置の制御方法

【課題】処理効率を向上出来る半導体記憶装置の制御方法を提供すること。

【解決手段】複数ビットを保持するメモリセルを備えた半導体記憶装置3が第1レディ状態になったことを受けて制御装置2が第1信号処理を開始し、下位ビットデータが前記半導体記憶装置3に入力、書き込まれるステップS11〜S13と、前記半導体記憶装置3が第1ビジー状態となるステップS14と、遅くとも前記書き込みが終了した時点で前記半導体記憶装置3が第2レディ状態となり、前記第1信号処理が終了するステップS16、S17と、前記半導体記憶装置3が前記第2レディ状態になったことを受けて第2信号処理を開始し、上位ビットデータが前記半導体記憶装置に入力、書き込まれるステップS18〜S20とを具備し、前記上位ビットの書き込みと第2信号処理に要する期間Δt1は前記下位ビットの書き込みと第1信号処理に要する期間Δt2よりも長い。

(もっと読む)

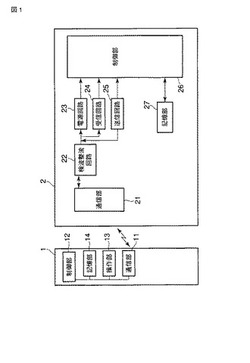

複合携帯可能電子装置および複合ICカード

【課題】たとえば、セキュリティ性の高いデータを付加して送信されるコマンドは接触式インタフェイスにて確実に送信することができ、また、大容量のデータを含むコマンドは非接触式インタフェイスにて高速伝送により送信することができる複合携帯可能電子装置を提供する。

【解決手段】接触式、非接触式インタフェイスをそれぞれ有し、これら接触式インタフェイスあるいは非接触式インタフェイスにより、接触式インタフェイスおよび非接触式インタフェイスをそれぞれ有するカードリーダ・ライタと通信を行なう複合ICカードにおいて、カードリーダ・ライタからのコマンドを非接触式インタフェイスで受信し、当該コマンドに対するレスポンスを接触式インタフェイスでカードリーダ・ライタへ送信し、あるいは、カードリーダ・ライタからのコマンドを接触式インタフェイスで受信し、当該コマンドに対するレスポンスは非接触式インタフェイスでカードリーダ・ライタへ送信する。

(もっと読む)

半導体装置の作製方法

【課題】レーザ照射パターンを切り替えながら、所望の位置に高速にレーザ照射を行う方法を用いた半導体装置の作製方法を提供する。

【解決手段】一対の導電層に有機化合物層が挟まれた構造を有する有機メモリ素子において、該有機メモリ素子へのデータの書き込みをレーザ照射装置を用いたレーザ照射により行う。また、レーザ発振器から射出したレーザビームは、回折光学素子により複数に分岐され、一度の照射で該有機化合物層上の複数箇所にレーザビームを照射される。

(もっと読む)

メモリコントローラ、不揮発性記憶装置、不揮発性記憶システム、及びデータ書き込み方法

【課題】実装するフラッシュメモリの種類に対応して書き込み速度とピーク電流抑制とを最適化することのできるメモリコントローラ、不揮発性記憶装置、不揮発性記憶システムを提供すること。

【解決手段】論物変換モード決定手段125が、実装された不揮発性メモリ130や140の種類に応じて論物変換手段126の論物変換モードを決定する。これにより、不揮発性メモリ130や140に対してデータを並列的に書き込むか、あるいは、いずれか一方の不揮発性メモリに直列的に書き込むかを選択する。不揮発性メモリ130、140が低速タイプの場合には不揮発性メモリ130と140に同時に書き込み、高速タイプの場合にはいずれかの不揮発性メモリに直列的に書き込むようにしたので、目標書き込み速度を維持しつつピーク電流を抑制することができる。

(もっと読む)

半導体集積回路装置のデータ記録方式

【課題】 大規模な記録容量とともに、高速なデータ書き込み、並びにデータ読み出しを実現する不揮発性半導体メモリを有した半導体集積回路装置のデータ記録方式を提供する。

【解決手段】 二値領域55と多値領域57とを含むメモリ領域51を備え、ホスト機器が送信したデータ(DATA1〜DATA3)を、二値領域55に二値データで記録し、二値領域55に記録したデータ(DATA1〜DATA3)を、ホスト機器からのアクセスが無いときに多値領域57に多値データでコピーする。

(もっと読む)

情報記録媒体とそのプログラム、及び、情報処理装置

【課題】不揮発性メモリに対して柔軟かつ迅速に処理を行うことができる情報記録媒体とそのプログラム、及び、情報処理装置を提供する。

【解決手段】ICカード(情報記録媒体)は、不揮発性メモリ15と処理実行手段などとを備える。不揮発性メモリ15は、複数の領域に分割されてブロック化されており、分割された各分割領域には、その各分割領域を識別するための割付情報15aが割り付けられている。割付情報15aは、領域識別子15bと、ブロック識別子15cとによって構成され、領域識別子15bは、分類情報としての「1、2、3」などであり、ブロック識別子15cは、各分割領域の先頭アドレス(0000番地、0800番地など)である。処理実行手段は、割付情報15aに基づいて、不揮発性メモリ15のメモリ検査を行う。

(もっと読む)

ICカード用LSIおよびメモリデータ転送方法

【課題】LSIの処理速度の向上および消費電力の削減を図るために、CPUの外部バスに接続されたメモリ間でのデータ転送における処理速度の向上を図る。

【解決手段】ROM13に格納されているプログラムにより、ハードウェア部15にあるレジスタ領域29の読み出しメモリ先頭アドレス設定レジスタ31、書き込みメモリ先頭アドレス設定レジスタ32、転送データバイト数設定レジスタ33に各値を設定し、プログラムがデータ転送開始信号34をイネーブルにすると、ハードウェア部15はレジスタにセットされたメモリ先頭アドレス及びデータバイト数をもとに、外部バス21に接続された各メモリを制御し、メモリ間でのデータ転送を所定の処理クロック数で処理することから、処理速度の向上を図ることができる。

(もっと読む)

バーコード及び撮像装置

【課題】無駄なデコード時間の発生を抑制することのできるバーコード及び撮像装置を得る。

【解決手段】2次元コード60に対し、予め定められた第1記録密度で実データがコード化されて記録された実データ領域60Bと、前記第1記録密度より低い第2記録密度で前記実データが何を示す情報なのかを特定することのできるインデックス情報がコード化されて記録されたインデックス領域60Aと、を設ける。そして、デジタルカメラでは、インデックス領域60Aに対応する情報をデコードして、これによって得られたインデックス情報に基づいて2次元コード60が読み取り対象とするバーコードであるか否かを判定し、読み取り対象とするバーコードであると判定した場合のみに実データ領域60Bに対応する情報をデコードする。

(もっと読む)

情報処理装置

【課題】より適切な動作モードを選択することのできる情報処理装置を提供する。

【解決手段】本発明に係る情報処理装置は、カード型媒体が挿入されるカードスロットと、第1の動作モードで前記カード型媒体とデータのやり取りを行う場合の通信速度である第1通信速度を取得する、第1通信速度取得手段と、第2の動作モードで前記カード型媒体とデータのやり取りを行う場合の通信速度である第2通信速度を取得する、第2通信速度取得手段と、前記第1通信速度と前記第2通信速度のうち、どちらが速いかを判断する、判断手段と、前記第1の動作モードと前記第2の動作モードのうち、前記判断手段で速いと判断された通信速度の動作モードで、前記カード型媒体とデータのやり取りをする、データ通信手段と、を備えて構成されている。

(もっと読む)

RFIDタグを媒介としたR/W間通信プロトコル

【課題】質問器に対して制御情報などを送る場合には、制御装置や専用の接続線を介して行っていたため、RFタグシステムが冗長的な構成となってしまうという課題がある。

【解決手段】非接触タグと、非接触タグと通信可能な複数の質問器からなるRFタグシステムを提供する。一の質問器は、非接触タグのメモリに情報を記憶し、その記憶した情報を他の質問器が取得することによって、質問器間の通信を間接的に実現することができ、冗長的なホスト装置や接続線などを排除することができる。また、質問器間通信を間接的に実現することで、RFタグシステムの通信領域を拡大することができる。

(もっと読む)

多段階誤り訂正方法及び装置

【課題】例えば、フラッシュおよびEEPROM・NVMモジュールの両方からなる大容量SIMカード等の、データ処理システムの性能および耐久性を向上させるためのシステムおよび方法を提供する。

【解決手段】(a)ユーザ・データを記憶するための第一のNVM、そして(b)ユーザ・データに関連する管理データを記憶するための、第一のNVMから分離した第二のNVMを含むSIMカード。第一のNVMはブロック消去可能であること、そして第二のNVMはワード消去可能であることが好ましい。第一のNVMはフラッシュメモリであること、そして第二のNVMはEEPROMであることが好ましい。管理データは、第一のNVMの仮想アドレスを物理デバイス・アドレスへマップするためのマッピング・テーブルを含むことが好ましい。ユーザ・データおよび管理データは、ファイル・システム内で編成されることが好ましい。管理データは、少なくとも一つのファイル・アロケーション・テーブルを含むことが最も好ましい。管理データは、少なくとも一つのファイル・ディレクトリを含むことが最も好ましい。この場合、少なくとも一つのファイル・ディレクトリは、ファイル名、ファイル・サイズ、ファイル属性およびファイル・セクターの物理アドレスからなるグループから選択される少なくとも一つのアイテムを含む。

(もっと読む)

半導体装置

【課題】大規模な演算回路を有する半導体装置において、クロック信号に遅延があると、回路は誤動作する。特に、無線チップのように、電源電圧が変動する環境下では、クロック信号の遅延を設計時に精密に見積もることは非常に困難である。また、電源電圧を一定に保つには、大規模な電源回路が必要で、チップ面積大、高価格化などを招いてしまう。

【解決手段】電源検管理回路と、クロック生成回路と、を搭載した半導体装置により、電源電圧の変動を電源管理回路で検出し、クロック生成回路でクロック信号の周波数と、デューティー比とを変更することで、演算回路を安定して動作させる。このような大規模な演算回路を搭載した高性能の半導体装置を安価に提供することができる。

(もっと読む)

ICカードシステム

【課題】装置が大型化するのを抑え、かつ、データ転送時間の短縮、単位時間当りのデータ転送量の増大化をはかる。

【解決手段】リード/ライト装置100を介して、ICカード200にデータを書き込み、また、このICカード200の記憶データを読み出す。これらの間のデータの授受は、コイルを用いた搬送波の電磁結合で行い、かつこの搬送波に対し、授受されるデータの各ビットの値に従って、このデータの配列順に交互に、周波数変調と振幅変調とを繰り返し行うようにする。

(もっと読む)

通信媒体及び通信媒体処理装置

【課題】通信処理時間の短縮を図ることが可能な通信媒体を提供すること。

【解決手段】通信媒体は、外部機器と通信しデータを送受信する通信手段と、前記通信手段を介して送受信されるデータを記憶する記憶手段と、第1の動作状態の認識に基づき第1のデータサイズを上限としたデータの送受信を制御し、第2の動作状態の認識に基づき前記第1のデータサイズより大きい第2のデータサイズを上限としたデータの送受信を制御する制御手段とを備えている。

(もっと読む)

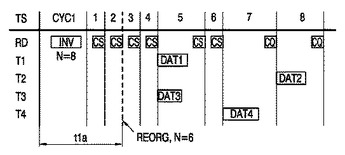

リーダを介してトランスポンダからデータを読み取る方法、トランスポンダ、及びリーダ

リーダ装置(RD)によって複数のタイムスロット(TS)の間にトランスポンダ(T1〜T4)からデータ(DAT1〜DAT4)を読み取る方法を開示しており、ここでは、前記リーダ装置(RD)及び前記トランスポンダ(T1〜T4)双方において前記タイムスロット(TS)の占用を観察している。再編成(REORG)を前記占用に応じて実行し、前記リーダ装置(RD)及び前記トランスポンダ(T1〜T4)双方は新しいタイムスロット(TS)の数(N)を選ぶ。さらに、前記トランスポンダ(T1〜T4)は、実際の要求にシステムの容量を適合させるように、前記リーダ装置(RD)にデータ(DAT1〜DAT4)を送信するための、新しいタイムスロット(TS)の1つを選ぶ。前記再編成(REORG)は、前記リーダ装置(RD)及び前記トランスポンダ(T1〜T4)の間の通信なしで行うことが望ましい。本発明は、さらに、本発明に係る方法を実行するためのトランスポンダ(T1〜T4)及びリーダ装置(RD)に関する。  (もっと読む)

(もっと読む)

メモリシステム

【課題】異なる消去ブロックサイズを想定したメモリへのアクセスに対して柔軟に対応できるようにする。

【解決手段】メモリカード1は、コントローラ4とNAND型フラッシュメモリ3とを有する。コントローラ4は、第1の消去ブロックサイズを有する半導体メモリにおける第1のアドレスと前記第1の消去ブロックサイズよりも大きい第2の消去ブロックサイズを有する半導体メモリにおける第2のアドレスとの対応付けを管理するためのプログラムを格納するROM9と、このROM9に格納されているプログラムを実行するCPU8とを含んでいる。NAND型フラッシュメモリ3は、前記第2の消去ブロックサイズを有するメモリである。コントローラ4は、前記第2のアドレスを用いてNAND型フラッシュメモリ3に対するアクセスを実行する。

(もっと読む)

携帯可能電子装置およびICカード

【課題】メモリから入れ子構造のデータを読出す際、当該データ内に無効なデータを含む場合はそのデータを省き、有効なデータのみを出力データとすることができ、通信を含めた処理時間の短縮が図れる携帯可能電子装置およびICカードを提供する。

【解決手段】外部から供給される命令データに基づいて各種処理を実行するICカードにおいて、メモリから入れ子構造のデータを読出す際、識別子が当該データが無効を示す特定の値(「00」)であるか否かをチェックし、識別子が特定の値である場合は当該データが無効データであると判断してそのデータを省き、有効なデータのみを出力データとする。

(もっと読む)

201 - 220 / 297

[ Back to top ]