Fターム[5B045DD01]の内容

マルチプロセッサ (2,696) | メモリシステム、ファイル管理 (299) | 共有メモリ、専用メモリ (190)

Fターム[5B045DD01]の下位に属するFターム

領域管理 (78)

Fターム[5B045DD01]に分類される特許

1 - 20 / 112

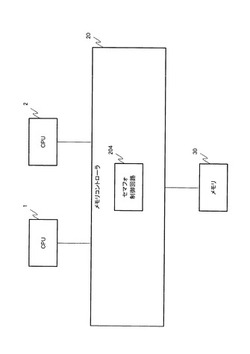

マルチプロセッサシステム、及びマルチプロセッサシステムの制御方法

【課題】各CPU(プロセッサ)の処理負荷を軽減し、セマフォの使用効率を向上させたマルチプロセッサシステム、マルチプロセッサシステムの制御方法を提供すること

【解決手段】メモリ30は、CPU1及びCPU2からアクセスされる。セマフォ制御回路204は、CPU1、CPU2からメモリ30へのロック命令、アンロック命令を受信して、メモリ30の同期制御を行う。詳細には、セマフォ制御回路204は、ロックを行ったプロセッサがロック処理を行っている時間(ロック処理時間)をカウントする。また、セマフォ制御回路204は、ロック中にロック命令を送信したプロセッサの命令送信順序を保持し、算出済みのロック処理時間と、命令送信順序を基に、ロックに失敗した各プロセッサの待ち時間を算出して通知する。

(もっと読む)

画像音声信号処理装置及びそれを用いた電子機器

【課題】 MPEG−4 AVCの符号化/復号処理のような、大量のデータ処理量が要求される画像処理に対して、高性能で、高効率な画像処理が行える信号処理装置及びそれを用いた電子機器を提供する。

【解決手段】 信号処理装置は、命令並列プロセッサ100、第1データ並列プロセッサ101、第2データ並列プロセッサ102、及び、専用ハードウェアである動き検出ユニット103とデブロックフィルタ処理ユニット104と可変長符号化/復号処理ユニット105とを備える。この構成により、処理量の多い画像圧縮伸張アルゴリズムの信号処理において、ソフトウェアとハードウェアで負荷が分散され高い処理能力と柔軟性を実現した信号処理装置、及びそれを用いた電子機器を提供出来る。

(もっと読む)

分散共有メモリ管理システム、分散共有メモリ管理方法、および分散共有メモリ管理プログラム

【課題】メモリを共有する異なるノードにおけるメモリ資源・通信資源の使用効率を高める。

【解決手段】固有メモリに格納されたデータ値を更新し、更新された値が予め設定された共通初期値と異なる場合に更新された値と該値の固有メモリにおけるアドレスを送出する計算ノードと、共有メモリに格納されたデータを共通初期値で初期化するデータ初期化機能と、計算ノードから更新データが送り込まれた場合に前記更新データに基づき前記共有メモリにおける対応するアドレスのデータを前記更新値へと更新する共有メモリデータ更新機能を有するメモリ管理装置を備える。

(もっと読む)

マルチプロセッサおよびそれを用いた画像処理システム

【課題】データの共有やデータ転送のバッファリングを容易に行なうことが可能なマルチプロセッサを提供すること。

【解決手段】複数の共有ローカルメモリ5−0〜5−(n−1)のそれぞれが、複数のプロセッサユニットPU0〜PU(n−1)(1−0〜1−(n−1))の中の2つのプロセッサに接続されており、複数のプロセッサユニットPU0〜PU(n−1)(1−0〜1−(n−1))と複数の共有ローカルメモリ5−0〜5−(n−1)とがリング状に接続される。したがって、データの共有やデータ転送のバッファリングを容易に行なうことが可能となる。

(もっと読む)

マイコン、処理同期方法

【課題】一方のコアから他方のコアに割込みによりイベントを通知する際、イベントの誤通知を検知できるマイコンを提供すること。

【解決手段】第1のコア52と第2のコア53間で通信する通信手段43と、第1のコアと第2のコアが共有する共有メモリ51と、外部信号を取得して第1の処理を実行し、第1の処理毎に所定情報を共有メモリに書き込む第1の処理手段55と、通信手段を介して第2のコアに処理要求を出力する処理要求手段33と、処理要求をトリガーに第2の処理を実行する第2の処理手段56と、を有するマイコン100において、第2のコアは、処理要求を受け付けた場合、共有メモリから最新の所定情報と前回の所定情報を読み出し、最新の所定情報と前回の所定情報に規定された関係がある場合のみ、第2の処理手段に第2の処理の実行を許可する比較手段57、を有する。

(もっと読む)

電子機器

【課題】複数のCPU間で効率よくデータ授受を行うことができる電子機器を提供すること。

【解決手段】共有メモリを介して複数のCPU間でデータの授受を行うように構成された電子機器において、前記共有メモリには、

前記授受されるデータを格納する唯一のFIFOと、前記FIFOのデータ格納位置情報とデータ取り出し位置情報と作業情報としてのデータ取り出し位置情報を含むFIFOの管理情報を格納するFIFO管理情報格納部と、前記データの処理を即座に実行できないときに当該データ処理を保留にするための保留要求管理情報を格納する保留要求管理情報格納部が設けられていることを特徴とするもの。

(もっと読む)

マルチコア・プロセッサ

【課題】共有アクセス対象へのアクセスに関する調停を確実に行うことが可能なマルチコア・プロセッサを提供すること。

【解決手段】複数のプロセッサコアによって読み書き可能なメモリ上に、特定の共有アクセス対象に対するアクセスの内容及び順序を規定するためのメッセージキューが設定され、複数のプロセッサコアは、メッセージキューに対する所定の書き込み制御に応じて自己が実行すべきタスクに含まれる処理のうち特定の共有アクセス対象に対するアクセスを含む処理に関するジョブ情報を排他的にメッセージキューに書き込み、複数のプロセッサコアのうち少なくとも一の特定対象アクセス実行用プロセッサコアは、メッセージキューに書き込まれたジョブ情報に従って特定の共有アクセス対象に対するアクセスを含む処理を実行することを特徴とする、マルチコア・プロセッサ。

(もっと読む)

信号制御装置及び信号制御方法

【課題】2つのCPUがデュアルポートRAMに同じタイミングで読出し又は書込みを行う場合に、データ信号を正しく読出すこと。

【解決手段】信号制御装置4は、第1及び第2のCPUがデュアルポートRAM5に書き込むアドレスの衝突を検出するアドレス衝突検出部14を備える。また、アドレスの衝突が検出された場合に、デュアルポートRAM5に書込みを行う第1又は第2のCPUのいずれかに設けられたバッファメモリに、衝突したアドレスから読出したデータ信号を保存する制御を行う制御部13を備える。また、第1及び第2のCPUの読出し可能状態又は書込み可能状態に応じて、データ信号の読出し元であるレジスタ又はバッファメモリを切替えて、読出し可能状態となるCPUに読出した前記データ信号を出力するマルチプレクサ15a,15bを備える。

(もっと読む)

データプロセッサ

【課題】プロセッサコアのローカルメモリや共有メモリの所要のアドレスに対して小さな回路規模で排他制御を行うことができるデータプロセッサを提供する。

【解決手段】要求に従ってバスロック設定と解除が可能にされるシステムバス(5)を共有する複数個のプロセッサコア(20,40)が相互に互いの内部リソース(22,42)を共有するデータプロセッサ(1)において、プロセッサコアが内部リソースの第1アドレス(ロック変数割り当てアドレス)へアクセスを行うときバスロックの要求を伴って当該アクセス要求をシステムバスに出力することによりシステムバスにバスをロックさせると共にシステムバスから当該プロセッサコアに帰還されるのを待って当該アクセス要求を処理し、プロセッサコアが内部の第2アドレスへアクセスを行うとき当該アクセス要求をプロセッサコアの内部で処理する。

(もっと読む)

マルチプロセッサシステムおよびマルチプロセッサシステムのプログラム

【課題】 マルチプロセッサシステムの計算処理の効率を向上させる。

【解決手段】 マルチプロセッサシステムは、第1メモリと、第1メモリに接続され、第1メモリに記憶されたデータを用いて処理を実施する処理部とを有している。処理部は、第2メモリと、データおよび処理の結果である処理データの少なくとも一方を第1メモリと第2メモリとの間で転送するデータ転送を実施する第1プロセッサと、第1メモリと第2メモリとの間でのデータ転送と処理とを切り替え可能に実施する第2プロセッサと、第2メモリに転送されたデータを用いて、処理を実施する第3プロセッサとを有している。

(もっと読む)

SIMDベクトルの同期

プロセッシングデバイス内のデコーダによって、第1記憶ロケーション、第2記憶ロケーション及び第3記憶ロケーションの間の複数のデータ要素に対するベクトル比較/交換オペレーションを規定する単一命令をデコードする段階と、プロセッシングデバイス内の実行ユニットによって実行するために、単一命令を発行する段階と、単一命令の実行に応答して、第1記憶ロケーションからのデータ要素と、第2記憶ロケーションにおける対応するデータ要素とを比較する段階と、一致が存在するかに応じて、第1記憶ロケーションからのデータ要素を、第3記憶ロケーションからの対応するデータ要素で置き換える段階とを実行することによって、ベクトル比較/交換オペレーションが実行される。 (もっと読む)

並列信号処理装置

【課題】データ転送におけるレイテンシーの遅れや、データ転送機構以外の回路の増大を伴うことなく、演算器の並列度を高めても、急激な回路規模の増大を抑えることができるようにする。

【解決手段】演算器1−1〜1−nが、自己が接続されているローカル共有バス2に接続されている共有メモリ3から隣接している他の演算器1の演算結果を読み出して、その演算結果に対する所定の演算処理を実施し、その演算処理の演算結果を上記ローカル共有バス2に接続されている上記共有メモリ3以外の共有メモリ3に書き込むように構成する。

(もっと読む)

マルチコアシステム

【課題】プロセッサ間ネットワークの特定のルータに負荷が集中することを軽減したマルチコアシステムを提供する。

【解決手段】プロセッサ間ネットワーク11は、各プロセッサエレメントPE0〜PE9から発せられたアクセス及び各プロセッサエレメントPE0〜PE9宛のデータを中継する複数のルータR00〜R23と、各プロセッサエレメントPE0〜PE9からのリードアクセスに応じて、アクセス対象のデータを要求元のプロセッサエレメント宛に送信する共有キャッシュメモリ12と、を備え、各ルータR00〜R23は、他のルータ又はプロセッサエレメントへ転送したデータを保持するルータ内キャッシュ機構C00〜C23と、リードアクセスが転送されてきた際にアクセス対象のデータをルータ内キャッシュ機構C00〜C23に保持している場合には、当該データを読み出して要求元のプロセッサエレメント宛に送信する手段と、を備える。

(もっと読む)

データ処理装置及びそのデータ処理方法

【課題】

リングバスに接続された複数の処理モジュールにより各種処理を実行する構成において、アクセス遅延を起因とした処理速度の低下がある。

【解決手段】

データ処理装置は、リング状に接続され、所定の順番に従ってデータを処理する複数のモジュールと、データの処理に用いるパラメータを格納する共有メモリとを有する。ここで、モジュールは、共有メモリから取得したパラメータを格納する格納手段と、他のモジュールから受信したデータが自モジュールで処理すべきデータであるか否かを識別する識別手段と、識別手段により自モジュールで処理すべきと識別されたデータの処理に必要なパラメータが格納手段に格納されていない場合、共有メモリに対してパラメータの取得を要求する要求手段と、要求手段により共有メモリに要求したパラメータを必要とするデータを他のモジュールへ送信する送信手段と、当該パラメータを用いてデータを処理する処理手段とを具備する。

(もっと読む)

複数メモリ特定用途向けデジタル信号プロセッサ

回路基板(210)と、この回路基板上に実装された1又はそれ以上のデジタル信号プロセッサ(100)とを含む集積回路装置(200)を提供する。デジタル信号プロセッサ(100)は、データユニット(120)及び制御ユニット(110)を含み、データユニットは、特定のアプリケーションの少なくとも一部を実行するために特定の数式を実行するように構成された関数コア(124)と、特定のアプリケーションを実行するためのコマンドを制御ユニット及びデータユニットに送信するように構成された1又はそれ以上の命令を記憶する命令メモリ(122)とを含み、制御ユニットは、複数のメモリバンク(130、140)と関数コアの間の、特定のアプリケーションを実行するためのデータの流れを制御するように構成され、複数のメモリバンクは、1又はそれ以上のデジタル信号プロセッサの各々に結合されるとともに、回路基板上に統合された少なくとも2又はそれ以上のローカルメモリバンク(130)を含む。 (もっと読む)

情報処理システム

【課題】データ転送時に発生するデータの書き込み完了通知及びデータの読み出し完了通知を抑制する。

【解決手段】情報処理システム90には、情報処理装置1、情報処理装置2、及び共有部3が設けられる。情報処理システム90では、情報処理装置1及び情報処理装置2の間の共有部3に設けられる共有メモリ31を介して、情報処理装置1と報処理装置2の間のデータ転送を行っている。連続したデータ転送の場合、データ転送が終了後或いは所定回数のデータ転送が終了後に転送データの完了通知が送信される。

(もっと読む)

アトミックなセマフォ操作を行う方法および装置

【課題】処理システムと、処理システム内で通信する方法において、セマフォへのアトミックなアクセスを、バスプロトコルの枠組み内で、追加のハードウェアを最少にして、性能を劣化することなく、実施する技術を提供する。

【解決手段】処理システムは、バスと、バスに連結されたメモリ領域と、バス上でメモリ領域へアクセスする複数の処理構成要素とを含み、各処理構成要素が、セマフォ操作を行って、バス上でのセマフォ位置への読み出し動作および書き込み動作を同時に要求することによって、メモリ領域へのアクセスを得るように構成される。

(もっと読む)

画像形成装置

【課題】画像形成装置において、不揮発性メモリを2つのCPUで共有させると共に、2つのCPUから不揮発性メモリへのアクセスを簡単な回路で調整できるようにする。

【解決手段】画像形成プロセス制御を行う第1CPU1と、通信制御を行う第2CPU2と、第1CPU1及び第2CPU2で共有するEEPROM4と、第1CPU1及び第2CPU2の一方を不揮発性メモリ4に直接アクセス可能とするセレクタ3とを設ける。そして、第1CPU1と第2CPU2との間で通信可能とし、通常状態では、第1CPU1がEEPROM4に直接アクセス可能とするとともに、第2CPU2は、第1CPU1を介してEEPROM4にアクセス可能とする。一方、第1CPU1が作動を停止した省電力状態又は第1CPU1が動作異常状態では、セレクタ3によって第2CPUがEEPROM4に直接アクセス可能となるようする。

(もっと読む)

車載用情報処理装置、及び車両制御装置

【課題】車載された複数EUC間での機能連携のためのデータを、各ECUが保持する車両制御用のアプリケーションが使用するよりも事前に共有できる車載用情報処理装置を提供する。

【解決手段】車載用情報処理装置100は、他のECUとの機能連携に関連するタグデータが付与されたデータを記憶する機能連携タグ付データ記憶部101と、車両の状況情報に応じて機能連携タグ付きデータ記憶部101に記憶されているタグデータを参照して、他のECUとの機能連携用のプログラムの実行局面を特定する機能連携メモリ制御部103aと、機能連携メモリ制御部103aにおいて機能連携の実行局面と特定された場合、他のECUとの機能連携をするため機能連携用OSを起動すると共に、機能連携のため送受信される機能連携用パケットデータを生成する機能連携OS制御部102と、機能連携用パケットデータを送受信する機能連携パケット送受信部103bとを備える。

(もっと読む)

動的サブネットワークを備えた相互接続ネットワーク

【課題】多数の並列接続を同時に生成するための新規な相互接続ネットワークアーキテクチャを提供すること。

【解決手段】m個の第1電子回路(102)及びn個の第2電子回路(106)との相互接続ネットワークであって、m個の相互接続サブネットワークを備え、それぞれは、m個の第1回路の一つをn個の第2回路の全てに接続するアドレスバス及び情報伝送バスであって、リピートデバイスを通して相互に接続された複数の電気的導通配線セグメント(112a,112b)を備えたバスと、アドレス信号の値に基づきリピータデバイスの一つを活性化する機能を有し、リピータデバイスを制御するための手段であって、活性化リピータデバイスが、m個の第1回路の一つとn個の第2回路の一つとの間又は複数のn個の第2回路の間のデータ信号のための情報伝送バスにおける通信経路を形成する手段とを備える。m及びnは1よりも大きい整数である。

(もっと読む)

1 - 20 / 112

[ Back to top ]