Fターム[5B045EE00]の内容

マルチプロセッサ (2,696) | 競合処理、占有制御 (237)

Fターム[5B045EE00]の下位に属するFターム

Fターム[5B045EE00]に分類される特許

1 - 4 / 4

情報処理方法、装置及びプログラム

【課題】マルチパスネットワークにおけるリンク競合を回避する。

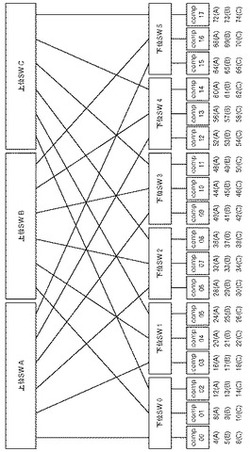

【解決手段】多段マルチパスネットワークにおける最下層の中継装置に接続された複数のコンピュータのうち並列プロセスを起動するように選択されたコンピュータである選択コンピュータの識別子を含む第1のデータを取得し、複数のコンピュータに含まれる各コンピュータの識別子に予め対応付けられており且つルーティングに用いられる、ネットワークにおける通信経路毎のネットワーク識別子から、選択コンピュータを順序づけるための識別番号間の差が等しい選択コンピュータ間の通信経路の重複を避けるように、第1のデータにおいて識別子が含まれる選択コンピュータ毎に、他の選択コンピュータとの通信で用いるべきネットワーク識別子を選択する。

(もっと読む)

信号制御装置及び信号制御方法

【課題】2つのCPUがデュアルポートRAMに同じタイミングで読出し又は書込みを行う場合に、データ信号を正しく読出すこと。

【解決手段】信号制御装置4は、第1及び第2のCPUがデュアルポートRAM5に書き込むアドレスの衝突を検出するアドレス衝突検出部14を備える。また、アドレスの衝突が検出された場合に、デュアルポートRAM5に書込みを行う第1又は第2のCPUのいずれかに設けられたバッファメモリに、衝突したアドレスから読出したデータ信号を保存する制御を行う制御部13を備える。また、第1及び第2のCPUの読出し可能状態又は書込み可能状態に応じて、データ信号の読出し元であるレジスタ又はバッファメモリを切替えて、読出し可能状態となるCPUに読出した前記データ信号を出力するマルチプレクサ15a,15bを備える。

(もっと読む)

CPUシステム、バスブリッジ、その制御方法、及びコンピュータシステム

【課題】 複数のCPUでもって同一のアクセス対象に対してアクセスを行う場合に、不具合なくセマフォの獲得に係る排他制御処理を行う為の技術を提供すること。

【解決手段】 バスブリッジ部103は、CPU101からセマフォの獲得要求を受けた場合には、バスブリッジ部104から受信したsemi_out信号と、信号線112を介して受けた優先度に応じて、セマフォの獲得を制御する。

(もっと読む)

ネットワークシステム、そのノード

【課題】 排他を行わない共有メモリ使用方法を提供する。

【解決手段】 インタフェースメモリ12において、ネットワークコントロール部11がデータ書込みし、ホストマイコンがデータ読出す記憶領域である共有データバンク領域21を2データバンク構成とし、バンク管理情報22により管理する。バンク管理情報22は、ネットワークに接続された各局毎に1bit割り当てられ、bit0の場合はデータバンクAがホスト向け、bit1の場合はデータバンクBがホスト向けであることを意味し、ネットワークコントロール部11はホスト向けではないデータバンクにデータを書き込み、ホストマイコン13はホスト向けのデータバンクからデータを読み出す。送信データバンク領域についても略同様である。

(もっと読む)

1 - 4 / 4

[ Back to top ]