Fターム[5B045EE19]の内容

マルチプロセッサ (2,696) | 競合処理、占有制御 (237) | 競合処理方式 (107) | フラグ、識別子によるもの (17) | テストアンドセット方式 (3)

Fターム[5B045EE19]に分類される特許

1 - 3 / 3

マルチプロセッサシステム、及びマルチプロセッサシステムの制御方法

【課題】各CPU(プロセッサ)の処理負荷を軽減し、セマフォの使用効率を向上させたマルチプロセッサシステム、マルチプロセッサシステムの制御方法を提供すること

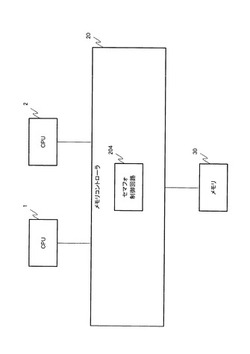

【解決手段】メモリ30は、CPU1及びCPU2からアクセスされる。セマフォ制御回路204は、CPU1、CPU2からメモリ30へのロック命令、アンロック命令を受信して、メモリ30の同期制御を行う。詳細には、セマフォ制御回路204は、ロックを行ったプロセッサがロック処理を行っている時間(ロック処理時間)をカウントする。また、セマフォ制御回路204は、ロック中にロック命令を送信したプロセッサの命令送信順序を保持し、算出済みのロック処理時間と、命令送信順序を基に、ロックに失敗した各プロセッサの待ち時間を算出して通知する。

(もっと読む)

分散制御用制御ソフトウェアおよび電子制御装置

【課題】

共有記憶領域を介したデータ授受による差異を吸収することで、複数演算装置を用いた制御システムの開発効率を向上することができる制御ソフトウェアを提供する。

【解決手段】

ネットワーク通信を行うソフトウェア部品と同じインターフェースを有し、前記複数演算装置が共有する記憶領域のデータの読み書きを行う処理ソフトウェアを部品化することで、共有記憶領域によるデータの授受を通信物理層のひとつとして扱い、制御システムを構築する。

(もっと読む)

プロセッサ

【課題】簡潔な構成で、処理能力の大幅な低下を招くことなく、他のプロセッサの動作や割り込み処理に対するアトミック性を確保する。

【解決手段】アドレス格納部131はアトミックオペレーションでアクセスされるメインメモリ3のアドレスを格納する。データ格納部132にはメインメモリ3から読み込まれたデータやCPU100によるアトミックオペレーションの処理結果のデータを格納する。割り込み検出フラグ134は割り込み復帰命令が実行されたときにセットされる。メモリアクセス制御部133は、アトミックオペレーションが終了するときに、割り込み検出フラグ134等に応じて判定回路139から出力されるアトミック性保証信号に基づき、処理結果データのメインメモリ3への書き込みを停止する。

(もっと読む)

1 - 3 / 3

[ Back to top ]