Fターム[5B045FF00]の内容

マルチプロセッサ (2,696) | 割込処理 (54)

Fターム[5B045FF00]の下位に属するFターム

Fターム[5B045FF00]に分類される特許

1 - 3 / 3

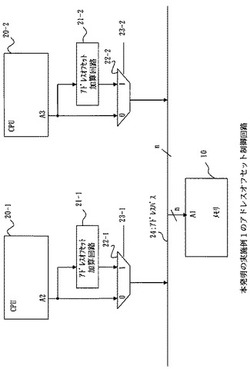

アドレスオフセット制御回路

【課題】あるプロセッサが記憶したデータを他のプロセッサが破壊してしまう可能性があり、その原因となっているソフトウェア(プログラム)の不具合を特定するのに時間が掛かってしまう。

【解決手段】アドレスオフセット制御回路は、複数のアドレスオフセット加算回路21−1,21−2と、複数の選択回路22−1,22−2とを有している。アドレスオフセット加算回路21−1,21−2は、メモリ10に対するアクセスをそれぞれ行うプロセッサ(例えば、CPU)20−1,20−2からそれぞれ出力されるアドレスに、所定のオフセット値をそれぞれ加算して加算結果をそれぞれ出力する。すると、選択回路22−1,22−2は、各アドレスオフセット加算回路21−1,21−2の加算結果と各CPU20−1,20−2から出力されるアドレスとをそれぞれ選択してメモリ10に与える。

(もっと読む)

少なくとも2つの実施ユニットを有する計算機において切り替える装置および方法

少なくとも2つの実施ユニットを有する計算機システムにおいて切り替える装置および方法であって、その場合に切替え手段が設けられており、その切替え手段は、少なくとも2つの駆動モードの間で切り替えるように形成されており、その場合に第1の駆動モードが比較モードに、第2の駆動モードがパフォーマンスモードに相当する、この装置および方法は、各実施ユニットに、プログラミング可能なインターラプトコントローラが対応づけられており、かつメモリ素子が設けられており、そのメモリ素子内に、これらインターラプトコントローラの少なくとも1つのもののコンフィグレーションの少なくとも一部を記述する情報が格納されていることを、特徴としている。  (もっと読む)

(もっと読む)

少なくとも2つの実施ユニットを有する計算機システムにおける切替え方法および装置

少なくとも2つの実施ユニットを有する計算機システムにおける切替え方法および装置であって、その場合に切替え手段が設けられており、その切替え手段は、これら実施ユニットが少なくとも2つの駆動モードの間で切り替るように形成されており、その場合に第1の駆動モードは比較モードに相当し、第2の駆動モードはパフォーマンスモードに相当する、前記方法および装置は、インターラプトコントローラが設けられており、さらに少なくとも3つのメモリ領域が設けられており、その場合にメモリ領域へのアクセスが、少なくとも1つの第1の実施ユニットに第1のメモリ領域が対応づけられ、少なくとも1つの第2の実施ユニットには第2のメモリ領域が対応づけられ、少なくとも1つの第3のメモリ領域が少なくとも2つの実施ユニットに対応づけることができるように、行われることを特徴としている。  (もっと読む)

(もっと読む)

1 - 3 / 3

[ Back to top ]