Fターム[5B046BA05]の内容

CAD (21,103) | 設計対象(段階、工程) (4,232) | 実装設計、レイアウト設計 (2,049) | 割付、配置、ネスティング (289)

Fターム[5B046BA05]に分類される特許

1 - 20 / 289

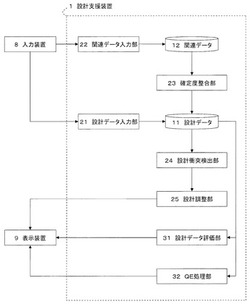

設計支援装置および設計支援方法

【課題】配置を段階的に確定していくレイアウト設計において、設計制約を満たすような配置の意志決定を効率的に支援すること。

【解決手段】設計支援装置1は、設計データ11を構成する各機器に対して、レイアウトデータと確定度とを対応づけて記憶手段に格納する設計データ入力部21と、設計データ11の各機器について、機器間でのレイアウトデータの衝突を検出する設計衝突検出部24と、設計衝突検出部24により衝突が検出された機器群について、対応づけられている確定度が低い順に機器を選択し、その選択した機器を他の機器を回避するように移動させることにより、設計データ11のレイアウトデータを変更する設計調整部25と、を有する。

(もっと読む)

プリント基板設計支援プログラム、プリント基板設計支援方法及びプリント基板設計支援装置

【課題】プリント基板上に所定の条件を満たすようにビアを自動で配置することを目的とする。

【解決手段】複数の導電層を有するプリント基板のグラウンドとして利用できる導電領域を特定するグラウンド導電領域特定ステップと、グラウンド導電領域特定ステップにより特定された導電領域が2次元的に重複している重複導電領域を抽出する抽出ステップと、抽出ステップにより抽出された重複導電領域内に複数の導電層のうちの少なくとも2層を電気的に接続する層間接続部材を所定の距離以内の間隔で配置する第1の配置ステップとをコンピュータに実行させるためのプリント基板設計支援プログラムであって、第1の配置ステップは、抽出ステップにより抽出された重複導電領域をブロック分割するブロック分割ステップと、ブロック分割ステップにより分割されたブロック内に層間接続部材を配置する第2の配置ステップと、を有する。

(もっと読む)

半導体設計装置、半導体設計方法及びプログラム

【課題】信号の重要度を考慮に入れたセルの自動配置を行うアルゴリズムは存在しない。従って、重要配線が不必要に長くなる場合がある。重要配線が長くなると、重要配線を伝達する信号を劣化させる原因となり得る。そのため、信号の重要度を考慮に入れたセルの自動配置を行うことで、重要度の高い信号の品質を維持する半導体装置を設計できる半導体設計装置、が望まれる。

【解決手段】半導体設計装置は、半導体装置に含まれる複数のセルを接続する複数の信号配線から、伝達する信号が重要であることを示す重要配線情報が付された重要配線と、複数の信号配線のそれぞれに接続されているセルの数を示すセル接続数と、を抽出する配線情報抽出部と、配線情報抽出部が抽出した重要配線及びセル接続数に応じて、複数のセルの配置を決定するセル自動配置部と、を備えている。

(もっと読む)

半導体装置の自動配置配線プログラム、自動配置配線装置及び自動配置配線方法

【課題】従来の方法では、アナログ・デジタル混載LSIのレイアウトの処理時間及び面積効率が悪化する問題があった。

【解決手段】本発明の自動配置配線プログラムは、回路設計情報からモジュールを抽出する第1処理(S10)と、モジュールに含まれる回路の属性を示すモジュール属性を設定する第2処理(S11)と、面積値を一定として縦横の寸法が異なる複数のモジュール形状候補を生成する第3処理(S12)と、上位モジュールの形状に適合するモジュール形状候補に対して回路素子を配置してレイアウトパターンを生成する第4処理(S13)と、を有し、第3処理(S13)では、第1回路属性のモジュールに対しては、行の高さ又は列の幅を縦横の寸法の変化単位とする複数のモジュール形状候補を生成し、第2回路属性のモジュールに対しては、縦横の寸法が連続的に変化する複数のモジュール形状候補を生成する。

(もっと読む)

レイアウトパタン生成装置及びプログラム

【課題】デザインルールチェックの妥当性を正しく確認するために用いるレイアウトパタンを簡易に生成することができるようにする。

【解決手段】図形入力部24によって、半導体装置のレイアウトパタンについて予め定められた作図基準を満足するように生成されたOKパタンの入力を受け付ける。基準位置指定部28によって、OKパタンに対して、作図基準を満足している部分を基準箇所として指定する入力を受け付ける。検証パタン生成部34によって、OKパタンの基準箇所に対して、所定の変更を加えることにより、作図基準を満足しないNGパタンを生成する。

(もっと読む)

半導体集積回路のレイアウト設計装置、方法、及びプログラム

【課題】アナログ回路において最適な配線効率を実現するためのレイアウト設計を可能にする。

【解決手段】機能ブロックを構成する素子をその種類毎にグループ化する。機能ブロック内の素子の配置を各素子の接続関係に基づいて決定する。この時、グループを構成する素子の分割数を考慮してもよい。機能ブロックの配置順序を面積又は幅が大きい順に配置されるように決定する。また、配置順序はユーザの指定により調整できることが好ましい。配置順序と回路全体の接続情報とに基づいて各機能ブロックの配置位置を決定する。

(もっと読む)

フロアプラン作成情報生成方法、フロアプラン作成情報生成プログラム、フロアプラン作成情報生成装置、フロアプラン最適化方法、フロアプラン最適化プログラム及びフロアプラン最適化装置。

【課題】フロアプラン設計におけるイタレーションを防ぎ、設計期間を短縮する。

【解決手段】複数の回路モジュールの接続情報を含むネットリストと、前記複数の回路モジュールにグループを設定するためのグループ設定情報と、を記憶部に記憶し、ネットリスト及びグループ設定情報に基づき、複数の回路モジュールにグループを設定し(S21)、設定されたグループ間におけるタイミング制約を満たす距離を算出し(S23)、算出されたグループ間の距離を含み、フロアプランを作成するためのフロアプラン作成情報を生成する(S25)。

(もっと読む)

配置配線装置

【課題】効率的にIR−Dropを防止することが可能な配置配線装置を提供すること。

【解決手段】複数のセルを配置した後、セル間の隙間が所定の大きさよりも小さい場合にはセル間の隙間が所定の大きさ以上となるようにセルの配置を変更する(S17)。そして、配置された複数のセルの間に容量セルを挿入し(S15)、配置された複数のセルの配線を行なう(S14,S16)。したがって、効率的にIR−Dropを防止することが可能となる。

(もっと読む)

LSI設計方法,設計プログラムおよび設計装置

【課題】従来のLSI設計フローではクロックの遅延やスキューが無いことを前提とするため,クリティカルパスにてタイミングが仕様を満たさないことがSTA後に判明する。

【解決手段】ハードウェア記述ファイルと制約条件ファイルとから第1のクロックと第2のクロックのそれぞれのクロックツリーによる想定遅延値をそれぞれ生成し,第1のクロックと第2のクロックの想定遅延値をもとにしてクリティカルパスをデータベースへ登録するデータベース構築工程と,ハードウェア記述ファイルと制約条件ファイルについて論理合成を行うとともに,クリティカルパスをそれ以外のパスよりも優先して最適化し,ネットリストを生成する論理合成工程とを有するLSI設計方法。

(もっと読む)

複数部品からなるプレス成形品の最適分割位置決定方法及び装置

【課題】本発明は薄板をプレス成形して形成された複数の部品を接合して構成される製品における、該製品における最適な分割位置を決定する方法及び装置得る。

【解決手段】本発明の最適分割位置決定方法1は、薄板をプレス成形して形成された複数の部品を接合して構成される製品における、該製品における最適な分割位置を決定する方法であって、製品CAD情報の分割可能領域内において分割位置候補を複数設定し、分割位置候補のひとつで製品を分割した場合の各部品の展開形状を計算し、該展開形状に必要な余裕代を設ける余裕代展開形状を計算し、各余裕代展開形状を含む最小の板材寸法を計算し、該板材寸法等から全部品の合計材料費を計算し、他の分割位置候補についても同様に合計材料費を計算し、材料費が最小になるような分割位置候補を最適分割位置として決定することを特徴とするものである。

(もっと読む)

部材割付システム

【課題】k種類の長方形の原材料から、長方形のm個の製品を切り出し、その歩留を最大にする。既存の線材を対象にした探索法を面材に適用する。

【解決手段】予め求めた初期実行可能解の目的関数の値を最大値とし、原材料の使用枚数について緩和された制約条件式0≦xi≦1を設定してシンプレックス演算処理をする。その結果得られた目的関数の値を最小値として、その範囲の目的関数の値をとる原材料の使用枚数の組合せを列挙する。その後、原材料の使用枚数の組合せを固定した制約条件でシンプレックス演算処理を実行し、得られた複数の非整数解を所定の評価式で評価する。初期実行可能解を面材固有のFF法により求め、探索の結果をFF法に当てはめて、板取りと切断順を出力する。

(もっと読む)

クロックツリー生成方法、クロックツリー生成プログラム、記録媒体、およびクロックツリー生成装置

【課題】外部電源電圧が変動した場合でも、安定に動作する半導体装置を実現することが可能なクロックツリー生成方法を提供する。

【解決手段】プログラム5のCTS部8は、電源領域Aから電源領域Bにクロック信号CLK1,CLK2を伝達する経路L1,L2を設け、電源領域A内の経路L1,L2にそれぞれアンカーバッファB1,B2を配置し、遅延回路D1,D2を電源領域B内の経路L1,L2にそれぞれ配置し、遅延回路D3,D4をアンカーバッファB1,B2の入力ノード側の経路L1,L2にそれぞれ配置する。したがって、外部電源電圧VDD1,VDD2が変動した場合でも、クロック信号CLK1,CLK2の遅延時間は同じになる。

(もっと読む)

プリント配線板の設計支援システム、プリント配線板の未実装部品に対するノイズ対策方法およびプログラム

【課題】プリント配線板の未実装部品の接続箇所としての端子の中から、ノイズの対策部品の取り付けが必要とされる端子を人手を介さずに判別したり表示できるプリント配線板の設計支援システム、プリント配線板の未実装部品に対するノイズ対策方法およびプログラムを得ること。

【解決手段】未実装部品用端子特定手段13は、互いに関連する製品のいずれかに少なくとも使用する実装部品のすべてを1枚のプリント配線板に実装可能に設計した共通化配線パターンにそのうちの1つの製品の部品を配置したときの未実装部品の端子を特定する。対策部品要否判別手段14はこれらの端子がノイズ対策が必要かを判別して対策必要端子記憶手段15がその結果を記憶する。

(もっと読む)

半導体集積回路の設計方法、設計プログラム、及び設計支援装置

【課題】半導体集積回路の設計TATを短縮する。

【解決手段】本発明による半導体集積回路の設計方法は、コンピュータ装置10によって実行される半導体集積回路の設計方法であって、論理セル500と配線セル400をチップ上に配置するステップと、論理セル500内のゲート505に対するアンテナルール122を配線セル400の第1アンテナ用ライブラリ101に追加することで、第1アンテナ用ライブラリ101を第2アンテナ用ライブラリ201に変更するステップと、配線セル400と他の論理セル510を第1配線550で接続するステップと、第2アンテナ用ライブラリ201に規定されたアンテナルール122に従い、ゲート505の面積に対する前記第1配線550の面積の比を検証する第1検証ステップとを具備する。

(もっと読む)

半導体集積回路及びそのレイアウト方法

【課題】短時間でレイアウト構成を行うことができる半導体集積回路及びそのレイアウト方法を提供すること。

【解決手段】本発明の一態様である半導体集積回路100は、出力回路11、信号分岐用セル12、マスタ回路13及びチェッカ回路14を有する。出力回路11は、出力信号を出力する。信号分岐用セル12は、出力信号を分岐した第1及び第2の出力信号を出力する。第1及び第2の出力信号に分岐される前の出力信号が伝搬する共通線部である第1の配線16の長さは、制約値X以下である。マスタ回路13は、第1の出力信号を受ける。チェッカ回路14は、第2の出力信号を受け、マスタ回路13と冗長構成回路を構成する。

(もっと読む)

布線設計方法、布線シミュレーション装置及びプログラム

【課題】ワイヤーハーネスの製造工程を正確に模擬することができる布線設計方法を提供する。

【解決手段】布線シミュレーション装置1の制御部11は、初期設計情報を取得すると(ステップ101)、取得された初期設計情報を制約条件とする解析モデルを用いて、所定の処理を複数回実行する収束計算を行うことによって、電線の布線作業を模擬する(ステップ102)。また、制御部11は、ステップ102における模擬結果に基づいて、所定の処理を複数回実行する収束計算を行うことによって、電線のパッキング作業を模擬する(ステップ103)。そして、布線シミュレーション装置1の制御部11は、ステップ102、103における模擬結果を表示部16等に出力する(ステップ104)。

(もっと読む)

設計支援システム

【課題】専門知識を有しないユーザであっても、スレーブ装置の接続順序や接続先のポートを意識したネットワークシステムの設計を容易に行うことができる設計支援システムを提供する。

【解決手段】スレーブ装置の固有情報が記述されたスレーブ情報データを記憶する記憶手段と、スレーブ情報データからスレーブ装置に備わるポートの情報を取得する取得手段と、ポートの情報に基づきスレーブ装置に備わるポートを表すGUI部品であるポート部品を生成し、スレーブ情報データに基づきスレーブ装置を表すGUI部品であるデバイス部品を生成し、デバイス部品とポート部品を含んで構成される設計中のネットワークシステムのトポロジを表示するトポロジ表示画面を含む設計支援用のGUIを生成する生成手段と、を有する。

(もっと読む)

設計支援システム

【課題】専門知識を有しないユーザであってもポートの接続インターフェースの種類を意識したネットワークシステムの設計を容易に行うことができる設計支援システムを提供する。

【解決手段】スレーブ装置の固有情報が記述されたスレーブ情報データを記憶する記憶手段と、スレーブ情報データからスレーブ装置に備わるポートの接続インターフェースの情報を取得する取得手段と、スレーブ情報データに基づきスレーブ装置を表すGUI部品であるデバイス部品を生成し、スレーブ装置に備わるポート同士の接続をポートの接続インターフェースの種類に応じて異なる態様で表すGUI部品であるライン部品を生成し、デバイス部品をライン部品で接続することにより構成される設計中のネットワークシステムのトポロジを表示するトポロジ表示画面を含む設計支援用のGUIを生成する生成手段と、を有する。

(もっと読む)

半導体装置および半導体集積回路の設計方法

【課題】本発明は、半導体集積回路を備えた半導体装置および半導体集積回路の設計方法に関し、IO領域を有効に利用しつつパッケージの高さ寸法の増大を有効に抑えた接続を可能とする。

【解決手段】半導体基板の表面の第1の辺に沿って、第1のIOセルと、第2のIOセルとを交互に配置したIO領域を有し、第1のIOセルは、第1の辺から所定の距離の位置に配置されたボンディングパッドを有し、第2のIOセルは、第1のIOセルのボンディングパッドより第1の辺から遠い位置にボンディングパッドを有し、かつ、第1のIOセルの少なくとも1つは、第1の辺から所定の距離の位置に配置された第1のボンディングパッドに加えて、第2のIOセルのボンディングパッドより第1の辺から遠い位置に、第2のボンディングパッドを有する第3のIOセルに置きかえられている。

(もっと読む)

半導体集積回路の設計方法

【課題】設計フローの負荷を増大させることなく、それぞれの回路モジュールに必要十分な容量セルを、それぞれの回路モジュールに近接配置することができる半導体集積回路の設計方法を提供する。

【解決手段】本発明は、それぞれが複数の論理セルを含む複数の回路モジュールからなる半導体集積回路の設計方法であって、複数の回路モジュールのそれぞれの、複数の論理セルおよび複数の論理セルの端子間の接続の情報を記述するネットリストに、複数の論理セルに電源を供給する電源配線間に接続されるセルであり、複数の論理セルのいずれとも独立で、かつ、複数の論理セルの端子と接続される端子を持たない容量セルの記述を追加し、複数の論理セルおよび複数の容量セルのレイアウトデータが格納されたセルライブラリを備えた設計支援システムを利用して、回路モジュールのそれぞれに対応する、複数の論理セルおよび容量セルを配置する配置領域を設定し、複数の論理セルおよび容量セルを対応する配置領域内に配置する工程を含む。

(もっと読む)

1 - 20 / 289

[ Back to top ]