Fターム[5B046CA05]の内容

Fターム[5B046CA05]に分類される特許

1 - 4 / 4

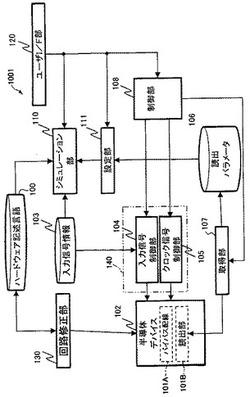

回路検証装置および回路検証方法

【課題】半導体デバイスのシミュレーションに必要なパラメータを読み出すための構成を簡素化する。

【解決手段】ハードウェア記述言語に基づく論理回路が形成された半導体デバイス(102)のエミュレーションのための信号をデバイスへ入力する手段(140)と、論理回路に対応したハードウェア記述言語によりシミュレーションを実行する手段(110)と、シミュレーションに係るパラメータをデバイスから取得する手段(107)と、取得したパラメータをシミュレーションに適用する手段(111)と、パラメータ取得前に論理回路を修正する手段(130)とを備える。論理回路を修正するとき、その論理回路にてパラメータを記憶する記憶素子がリング型のシフトレジスタとして動作するためのバイパス配線(101A)と、バイパス配線を介して各記憶素子のパラメータを読み出す読出部(101B)とを付加する。

(もっと読む)

半導体回路及び設計装置

【課題】処理装置がハードウェアアクセラレータを高速に起動させることができる半導体回路を提供することを課題とする。

【解決手段】データを記憶するためのメモリ(214)と、プログラムを実行し、プログラムの実行中のアドレスを示すプログラムカウンタの値がハードウェアアクセラレータ開始アドレスになると、プログラムの関数の引数のデータをメモリのスタックポインタのアドレスに書き込み、スタックポインタのアドレスを出力する処理装置(212)と、処理装置のプログラムカウンタの値がハードウェアアクセラレータ開始アドレスになると、処理装置からスタックポインタのアドレスを入力し、スタックポインタのアドレスを基にメモリから関数の引数のデータを読み出し、引数のデータを用いてハードウェア化した関数の処理を行うハードウェアアクセラレータ(213)とを有する半導体回路が提供される。

(もっと読む)

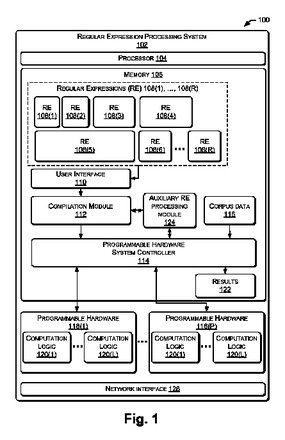

仮想化超並列プログラマブルハードウェアによる正規表現の検索

プログラマブルハードウェアデバイスでの実行に適切な論理および状態情報は、コーパスに対して正規表現を評価するように、タスクから生成することができる。プログラマブルハードウェアデバイスでの論理および状態情報のハードウェア容量の要件を推定することができる。推定されると、複数のタスクから生成された複数の論理および状態情報は、各セットの論理および状態情報がプログラマブルハードウェアデバイスのハードウェア容量内に収まるように、セットに配分することができる。各セット内のタスクは、プログラマブルハードウェアデバイスで並列に実行するように構成することができる。次いで、セットは順次に実行されてもよく、リソースの仮想化が可能になる。  (もっと読む)

(もっと読む)

複合データ処理装置

【課題】 刺繍の良さと印刷の良さを両立させることで風合い感や立体感を十分に表現でき、しかも刺繍処理に要する処理時間の短縮化を図るようにすること。

【解決手段】 予め選択された刺繍データが読み込まれ(S11)、その刺繍データについて解析処理され(S12)、特殊な縫目であって、しかも複数の糸色の糸で刺繍される混色領域が存在する場合には(S14:Yes )、その混色領域に印刷する印刷データが色別刺繍領域毎に作成され(S15)、刺繍データの糸色情報が、例えば「白色」等に単一化される(S16)。そこで、刺繍枠にセットされた布地に対して、このように単一化された刺繍データに基づいて刺繍処理された後、作成された印刷データに基づいてインクジェットプリンタにより印刷される。

(もっと読む)

1 - 4 / 4

[ Back to top ]