Fターム[5B046JA00]の内容

CAD (21,103) | 検証、解析 (4,829)

Fターム[5B046JA00]の下位に属するFターム

Fターム[5B046JA00]に分類される特許

1 - 6 / 6

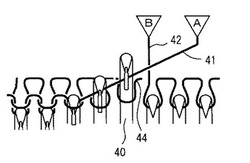

ニットデザイン装置

【構成】

・ 横編機のキャリッジの進行方向前方のカムシステムでインターシャ柄の境界に対して進行方向後方の第1の編地を編成し、進行方向後方のカムシステムで境界に対して進行方向前方の第2の編地を編成するコースで、

・ 第1の編地の端の編目で、直前に編成したコースに比べ、進行方向前方へ突出する編目を、ニットデザイン装置は第1の編目として編成データから検出する。第1の編目を検出すると、第1の編目に対して1コース下に位置する、第2の編地の第2の編目をミスに置き換える。

【効果】

インターシャ柄の境界部での編糸の引っ掛けを、編成効率を低下させずに防止できる。

(もっと読む)

レイアウト修正・ライブラリセル置換モジュール及び半導体装置設計用EDAツール

【課題】効率的に検出率を向上する方法及び未検出箇所が不良になる確率を低減させる手法により、多層配線層の検査工程を含む半導体製品の製造技術において、検査の迅速性を損なうことなく、半導体製品の製造歩留まりを向上させる技術を提供する。

【解決手段】不良の検出が困難な未検出領域について、パターン等の変更を行い検出率、致命率の改善を行う。例えば、検出が困難な未検出領域についてパターンを追加することで検出可能とする、パターンの間隔を広げることで不良率を低下させることなどが考えられる。

(もっと読む)

シミュレーション装置、プログラム、記憶媒体、及び方法

【課題】 本発明の課題は、ソフトウェアとハードウェアの協調シミュレーションにおいて、ソフトウェアとハードウェア間の同期回数を削減することを目的とする。

【解決手段】 上記課題は、組込みソフトウェアを検証するための論理的な単体又は複数のハードウェアモデルを駆動するハードウェアシミュレータと、前記組込みソフトウェアを実行するCPUの動作を模した前記単体又は複数のハードウェアモデルの一つであり、前記ハードウェアシミュレータとの命令毎の同期を省略して該組込みソフトウェアを動作させるCPUモデルとを有することを特徴とするシミュレーション装置により達成される。

(もっと読む)

パワープラント機械の過速度保護システムを試験する方法およびシステム

【課題】トリップの機会を低減させる過速度保護システムを試験する方法を提供すること。

【解決手段】本発明の実施形態は、少なくとも1つのシャフト(137)を備えるパワープラント機械(105、145)の過速度保護システムを自動的に試験する(200)という技術的な効果を有する。本発明の一実施形態では、パワープラント機械(105、145)が無負荷定格速度(FSNL)から減速している間に過速度保護システムを自動的に試験することができる。本発明の別の実施形態では、パワープラント機械がFSNLへ加速している間にパワープラント機械(105、145)の過速度保護システムを自動的に試験することができる。

(もっと読む)

検証装置、検証方法、及びプログラム

【課題】検証済みの基準回路と被検証回路とに修正が加えられた場合に、回路全体を検証しつつ、設計時間の短縮化及び効率化を図り得る、検証装置、検証方法、及びプログラムを提供する。

【解決手段】検証装置10は、基準回路での論理変更によって変更された信号に関する情報に基づいて、論理変更前後の基準回路における論理変更によって信号の入力値が変化するポイントを抽出する、基準回路側ポイント抽出部20と、被検証回路での論理変更によって変更された信号に関する情報に基づいて、論理変更前後の被検証回路における論理変更によって信号の入力値が変化するポイントを抽出する、被検証回路側ポイント抽出部30と、基準回路側ポイント抽出部20及び被検証回路側ポイント抽出部30が抽出したポイントを用いて、検証スクリプト41を生成する検証スクリプト生成部40とを備えている。

(もっと読む)

レイアウト設計支援装置、コンピュータ読み取り可能な記録媒体

【課題】 レイアウトパターンに対する補正結果と、この補正の検証結果とをレイアウトパターン設計者自身が設計中に逐次確認できるレイアウト設計支援装置、コンピュータ読み取り可能な記録媒体を提供する。

【解決手段】 縮小投影露光に使われるレチクルパターンを作成する設計支援装置であって、レイアウトパターンを作成するためのレイアウトエディタ1と、レイアウトパターンに対して補正および検証を行うためのOPC補正・検証装置2と、レイアウトパターン、補正および検証のデータを格納するためのデータベース3などから構成され、レイアウトエディタ1は、設計者がユーザインタフェースを通して操作することが可能とされ、レイアウトパターンを作成するための機能の他に、OPC補正・検証装置2の補正および検証を行うための機能を支援するために、画面上のメニューに補正・検証コマンドが追加されている。

(もっと読む)

1 - 6 / 6

[ Back to top ]